前回、宿題をこなすためにデスクリートのNMOSトランジスタを直列接続しました。結果はなんだかな~だったですが、作った「回路」は無駄にはしませんよ。チョイ変で、NAND型マスクROMを構成し実験してみました。ディスクリートのNMOSトランジスタたった8個で構成しているので、本物には程遠いナンチャッテ回路。でも原理は同じ。

さて、その回路を説明するために回路図を掲げようと思うのですが、今回から回路図エントリに使用する回路図エディタを変更しました。

- 今まで:LTspiceの回路図エディタ

- 「これからの」古代MOS回路:水魚堂の回路図エディタ

であります。今後も回路シミュレーション時にはLTspiceを使用させていただこうと考えているのですが、シミュレーションも不要なときの古代MOS回路をさくっと描く「だけ」にはちょっと厳めしすぎる。規模の大きいPCB設計用の開発環境はタダでさえ圧迫感があるこのPCのディスクストレージを食い過ぎる。そこで、

- 軽い

- 簡単にライブラリが描ける

- 日本語マニュアルなので楽

という3点を考えて水魚堂さんの回路図エディタを使用させていただくことにいたしました。とはいえネットリストもBOMも生成できる立派なCADであります。Bsch3V回路図エディタは純正のまま、古代MOS回路用の小さなライブラリを追加して使わせていただいております。

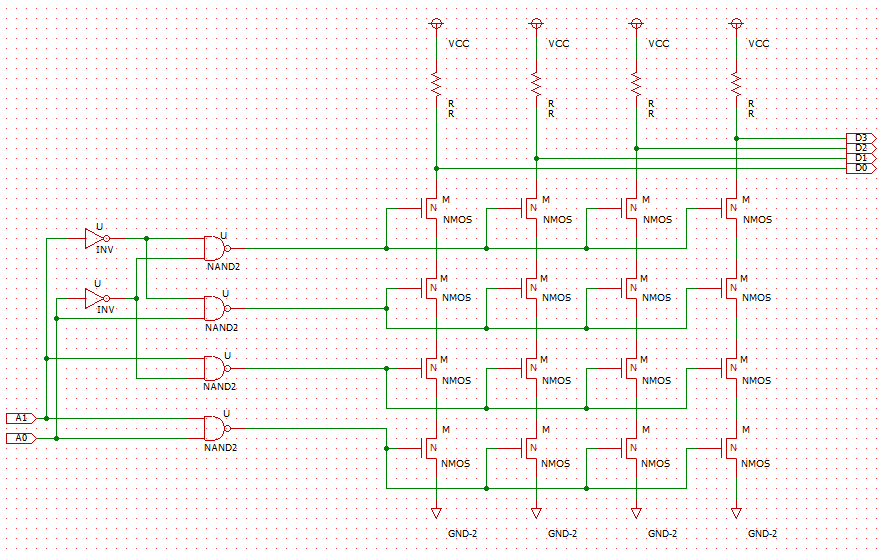

早速、NAND型マスクROM回路(もどき)を描いたものがこちら。

構成は、4ビット幅、4ワード深さの4×4=16ビットのROMであります。左側のインバータとNANDゲートがA0とA1という「アドレス」2ビットのアドレスデコーダ、右側のNMOSトランジスタの「アレイ」がROM本体です。各MOSトランジスタのゲートに共通な左右に通過する信号がワード線、直列に接続したNMOSトランジスタから出力される線がD0からD3のビット線となります。

構成は、4ビット幅、4ワード深さの4×4=16ビットのROMであります。左側のインバータとNANDゲートがA0とA1という「アドレス」2ビットのアドレスデコーダ、右側のNMOSトランジスタの「アレイ」がROM本体です。各MOSトランジスタのゲートに共通な左右に通過する信号がワード線、直列に接続したNMOSトランジスタから出力される線がD0からD3のビット線となります。

なお、NMOS(もどき)回路なので、各ビット線は抵抗で上に吊り上げる方式、また、各NMOSのボディ(あるいはサブストレート、バックバイアス)は明示していません。LSI内部であればGND接続、今回のようなディスクリート使用であれば各トランジスタのソース接続となります。

見れば分かる簡単な回路ですが、一応説明させていただきます。

- 2ビットのアドレスに応じてワード線のどれか1本がLOW(他はHIGH)となる

- LOWになった線につながっているトランジスタが存在すればビット線はHIGH、不在(短絡)しておればビット線はLOWとなる

まあ、お手軽。実際には、トランジスタを直列接続していると、前回の実験でも明らかなようにビット線の駆動力が落ちていくので、こんな単純に出力を取り出すことなどできず、センスアンプとか「アナログ的な」回路をビシビシ使うことになります。また、無限に直列接続などできないので、いろいろ階層化したりと工夫することになるのですが。しかし、これでも

NAND型ROM

には違いありませぬ。(Araha氏がなんちゃってNAND型ROM<もどき>について解説?感想書いてくれました。それはこちら)さて、今回は「マスク」ROM、最近あまり見ない、工場で製造時にプログラムするタイプのROMを想定しています。先ほど「トランジスタが存在すれば」などと書きましたが、実際にROMの中のビットアレイの中でトランジスタの在、不在みたいなことをどうやってプログラムしているのか。上の方か下の方か、大きく2通りの方法があります。

- トランジスタをインプラントで潰す

- メタル配線でトラジスタを無視?する

インプラントといって歯じゃありませんよ。不純物イオンをトランジスタに打ち込むのです。普段からトランジスタのスレッショルド電圧などを調整するためにイオンを打ち込んでいるのですが、不純物を打ち込み過ぎると、半導体としての性質が消え、導体になってしまいます。これをつかって、1をプログラムするトランジスタを濃いめの一発で潰してしまう。「ドーピング」の手口であります。

それに対して、2の方は配線でトランジスタを無効化すると。トランジスタは物理的には在るのですが、電気的には意味がなくなります。

1番目の方法の方が、面積の小さいROMが作れるので昔はこちらが主流でしたが最近では廃れています。なぜかというと、イオン打ち込みは半導体プロセスでも前半の方で行わないとならないので、お客のプログラムを受領してから出荷するまで数か月とか時間が必要になるのです。2番目の配線層は工程の最後の方でやれば良いので、予め未プログラムの仕掛ウエファー在庫を持っておれば、比較的短時間、数週くらいで出荷できる、というわけです。まあ、どちらにしても、電気的にプログラムできるFLASHセルに比べるとリードタイムが長いのでマスクROMは昔に比べると激減です。

なお、顕微鏡で見ればプログラムビットが一目瞭然のメタルプログラミングにくらべて、イオン打ち込みは見ても分からないので秘匿性が高いです。しかしこのごろは、暗号化が進んでいるので、秘匿したい用途ならばメタルでも暗号かければOKでしょ。

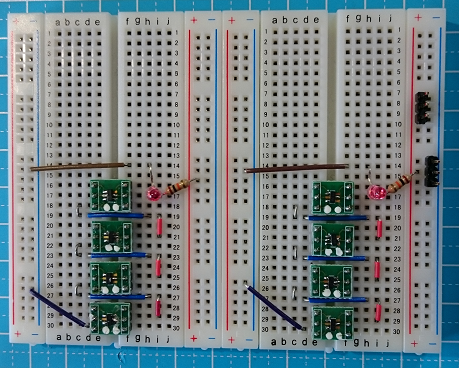

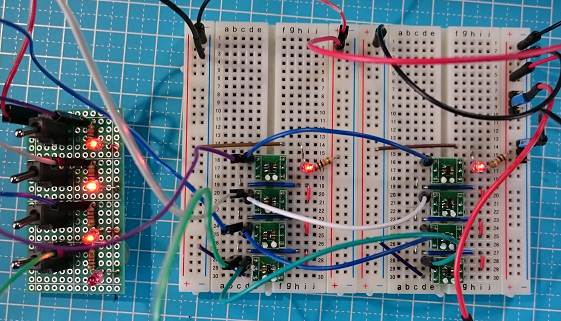

長々と説明していたので、実際に、ディスクリートのNMOSトランジスタのBOB基板をブレッドボードに刺して作った回路を動かしてみます。基本的な配線は前回の実験と同じですが、直列接続は4個にしてそれを2列ならべています。ぶっちゃけ、本日時点でNMOSのBOB基板は8個しか「製造」できていないために、2ビットx4ワード構成です。上記の回路図の半分。また、本来ならアドレスデコーダ部分もディスクリートのMOSトランジスタで作ったゲードで動かしたいところなのですが、全然間に合っていないので、とりあえずスイッチで作ったテスト回路で模擬です。

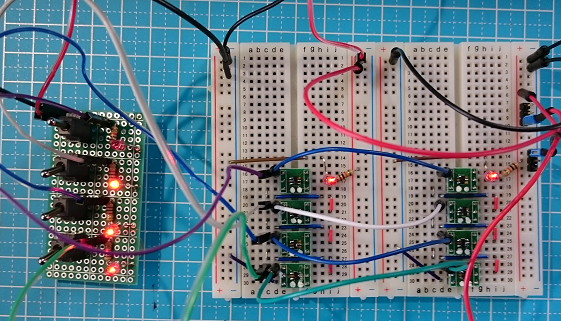

最初は、A0=0, A1=0のつもりで、メタルプログラミング無(LOW出力、写真ではLOW出力するとLEDが点灯)

次は、A0=0, A1=0のつもりで、ビット線0側をメタルプログラミング。黄色のジャンパがメタルプログラミングのつもり。

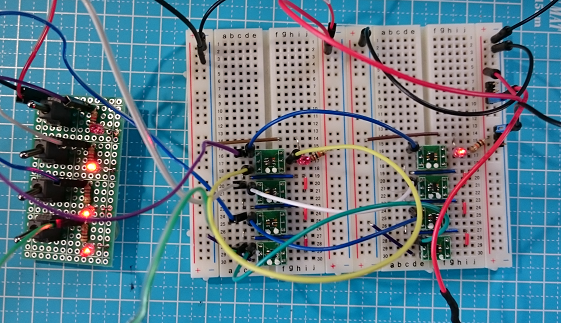

一応、違うワードでもテスト。A0=1, A1=1のつもりで、メタルプログラミング無。

プログラムしていないと、両ビット線ともLOW(両方のLED点灯)

プログラムしていないと、両ビット線ともLOW(両方のLED点灯)

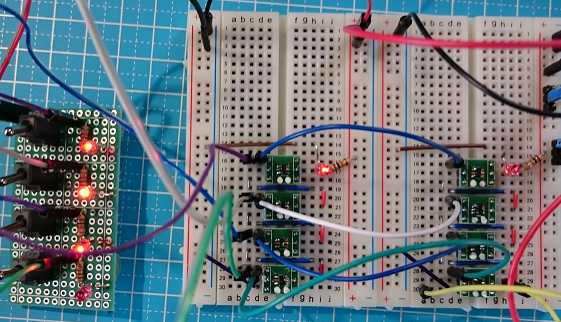

同じワードのこんどはビット1の線をメタルプログラム(黄色のジャンパ)すれば、

一応、ROMとして動作。

なんちゃってNAND型マスクROM(もどき)、完成。