前回は、ROMのビットパターンを外部ファイルから読み取ってシミュレーションに使用してみました。ファイルからデータを入力できるのであれば、コマンドラインからちょいとテスト値などを読み込ませて使用することもしたいです。ついでにモジュール・ファイルの置き場所も所定の場所にまとめたいです。今回はiverilog使うときの小ネタ

今回は「ゲートレベル」の「インタラクティブな」シミュレータ Logisim はお休みで、Icarus Verilog の回であります。

Icarus Verilogのドキュメンテーションの在り処

フリーのVerilogの定番、Icarus Verilogを使わせていただいております。そのホームページは以下に。

上記ホームページに若干の不満があるとすれば、ドキュメンテーションらしいドキュメンテーションが置かれていないという点であります。そこを補ってくれるのが、以下の2つではないかと思います。

上の gEDA project は、GPLライセンスのEDAツール(当然オープンソースでフリー)を推進しているプロジェクトで、回路図エディタやPCB設計ツールなど一通りそろっているなかで、Icarus VerilogはVerilog担当みたいな位置づけで「協力関係」にあるみたいです。ツールに関するドキュメントや、各種リンクも置かれており、Icarus Verilogに関する情報も結構充実しております。知らんけど。

一方、下のリンクは Icarus verilogのGithub です。当然ソースが置かれています。sphinx形式のドキュメントも置かれています。まあ、こちらの方がプライマリな情報ソースですかい。

モジュール・ファイルの取り込みと置き場所

Verilogの場合、1モジュール1ファイルにせよ、と言われるわけです(守らなくてもダメということもないみたいです。)すると当然、モジュールの種類だけのファイルが必要になるので、どこかに整理して置いときたくなりますな。

Icarus Verilogの場合、コマンドラインオプションからして以下のどちらかの方法になるんじゃないかと思います。

-

- -ylibdir

- -Iincludedir

上の -y オプションはそれに引き続くlibdirというディレクトリにモジュール・ファイルを置いておくと、上位のモジュールで参照しているモジュールが見つからないときにはそこを探してくれる、というものであります。便利。今回は以下のようなコマンドラインで、早速使ってみました。

$ iverilog -o main.out -yF:\pgm2\iverilog\vlib main.v

下記が main.v のソースで、その中で参照している compU8というのが、libdirに置かれているモジュールです。Windows上でIcarus Verilogしているので、libdirの指定は上記のようにWindows式のパスです。

`timescale 1 us / 100 ns

module main;

reg [7:0] A, B;

wire GT, EQ, LT;

parameter STEP = 10;

compU8 dut(

A, B, GT, EQ, LT

);

initial begin

if (! $value$plusargs("B=%d", B)) begin

$display("ERROR: +B=0..255 needed.");

$finish;

end

$dumpfile("main.vcd");

$dumpvars(-1, dut);

$monitor("%d GT=%b, EQ=%b, LT=%b", $stime, GT, EQ, LT);

end

// testbench actions

initial begin

#0 A = 8'b00000001;

#STEP A = 8'b00000010;

#STEP A = 8'b00000100;

#STEP A = 8'b00001000;

#STEP A = 8'b00010000;

#STEP A = 8'b00100000;

#STEP A = 8'b01000000;

#STEP A = 8'b10000000;

#STEP A = 8'b00000000; B = 8'b00000000;

$finish;

end

endmodule //main

一方、-Iオプションに引き続く指定は、includeファイルのディレクトリの指定です。プリプロセッサ命令を使ってファイルをインクルードする時には便利ではあるものの、インクルードのためには明示的にモジュール・ファイル名を書かねばならないのでインクルードそのものは面倒です。こちらはパスすることにいたしました。

シミュレーション時に与えることができるコマンドライン・パラメータ

エラボレーション時(コンパイル時)に、iverilogに対して、-Dオプションを使ってマクロ文字列を与えることができるので、それを使えばコンパイル時に何かパラメータを切り替えて使うことが出来そうです。

しかし、一度シミュレーション用のオブジェクトを生成した後で、vvpコマンドでシミュレーションをかけるとき、「実行時」のパラメータを与えられれば、いちいちモデルをコンパイルしなおすことなくできるので嬉しいです。

それに使えるのが、以下のコマンドライン入力用のシステム関数です。

$value$plusargs

これはVerilogの標準的な機能だと思うので Icarus Verilogの機能というわけでないです。Icarus Verilogでの使用例などは以下のページで見つかります。

Simulation Using Icarus Verilog

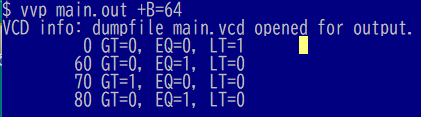

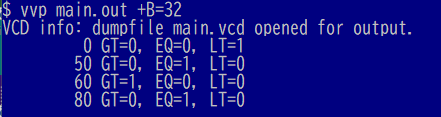

実際に、vvpに対しシミュレーション時に Bという変数に32という数値を代入させてシミュレーションしている様子が以下に。

フツーに動いてますで。当たり前か。