前回、地味な行列パレットからもっと地味な整数パレットに進出いたしました。実数、複素数中心のXcosですが無いと困るかも、ということで練習しました。今回は整数パレットの続きです。ぶちゃけ「ゲートレベル」の論理シミュレーション用って感じのブロックどもです。確かに論理シミュレーションもどき出来るけれどもイマイチやな~。

※「ブロックを積みながら」投稿順 index はこちら

※動作確認にはWindows 11のパソコン(64bit)上にインストールしたScilabの以下バージョンを使用しています。

Scilab 2024.0.0

今回練習のブロックども

今回は組み合わせロジック、フリップフロップ、シフタといったブロックどもを練習してみます。ほぼほぼゲートレベルのロジックシミュレータのような雰囲気。しかし、ロジックシミュレータとしては抜けている部分がありあり。

-

- 値は整数のみ、端的には0か1。X(不定)などはない。もっと言うと信号強度(ストレングス)など無い(あると「ワイヤド・オア」とか、MOSスイッチを扱えたりする。でもそんなもの最近流行らないか。)

- 遅延は無い。別途ゲートの外でディレイブロックを接続すればできないこともないが、多分それをやると回路がみていられないくらい醜くなる。

- 整数といっても符号付きバイト限定の入出力が多い。それを使って任意のビット幅のバスのような構造を作ろうとするのは辛い。

もっと適当な論理シミュレータが存在するので、Xcosをロジックシミュレーション(ゲートレベル)に使うのは不適と思います。無理やり使い途を考えるならば、(アナログ/デジタル)制御系の一部に小規模なゲートレベルのロジックが組み込まれているようなシステムをシミュレートするくらいかと。

以下、今回練習するブロックどもの一覧です。

-

- SHIFT — Shift/Rotates Bits

- LOGIC — Combinatorial Logic

- DFLIPFLOP — D flip-flop

- DLATCH — D latch flip-flop

- JKFLIPFLOP — JK flip-flop

これ以外に、SRフリップフロップもあるのですが、上記にJKフリップフロップ含まれているので割愛。

SHIFTとLOGIC

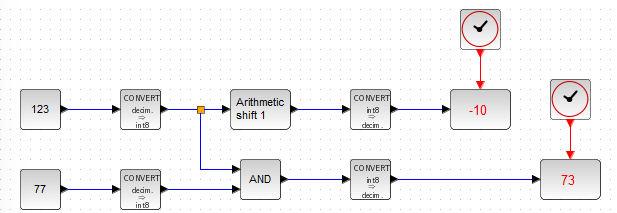

定数をシフトするものと、ANDをとるものを設定してみました。

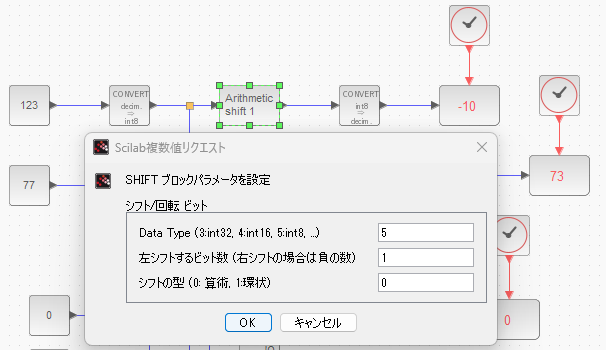

まずはSHIFTですが、左右のシフト、そしてローテイトが存在します。データ型は、8ビットだけでなく、16ビット、32ビットにも対応してます。いいじゃん。でも符号付のみなのです。符号無には対応してません。勿論、飽和とか丸めとか最近のプロセッサが持つアリガチな機能は不在(Armプロセッサのシフト系命令のごく一部についてまとめた別シリーズ記事はここ)

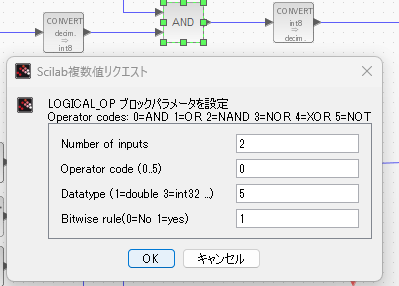

一方 LOGICブロックは、AND、OR、NAND、NOR、XOR、NOTと一通りそろっており(NAND、NORがあるのにXNORなし)「使えんこともない」雰囲気はかもしてます。

LOGICのセッティングが以下に。

DFLIPFLOPとDLATCH

DFLIPFLOPとDLATCH

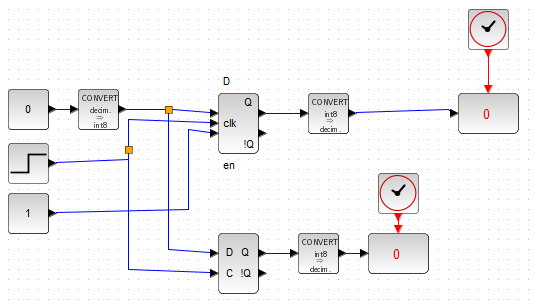

いわゆる「エッジトリガ」なD-FFと、「レベル・センス」あるいは「トランスペアレント」なDLATCHです。練習回路が以下に。

両ブロックとも特に設定など無いようです。すこし妙なのは、データ入力Dと出力Q、!Q(Qの逆相)については、符号付8ビット限定なのに、D-FFのclk、en入力、DLATCHのC入力については real でも良いというちぐはぐなところです。まあXcosの場合、整数型より real の方が扱いやすいけれど。

JKFLIPFLOP

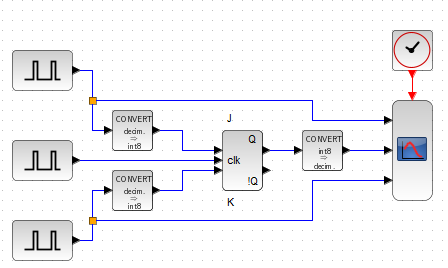

最後はJKフリップフロップです。Setに相当するJとResetに相当するKです。JKともに0なら保持、JKともに1ならトグルです。clk入力持っているのでエッジトリガなタイプね。回路は以下に。

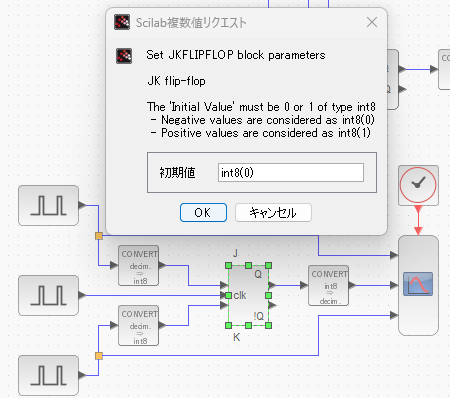

clkには1Hzの矩形波を与え、Jには2Hz、Kには4Hzの矩形波を与えてます。JKフリップフロップの設定が以下に。初期値0です。

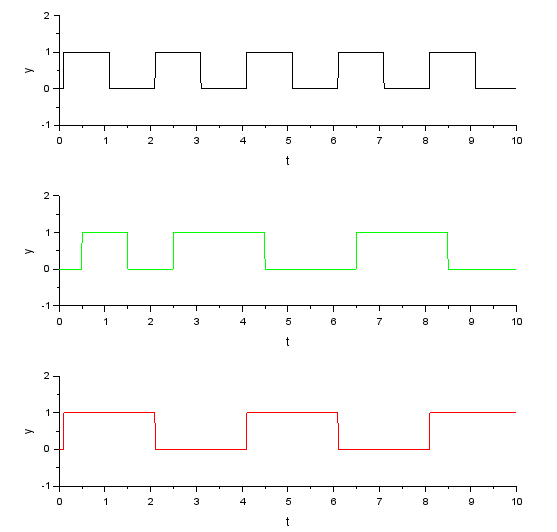

上記の「シミュレーション」結果が以下に。黒色がJの波形、緑がJK-FFのQ出力、赤がKの波形です。clkは毎0.5秒のところにライジング・エッジが来ます。

JKしてますな。頭に0.1sくらい遅延が入っているように見えるのは、元波形の生成ブロックに0.1sの遅延が入っているためです。