前回、FPGA上のRISC-Vコア(MicroBlaze V)上でDhrystoneベンチマークを実行。イケイケな感じ?になったので今回はVitis IDEから使用できるデバッガを使ってみます。これが簡単に起動できるだけでなく、各種機能がお楽で見やすい感じ。ただプラットフォーム作るときにデバッガに配慮しておかんと。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

デバッガの起動

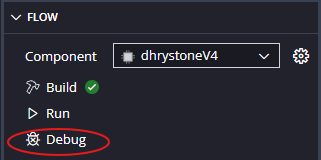

前回FPGA上で実行した Dhrystoneベンチマークのプロジェクト、前回は「Run」というボタンを押して実機実行してましたが、Debuggerでデバッグ実行する場合は、その下のDebugというボタンを押すだけです。

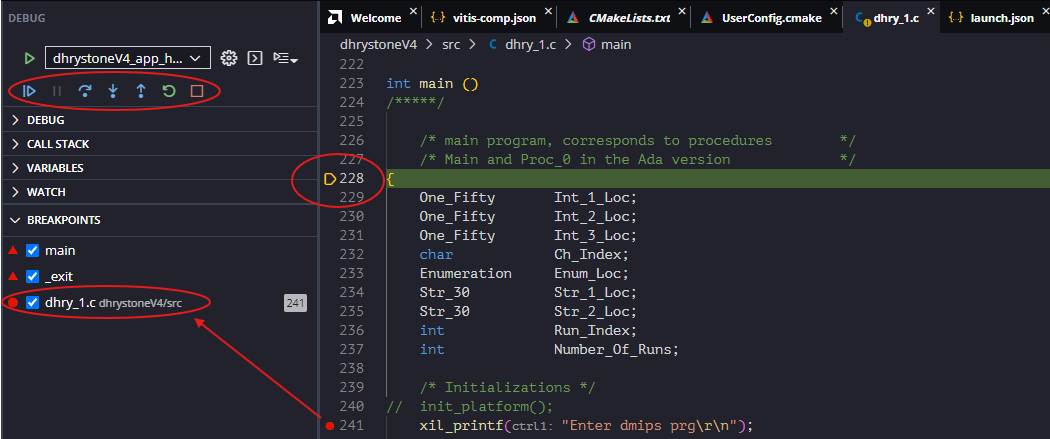

さすればごちょごちょ下の方で何やら動いているメッセージが続いた後、起動に成功すれば以下のような画面に切り替わります。この辺はVisual Studio Code使っていたら「ありがち」な感じでしょうかね。

上記画面の左上の赤丸のところが、デバッガを操作するメインのパネルで、その下に各種の表示などが折りたたまれてます。上記ではブレークポイントだけ開いており、右のソースコード部分の一番下の241行目のところに仕掛けたブレークポイントが反映されてます。なお、上記は起動直後の様子です。黄色の5角形の現在位置は228行目のmain()関数の冒頭にいます。

ここでデバッガの操作パネルの左端の実行ボタンを押してやれば241行目まで走ってブレークポイントで止まります。や~デバッグできとるやんけ。

なお、真ん中辺にならんでいるステップ実行ボタンなどを押してみましたが、ステップ実行も問題なくできとります。VARIABLESを開けば、ローカル変数など特に指定せずとも列挙されており、ステップしていくと値が反映されてました。よい感じ。

ディスアセンブリのタブ

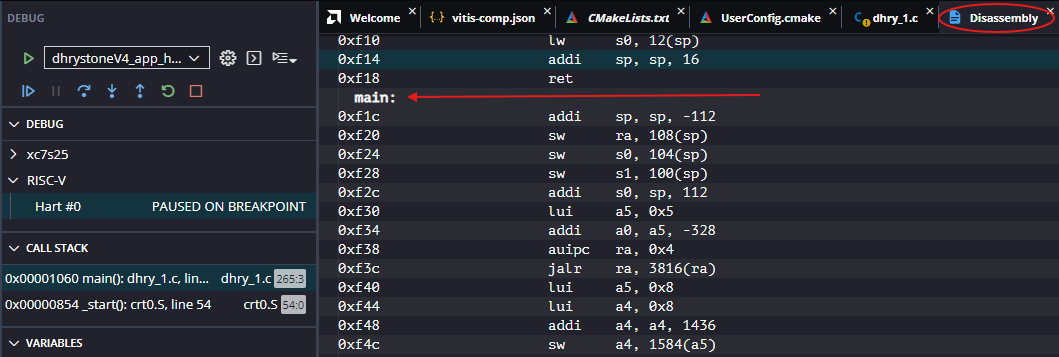

さらに嬉しいことにディスアセンブリのタブも表示してくれるようでした。こんなかんじね。

上記はメイン関数の冒頭のところで、ありがちなスタック上に領域をとって最低限のレジスタをスタック上にストアしたりしているところです。昔、別シリーズ「ぐだぐだ低レベルプログラミング」の第20回から第58回までを費やしてRISC-Vの命令どもを一通り練習したのだけれど忘れとります。忘却力だよ。

各種の「インスペクタ」もあり

ディスアセンブル・リストがあれば、レジスタ・ダンプもあり、ということでその辺の機能は、Vitis IDEの右端の方にアイコンがならんでました。

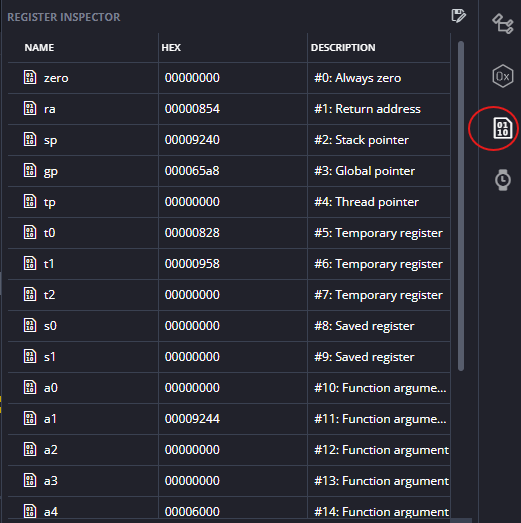

まずレジスタ・インスペクタが以下に。右端の赤丸のアイコンを押すと以下のような画面が右側に控えめに(プログラム・リストを隠さない程度に)開きます。

RISC-Vの場合、整数レジスタは32本あり、X0からX31の「無味乾燥」なレジスタ名で呼ぶこともできるのですが、上記ではRISC-VのABIで使用している「ABI的に意味のある」お名前が左端にならんでます。右側のDESCRIPTIONのところの#なんちゃらが、無味乾燥な方のXにつづく番号です。RISC-Vの公式どおりの使用方法が併記されているので、忘却力の年寄も安心。

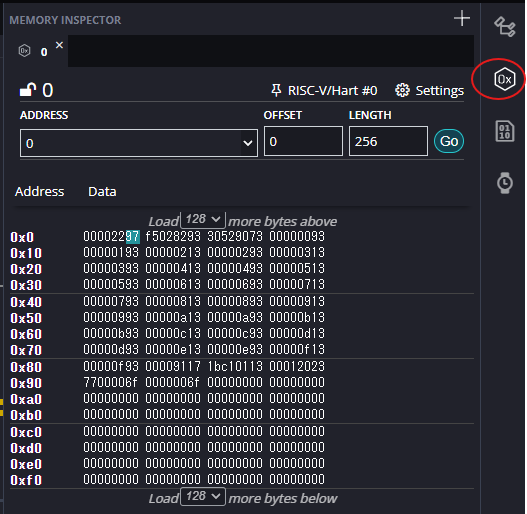

続いてはメモリインスペクタです。右の赤丸したアイコンを押すと以下のメモリインスペクタのウインドウが開くので、アドレス他を入力してGoボタンを押せばダンプされます。

いい感じでないかい。

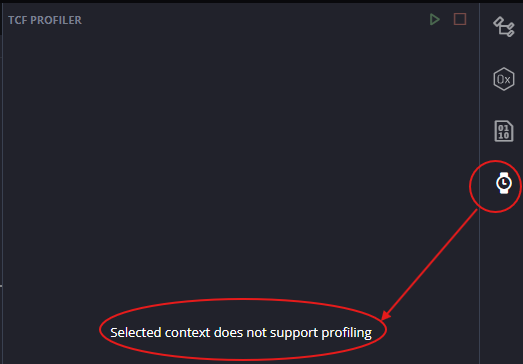

一番下の時計マークはプロファイラのアイコンです。ただ残念なことに、今回の「プラットフォーム」では以下のようなメッセージがでて動きませなんだ。

胸に手を当ててよ~く考えてみると、Vivado上でRISC-Vのコアをコンフィグするときに

-

- ブレークポイントは1本だけ

- プロファイリングに使う機能は無

ということで設定しちまってます。こんなに使いやすいのなら、ブレークポイントはも少し増やして、パフォーマンスモニタ用の機能も実装ONにしても良いかも。また今度やってみますわ。

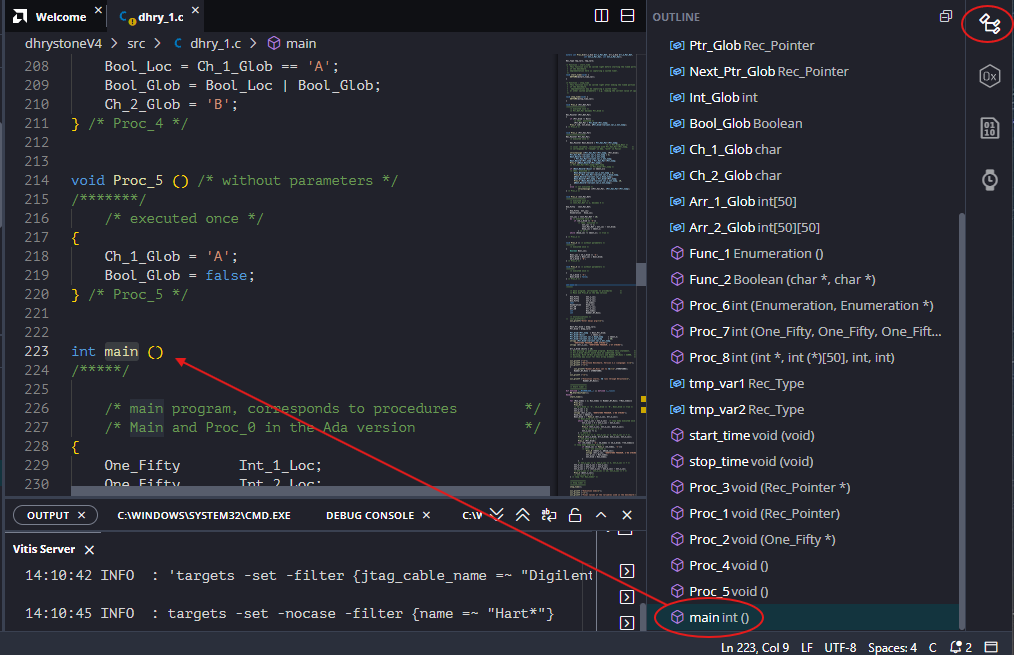

なお、各種のインスペクタどもの一番上のあるアイコンは「アウトライン」のボタンです。

ソースをナビゲートするための、よくある機能ですが、何もせずとも即使えるのでお楽。

Vitis IDE(2024.1)のデバッガ、とってもお楽。