RISC-V(MicroBlaze-V)コアを扱い始めて気になっていたのが、タイミングエラーです。踏みつぶしてFPGA上に実装しても「動いているように見える」けど気持ち悪いです。今回はどこで何が起こっているのか確認してフォルス・パスなり何なり制約条件を付けようかとして悩みました。hiddenの中に埋もれてるじゃん。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

タイミングバイオレーション

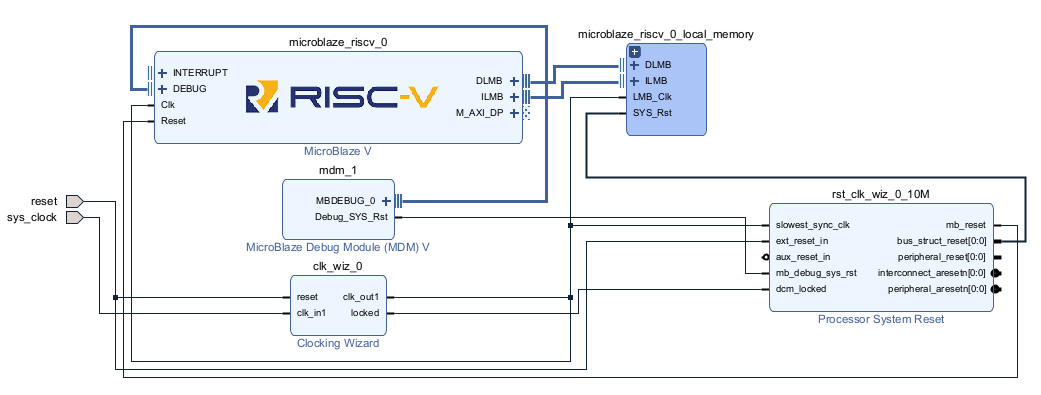

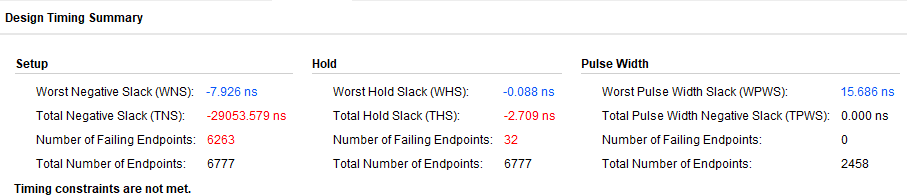

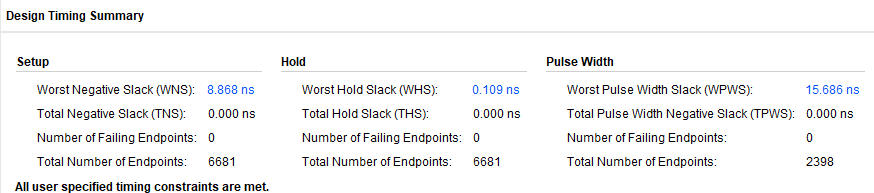

以下は、クロックソースを10MHzに「抑えた」ときの「5段パイプライン」RISC-Vコアのタイミングエラーのサマリです。

Setupはほぼほぼ壊滅的、Holdの方は局所的ですが何かありそうな感じです。なにかクロックそのものの設定に暗雲漂っているような気がしないでもないです。

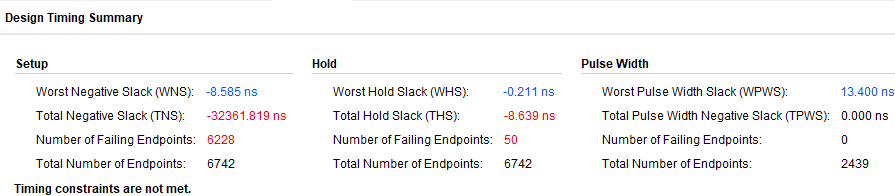

クロックを5MHzまで「抑えて」もこんな感じ。反って悪くなってないかい?

まあ、タイミング・レポートを見ながら調べれば原因分かるんでないの?問題点を追及してみました。以下の2つにほぼほぼ集約される感じ。

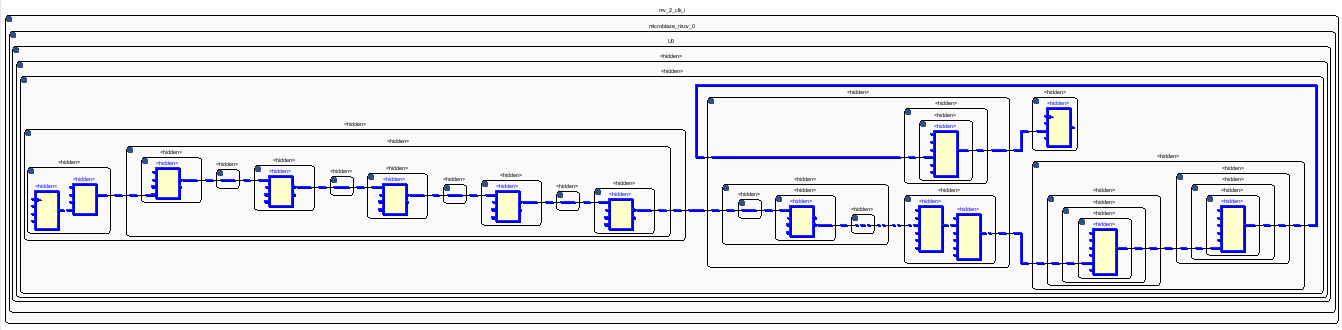

確かにかなり長いパスではある。しかしCELL名を見ていくと、RISC-Vコア内部の hidden なブロックの hiddenなCellからCellへと繋がっている。何から何までhiddenだと。

次の「マズイ」パスを見てみるとこんな感じ。お名前が書いてあるじゃん。

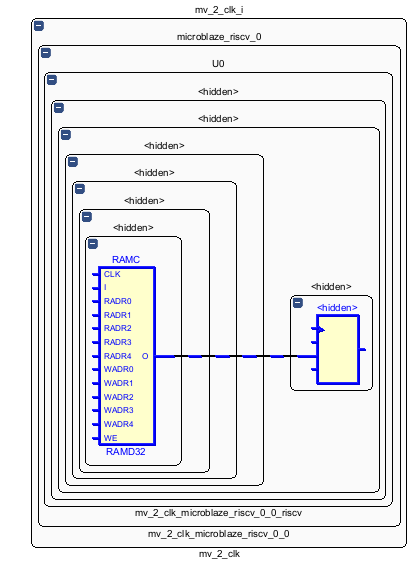

RAMCという、いかにもRAMセルという構造が見えますが、その周りは hiddenでくるまれてます。そして行先も hidden。

RAMCという、いかにもRAMセルという構造が見えますが、その周りは hiddenでくるまれてます。そして行先も hidden。

お惚け老人的には「コイツら」をフォルス・パスなどに指定して良いもんだかどうだか分からず。hiddenの中のhiddenだもんね。さらに言えば、hiddenからhiddenへ接続される信号をフォルス・パスに指定する方法が分かりませぬ。

まあ、クロックでまとめて除外指定する手は使えるみたい(実際にやってみるとバイオレーションが一気に消えます。)こんな感じ。

でもこれって何もチェックしてない、ってのとほぼほぼ同じだべさ。。。マズイんじゃないだろうか。FPGA素人老人の混迷は深い。