前回はイネーブルになっているデュアル・コアはそれぞれArmなんだかRISC-Vなんだかハッキリしろい、ということでステータスレジスタを読み出して確認しました。しかし、2コアの片方しか動かしてなかったです。今回は超簡単な実験スクリプトで2コアの両方が動いているところを確認したいと思います。手抜きだけれども。

※Pico関係投稿一覧は こちら 『Pico三昧』は一覧の末尾付近にひっそりと。

※Pico2対応のMicroPython処理系(バイナリ、uf2形式)は以下のURLからダウンロード可能です。

https://micropython.org/download/RPI_PICO2/

※動作確認に使用しているMicroPython処理系は以下です。

MicroPython-1.24.0-riscv–with-newlib4.3.0

ラズパイPico2搭載のRP2350マイクロコントローラは、Arm2個、RISC-V2個の合計4個のプロセッサを搭載してます。しかし、同時にイネーブルにできるのはコア0とコア1と呼ばれる2個だけです。組み合わせ的にはコア0とコア1に異なるアーキテクチャのプロセッサをアサインすることも可能ですが、RISC-V版のMicroPython処理系はRISC-Vのみです(当然Arm版はArmのみ。)

前回はMicroPythonのコードで直接OTP制御レジスタ内のステータスレジスタを読み出して本当にRISC-Vなんだよね、ということを確認。

今回は一歩進んで、Dualコアの両方を起動して双方コアに「爪痕」残してもらいます。ただし、何の制御もなく標準出力に結果をたれ流している手抜き版デス。

過去回でのマルチコア利用例

以下の別シリーズの過去回でラズパイPico、RP2040上でのマルチコア実行の試行をやってみてます。

MicroPython的午睡(12) ラズパイPico、簡単!マルチコアでLチカを

やっていることはLチカで、異なるプロセッサコア上で動作している「スレッド」でそれぞれLチカするというものです。

コアの識別

コアがArmであろうとRISC-Vであろうと、2つのコア間にはSIOというブロックが存在し、コア間通信などを担っています。このSIOの中にCPU_IDというレジスタがあり、ここを読んだときに0が読めれば自分はコア0、1が読めれば自分はコア1と分かります。アドレスが以下に。

-

- SIO_BASE 0xd0000000

- CPU_ID 0x000(オフセット・アドレス)

今回のMicroPython実験コード

両方のコアから何の制御もなく標準出力に結果を勝手にたれ流す、手抜きな実験コードが以下に。

import time, machine, _thread

from micropython import const

OTP_BASE = const(0x40120000)

ARCHSEL_STATUS = const(0x15c)

SIO_BASE = const(0xd0000000)

CPU_ID = const(0x000)

def taskA():

cpuid = machine.mem32[SIO_BASE + CPU_ID]

print(" task A CPUID: {0}".format(cpuid))

def taskB():

cpuid = machine.mem32[SIO_BASE + CPU_ID]

print(" task B CPUID: {0}".format(cpuid))

def main():

print("Multicore test")

stat = machine.mem32[OTP_BASE + ARCHSEL_STATUS]

c0="Arm"

c1="Arm"

if stat & 1:

c0="RISC-V"

if stat & 2:

c1="RISC-V"

print("Core 0 is currently {0}. Core 1 is currently {1}.".format(c0, c1))

_thread.start_new_thread(taskA, ())

taskB()

if __name__ == "__main__":

main()

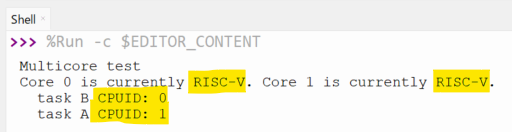

実験結果

上記をPico2上のMicroPython処理系で実行すると、コンソールに以下のような報告が上がってきます。

両コアともRISC-V、そしてtask Aはコア1で、task Bはコア0で実行されておると。まあ意味のあることは何もしとらんけど。