最近、老眼のせいか部品をいじるのが億劫になりつつあります。これはイケない。手を動かさないと。とはいえカッコイイ回路など作れる筈もなく、年寄は年寄らしく古色蒼然たる回路を復習。今回はパルス波形の立ち上がり、立下りなどを検出して一発食らわせるエッジ検出回路です。こんな回路もやってなかったんだっけ。お間抜け。

※「定番回路のたしなみ」投稿順Indexはこちら

今回のエッジ検出回路

今回の回路は古色蒼然とした回路っす。RC時定数で「遅らせた信号」を組み合わせ回路でエッジを抽出するもの。当然、設定したRCの値よりも高速な信号にはなすすべもありませぬ。まあ、その代わりお惚け老人でも理解できる回路の簡便さが利点かと。ムツカシーところはないし。

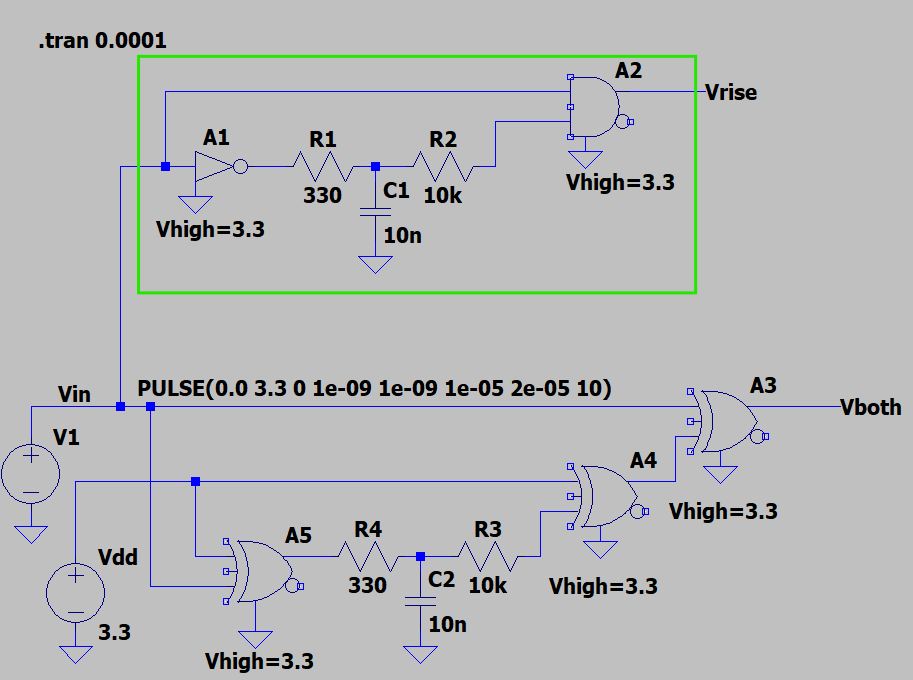

以下にLTspiceにエントリした「立ち上がり」検出と、「両エッジ」検出の回路図をかかげます。「立ち上がり」をひっくり返せば「立下り」はできる筈、ということで、片エッジの検出と両エッジの検出を並べてみました、という感じデス。

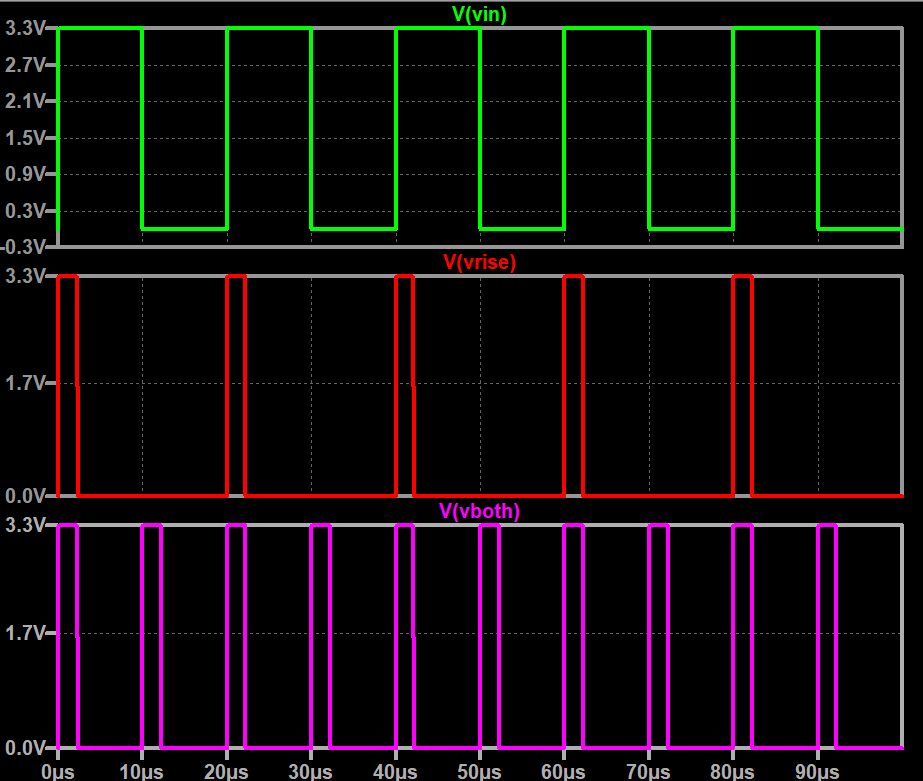

LTspiceの論理ゲートのシンボルはちょいクセ強で見ずらいですが、簡単な回路なのでお分かりでしょう。上の緑枠の中が立ち上げりエッジ検出回路で、Vinに与えられた波形の立ち上がりエッジで一発パルスをお見舞いするもの。下のVboth出力は、入力波形の立ち上げりと立下りの両方でパルスを発生するものです。

LTspiceの論理ゲートは、デフォルトで1Vを論理1(ハイ)に見立てるような感じになっているので、パラメータVhighに3.3を与えて、ハイのときに3.3V出力が得られるように設定してます。

黄緑のVin波形が入力信号。赤のVrise波形が上の「立ち上がりエッジ検出」回路の出力です。ピンクのVboth波形は下の「両エッジ検出」回路の出力です。

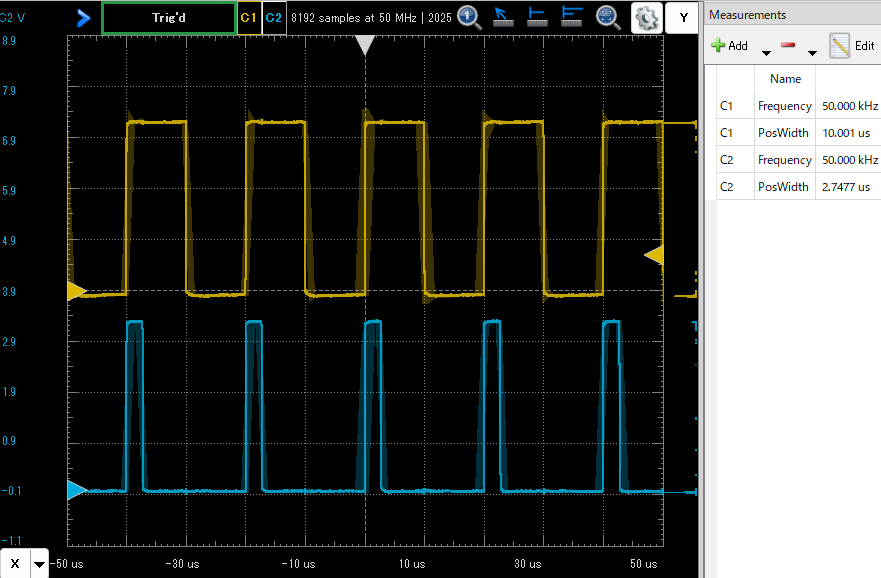

ブレッドボード上の現物確認

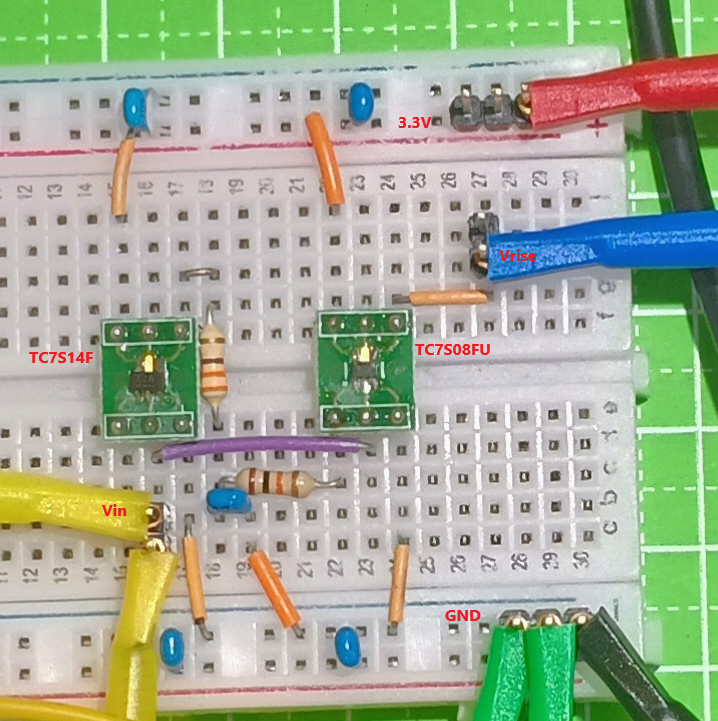

現物の動作確認をする段になってぬかっていたことに気づきました。手元にXORの在庫がありませぬ。正確に言うと1ゲートだけ「ワンゲート」ロジックがあったのですが、それでは不足です。仕方がないので、上の「立ち上がりエッジ検出」回路のみブレッドボード上に実機実装して動作確認してみました。東芝様のワンゲート・ロジック使用です。回路はこんな感じ。

古色蒼然の回路でも、今でも動くよ。あたりまえか。