前回が古色蒼然たるRC使ったエッジ検出回路であったので、今回は「まだしもな」シフトレジスタ使ったエッジ検出回路です。そうは言っても半世紀前でも存在していた筈の回路、これもまたクラシック。勿論、今でも使えるし、使っているケド。この頃はディスクリートなRC部品より、トランジスタは只みたいなもんだし。

※「定番回路のたしなみ」投稿順Indexはこちら

LTspiceでのシミュレーションでちょっと躓く

今回はシフトレジスタ、といっても2ビットの回路を使ってますが、そのLTspiceシミュレーションにてちょっとトラぶりました。その件については以下の別件シリーズに書きました。

SPICEの小瓶(58) LTspice、dflopの挙動、デフォルト遅延0なのよ

LTspiceの「Digital」コンポーネントを使うときは、デフォルトのままで放置せず、ちゃんとパラメータ与えれば済むことであります。

D-FF使った回路とそのシミュレーション

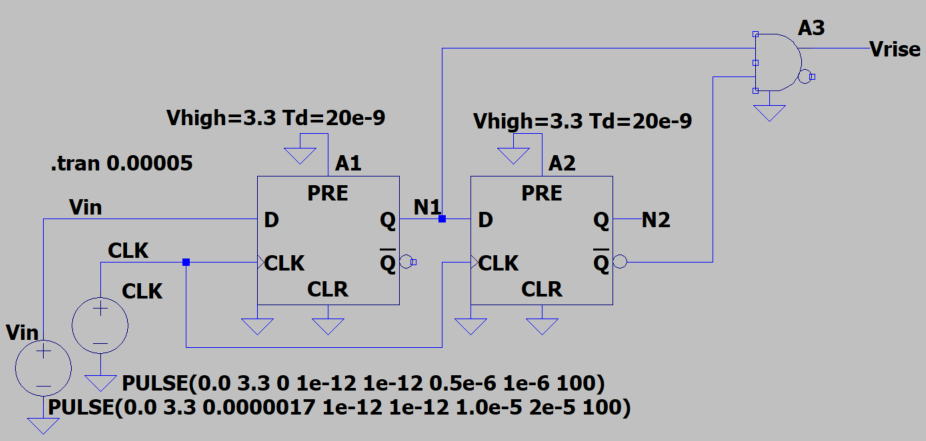

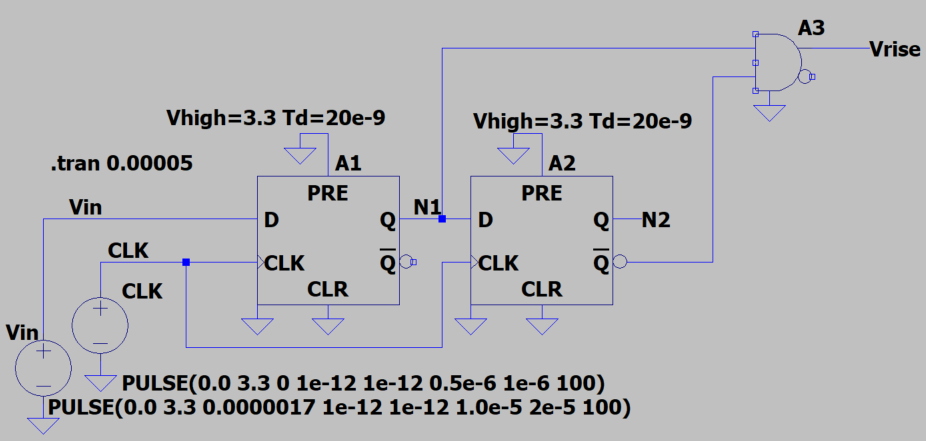

さて、D-FFでシフトレジスタ作ったエッジ検出回路のLTspice回路図が以下に。

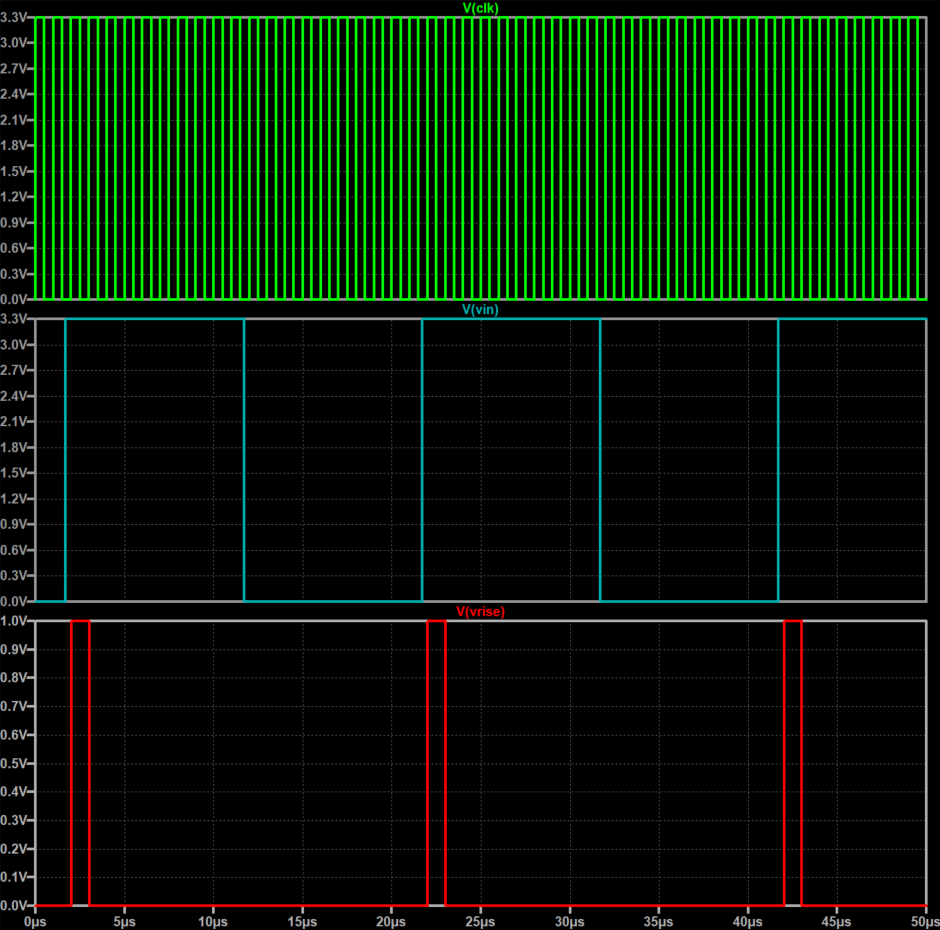

一番上がCLK信号、真ん中が入力波形、一番下の赤が立ち上がり検出波形です。上記ではQ1とQ2バーを取り出してANDしたので立ち上がりですが、当然、Q2とQ1バーにすれば立下りにも出来るハズ。ちょっと改造すれば両エッジ抽出も思うがまま。ただし検出にクロック使っているので、クロックより短い入力波形には成すすべありませぬ。

実機回路

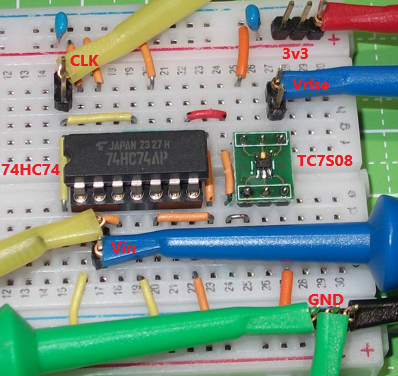

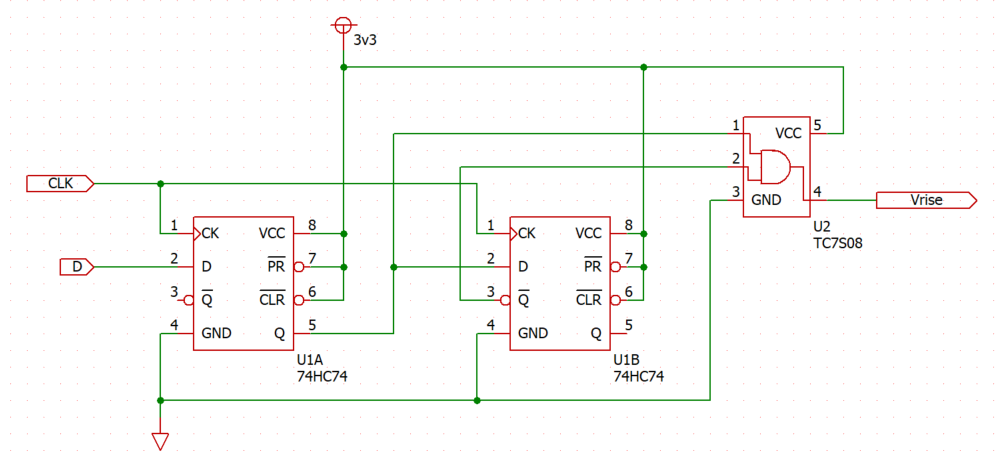

例によってブレッドボード上に実機回路を組み立てて、その波形を観察してみました。D-FFには TC74HC74使っているのでPRとかCLRの極性が上のLTspice回路図とは異なります。こんな感じ。

末尾のANDゲートは東芝ワンゲートロジック(L-MOS)です。

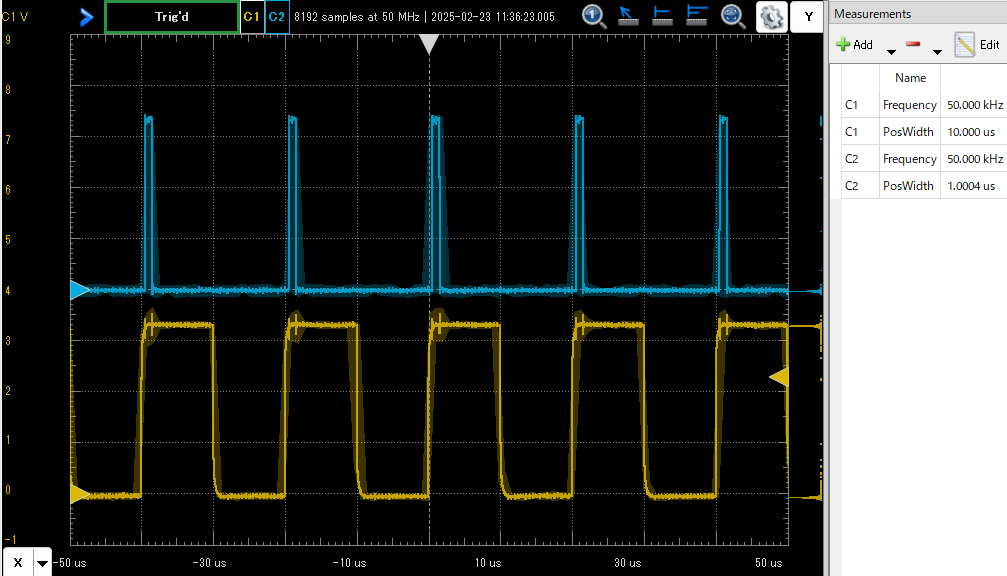

下の黄色が入力波形、上の青色が立ち上がりエッジを検出した出力波形っす。

わざわざLTspiceするほどの回路じゃないけど、まあやると気づくこともあるっと(別件。)