前々回がRC遅延、前回がシフトレジスタを使ったエッジ検出回路でした。結局、遅延させれば検出できるっと。今回は論理ゲートの遅延を利用したエッジ検出回路です。ICの上でRCモドキは作れるけどピュアなRC作ろうとするとデカい。シフトするにはクロックいるし、ということでゲート遅延はお楽。でも電圧や温度で遅延は変る、あなた任せ?

※「定番回路のたしなみ」投稿順Indexはこちら

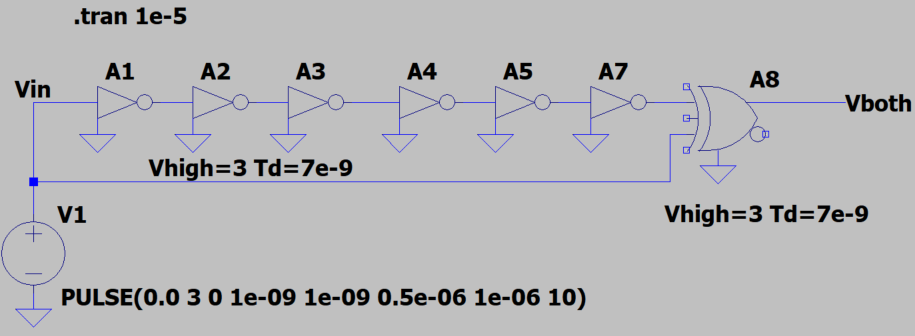

LTspiceシミュレーション

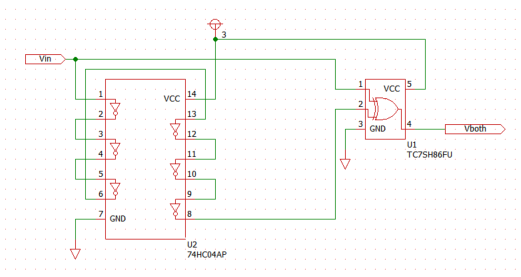

わざわざシミュレーションするほどの回路じゃないですが、過去回もシミュレーションしているのに、今回だけ除外するのも何なので行った時の回路が以下です。

今回は電源電圧3.0Vとしたので、Vhigh=3としてます。また肝心の遅延値Tdは7nsという値にしてみました。これは後で出てくる現物のXORゲートの3.3V、CL=15pFのときのTypical値をコピペしたものです。なお、この手のSPICELine属性の表示にチェックを入れるととっても五月蠅い図面になるので、A1とA8のみチェック入れて、他は非表示にしてます。

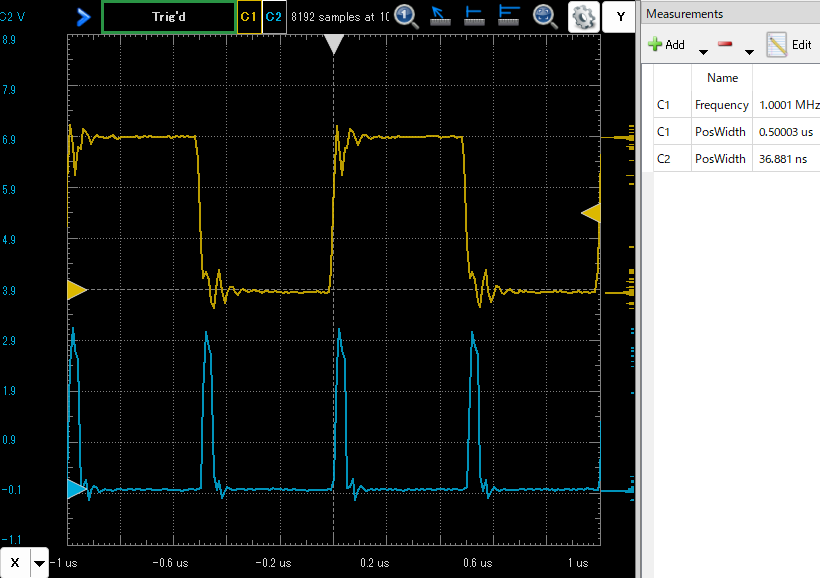

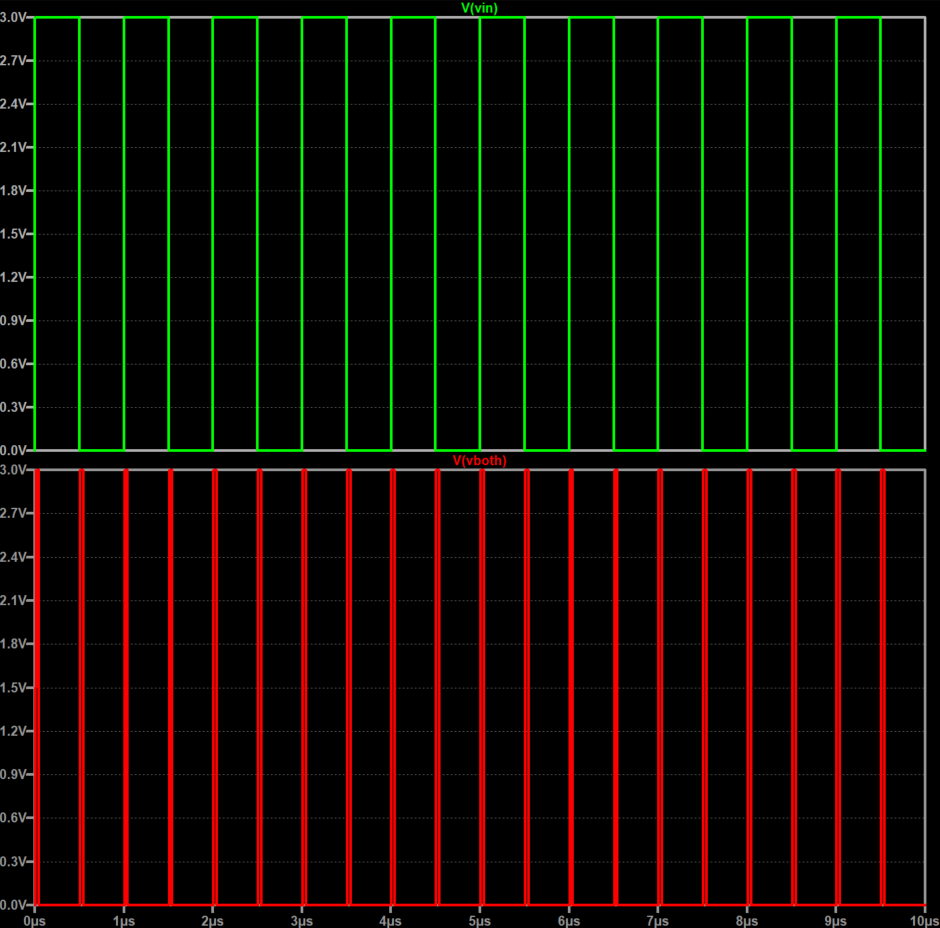

入力信号は0~3V振幅の周波数1MHz、デューティほぼ50%の矩形波です。シミュレーション結果が以下に。

しっかり両エッジでパルスがとれてます。過去回でやったとおりで、ゲートをとっ変えれば、立ち上がりでも立下りでも思うがままだと、ホントか?

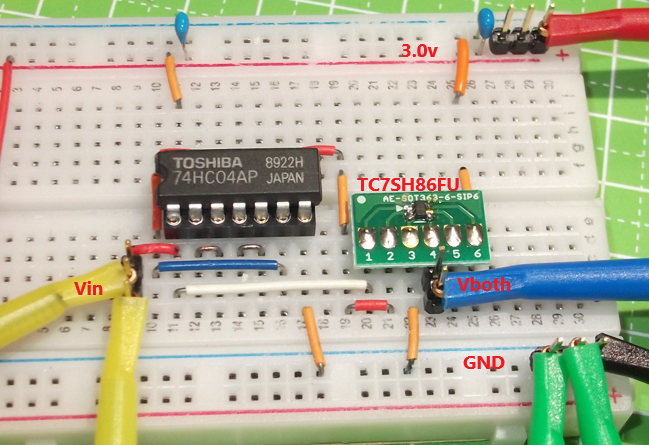

現物回路

手もとの部品箱にころがっている部品採用、ということで取り出したデバイスは以下です。

上はみんな大好き74HCシリーズの、知らない子はモグリ的代表品種の6回路入りインバータであります。

下は東芝様お得意の「ワンゲート」ICのXOR(排他的論理和)です。

黄色が入力波形(3V振幅の1MHz矩形波)、青色が両エッジ検出の出力です。パルス幅も含めて雰囲気出ているんでないかい?

実のところいうと、回路図もなく先に現物回路を組み立てて動かした後、シミュレーション回路、現物対応回路を描いたという泥縄的な実験だったけれども。順番ひっくり返して説明すれば論理的? ホントか?