このところロジック回路と遅延で作るような古色蒼然とした回路が続きました。今回はオペアンプとMOSFETで作るサンプルホールド回路です。別にADするわけでないのだけれど。世の中を見渡せば当然、立派な特性のサンプルホールド専用ICなどもあり、今回のような回路はビミョー。一応練習してみるってもんかと。

※「定番回路のたしなみ」投稿順Indexはこちら

サンプル・アンド・ホールド回路

例によって、Googleの生成AI、Gemini様にサンプル・アンド・ホールド回路についてご説明いただきます。

この後もいろいろご説明してくださってますが、回路みた方が早いのでバッサリです。すみません。

上記の回路の元ネタは、JRC(現、日清紡マイクロデバイス社)の オペアンプの応用回路例集に記載の回路です。多分4分の1世紀近く前の文書です。どういう経緯か、皆大好き秋月電子通商様の以下URLから今でもダウンロードすることが可能です。

https://akizukidenshi.com/goodsaffix/OP_AMP_APP_J_REL.pdf

元文書は、JRC社発行とは言え、特にオペアンプをこれとか、MOSFETはこれとか指定のない回路図なので、上記回路図は、当方の勝手にて手元にあるデバイスで置き換えてます。また回路定数などもテキトーに変更。ううむ。。。

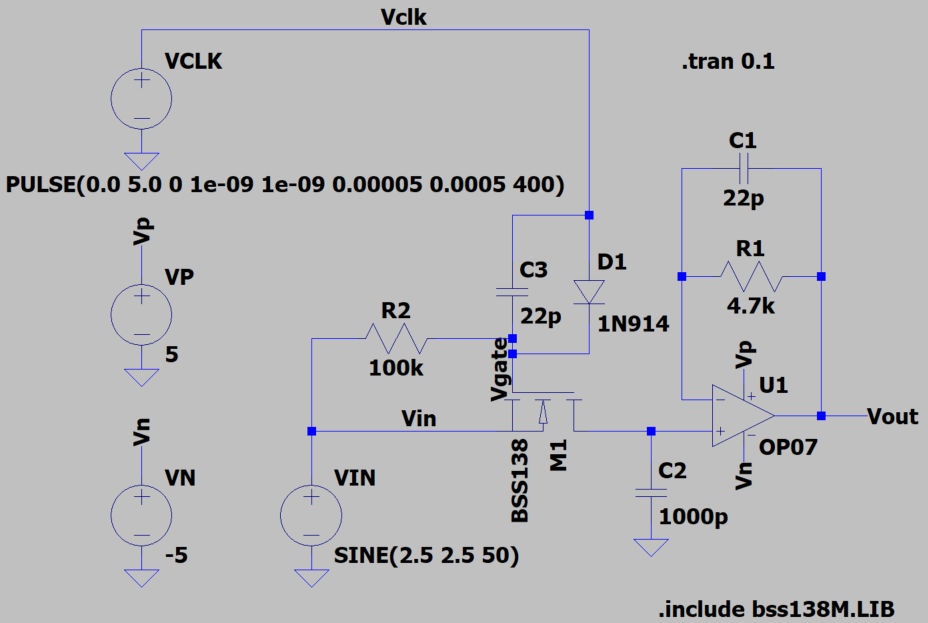

まずはLTspiceシミュレーション

すみません、旧JRC社の資料なのにアナデバ社のOP07使ってます。よってLTspiceのモデルはバッチリです。nch MOSFETはBSS138使ってます。以下の秋月通商ページで販売されているもの。

https://akizukidenshi.com/catalog/g/g104232/

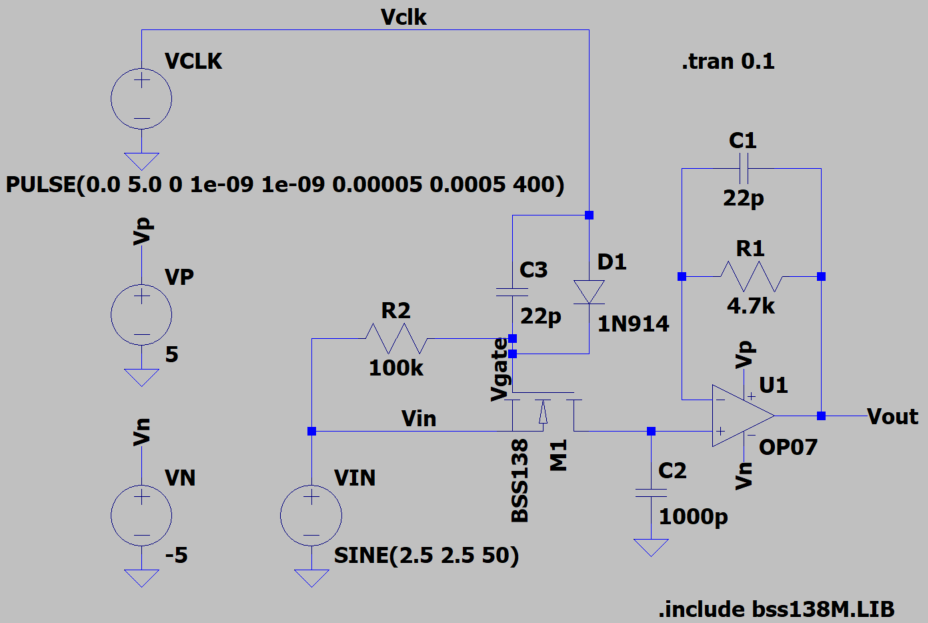

グラフの上のペインのピンク色(裏に隠れて見ずらいですが)がVclk(サンプリング・クロック)、金色がVgate(実際にNチャンネルMOSFETのゲートに印加される電圧)です。

下のペインの赤色が入力の正弦波信号、黄緑色がVclkでサンプリングした結果をOP07でホールドした出力波形です。OP07はレールツーレールではなく、伝統的な2電源オペアンプなので、そもそも電源Vpまで振れるなんてことはありませぬ。

まあ、上限に制限がある、ということをキモに銘じておけば(電圧そこそこの範囲で使えよ)、サンプル・アンド・ホールド出来てそうな気がします。

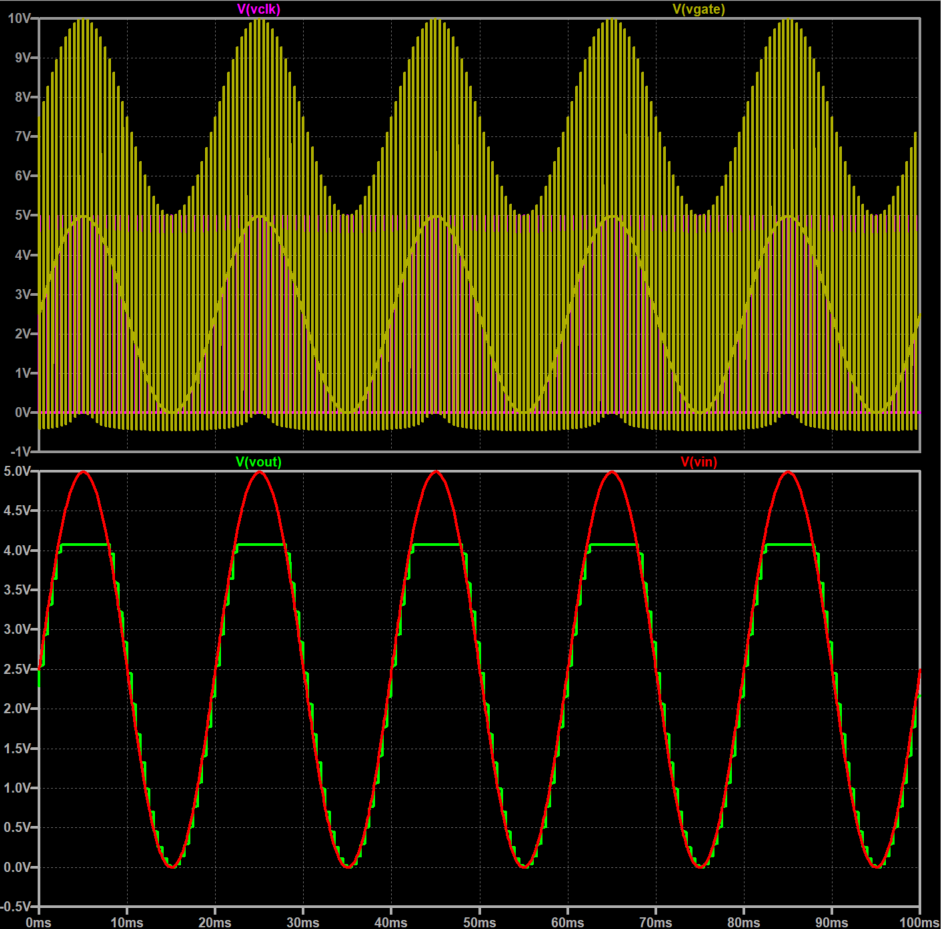

実機

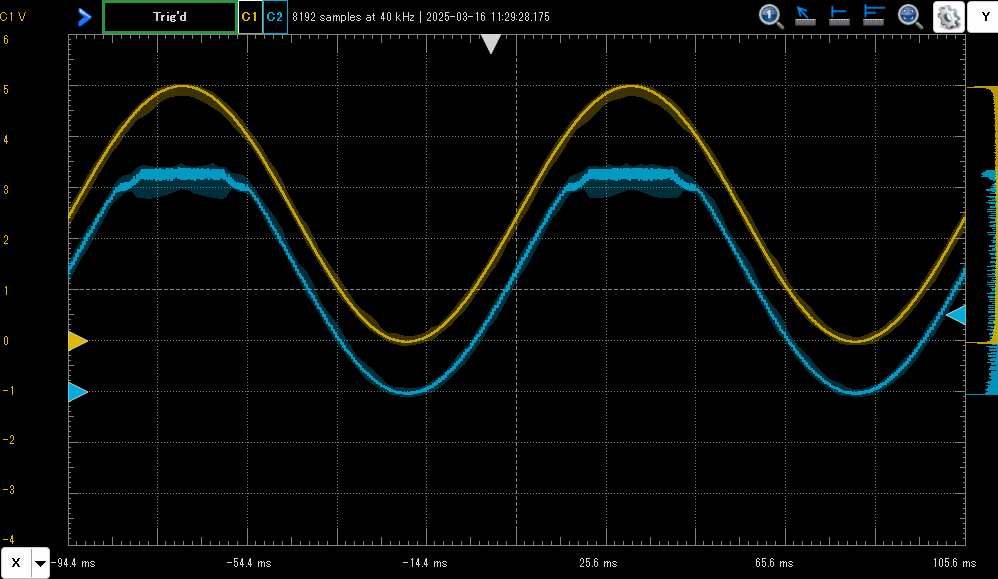

黄色が入力で、周波数10Hz、オフセット2.5V、振幅2.5Vの正弦波です。これをサンプリングクロック2kHz(デューティ10%の0-5V矩形波)でサンプリングしてOP07でホールドしたものが青色の出力信号です。

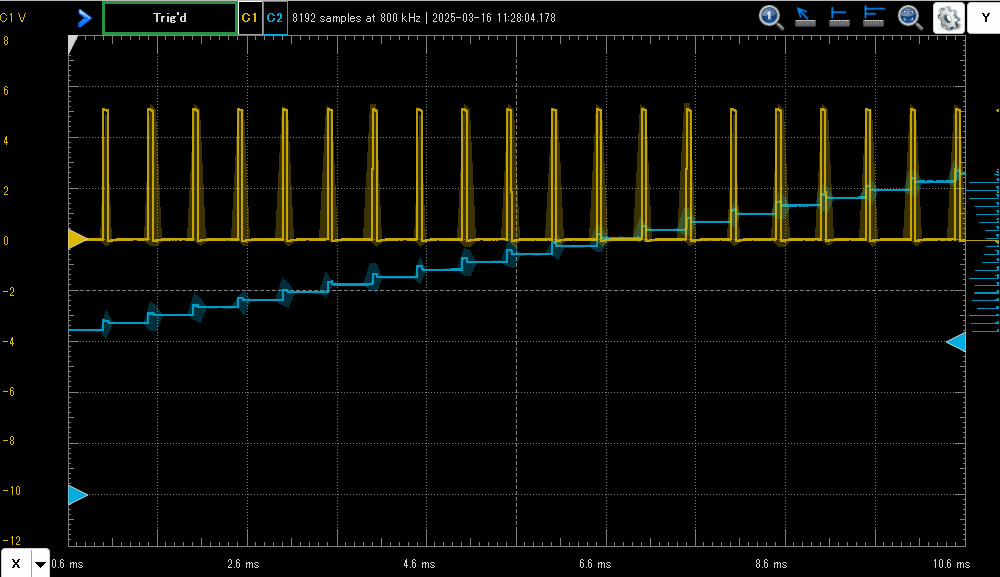

時間を拡大し、黄色をサンプリングクロック波形としたもの(一部範囲の拡大)が以下に。

サンプリングクロックとサンプリングクロックの間は、平らかで「ホールド」されているらしいことが分かります。いいのか?