前回、LTspiceの「ビヘイビア」なdflopを並べてみたら、デフォルトの遅延0でデータが「抜けて」しまったので慌ててコンポーネントに属性つけてシミュレーションしました。しかし属性つけずとも「動いている感」バッチリなモデルがEducationalフォルダにありました。BCDカウンタ74160のモデルです。

※「SPICEの小瓶」投稿順インデックスはこちら

Synchronous BCD decade counter、74160

今回試用してみるのは、LTspiceのExamplesフォルダの下のEducationalサブフォルダに格納されている

160.asc

という回路モデルです。なおこのモデルは

This example shematic is supplied for informational/educational purposes only.

だそうです。

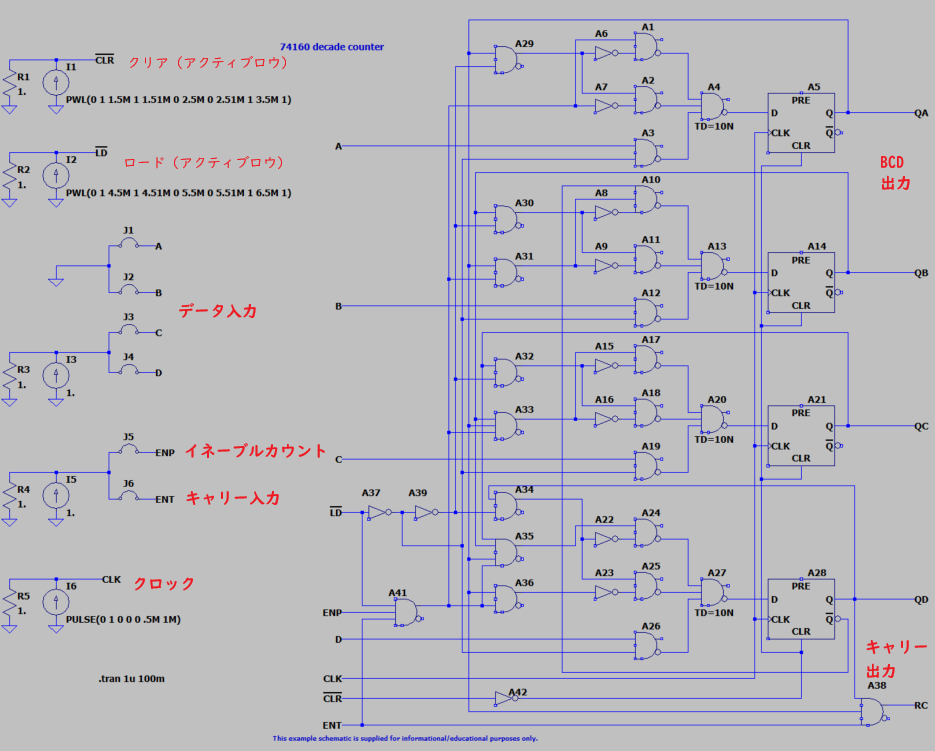

モデルが表しているのは、BCD一桁(decade)、4ビット分の同期カウンタである74160です。かっては一世を風靡した74ファミリのデバイスですが、古典的なBCD(バイナリ・コーデット・デシマル)カウンタなど今や需要などほぼないんでないかと思います。HDLちょこっと書いてFPGAの中に潜ませることなど一撃。そんなデバイスをLTspice上で表現してみたのが上記の回路図ということになります。回路図だけだとナンジャラホイなので、素人老人が入出力端子にテキトーな注釈を書きこんだものが以下に。

BCD1桁のカウンタであるので、出力はQAからQDの4ビットです。キャリー出力もあり。一方、同期式カウンタであるのでCLKに同期して全てのビットが更新されます。カウントを制御するためにENPとENTなる入力端子あり、これによりカウントの許可/停止、キャリー入力など制御もでき。RESETというか、クリア信号CLR#はCLKとは関係ないカウンタの強制クリアみたいです。また4ビットのパラレル入力端子AからDとそのロード制御信号LD#もあり。こちらはCLKと同期してのロード。

なおモデルで使用されているLTspiceのコンポーネントは、全て Digital フォルダに格納されている「ビヘイビア」な論理素子です。属性をつけなければ、0Vを0、1Vを1として動作する「ピュア」な奴です。そして前回のように属性をつけなければDフリップ・フロップのデフォルトの遅延ゼロとな。

シミュレーション

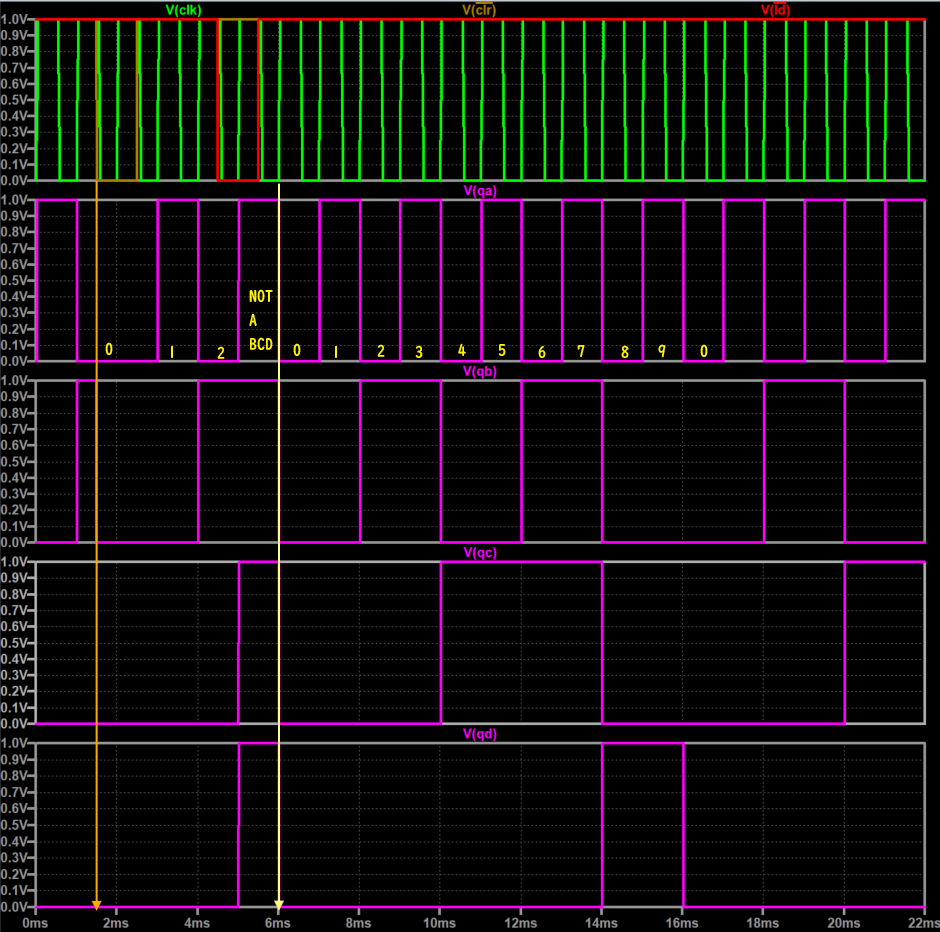

上記のモデルをロードしてシミュレーションしたものが以下に。「ロジック」といいつつ信号源でそれらしい信号を作ってくれてます。

シミュレーション波形に、これまたお惚け老人のコメントを書きこんだものが以下に。

CLR#信号(#はロウアクティブのつもり)、ロウのところでカウンタの値は0になってますが、イネーブル信号上は、常時カウントアップ状態であるので、すぐにカウントアップされていきます。

しかし、LD#信号のところで、パラレル入力から「BCDではない」変な値をロードすることを強いられます。カウンタそのものはそういう変な状態になっても、少ししたらゼロに戻ってカウントアップに復帰するような回路であるみたい。上記の黄色の矢印のCLKエッジのタイミングでオール0となって0クリア。以降は1、2、3。。。とカウントアップし、9にいたったところで0に戻りました。

BCDカウンタしているじゃん。あたりまえか。