ノスタルジックなゲートレベルのシミュレーションを楽しむ筈が、前回テストベンチもどきを取り付けたことで歯止めが効かなくなりました。やっぱりね~今時だからHDLも出来た方が良いよね~ ゲートレベルとHDLの橋渡しをどうするか、という問題は棚上げにして、今回はHDL環境を追加。

※かえらざるMOS回路 投稿順 INDEX

今日、ロジック設計と言ったらHDL書いて、シミュレーションして動いたら、シンセシスツールにお任せして実際の回路が出来上がるってな感じですかね。何かトラブラない限りゲートレベルでどうなっているか、なんて考えないっと。何百万ゲートいや何億もある?低レベルのロジックを読んでいたら死ぬまでに読み終わらないデス。

でもま、ソフトにせよ、ハードにせよ、低レベルなところに愛着があるので、そこに突っ込んでいきたいと思っております。しかしま、HDLなしには何もできない昨今かと。そこで ゲートレベルの回路図を開いた横で、VSCodeを開き、Verilog のソースを書き、シミュレーションし、波形を観察できるようにするべし、と考えましたです。今回はその設定編です。

Icarus Verilog、GTKwave

使用させていただいたのは以下の「フリー」なVerilog処理系です。FPGA作るにもASICやるにも商用の立派な処理系が主流じゃないかと思います。フリーと限定すると真っ先に登場する定番です。他に良いものが無いのかな。普通、仕事じゃ商用の処理系使うからねえ。。。ホームページが以下に。

手元の環境で使わせていただいておりますバージョンは以下です。

version 11.0 (devel)

Windows10PC上で運用しとります。すでにフリーのVCDビューワーGTKwaveは第19回で使えるようにしてありました。以下の3つがPATHに含まれていることがこれ以降の操作の前提であります。

-

- iverilog

- vvp

- gtkwave

VScodeからのVerilog使用

Verilogのソースそのものは普通のテキストファイルなので、VScodeで編集するのに何の問題もありません。各種のプラグインが充実しているVScodeのこと、Verilog用のプラグインもあるだろ、と思って見てみたら、ありました。有りすぎデス。どれを使ったらよいか選択に困ります。以下妄想です。

-

- ハードを記述するためのVerilogなので、使っている人数はソフト屋さんの10分の1以下(もしかすると100分の1とか1000分の1かもしれない)

- Verilog使っているけれど、メーカー製の商用開発環境上でやっている人が多数の筈(後続のツールチェーンとの接続もあるし)。VScodeのような汎用エディタ使っている人はそれほど多くないんでないかい?

- にも拘わらずVScode上のVerilogプラグインが多数ありすぎるのは、皆がやたらとツール作っている(作りすぎている)から。

ま、そゆことで以下2点のプラグインをインストールしてみました。

-

- Verilog-HDL/SystemVerilog/Bluespec SystemVerilog support for VS Code

- Simple solution to run testbench files, includes GTKWave support.

今回のDUT(Device Under Test)

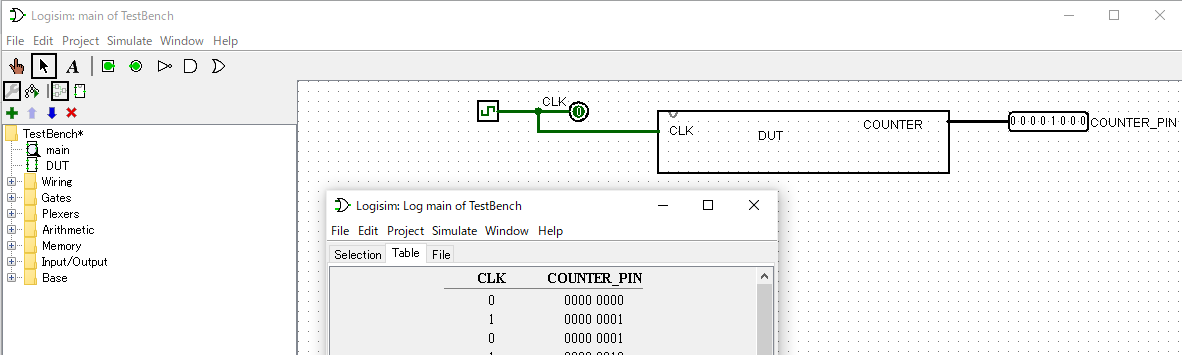

今回はテストということで、ゲートレベルシミュレータ Logisim上で以下のような感じのDUT、8ビットのカウンタを作ってみて、それとほぼ同等のものをVerilogしてみましたです。

以前からちょっと気になっていたのだけれど、今回Verilogで同等な回路を作ってアカラサマになったのは、

-

- Logisimではフリップ・フロップの類が0で初期化されている

- 普通のハードではそれは期待できない(もちろんVerilog上でも)

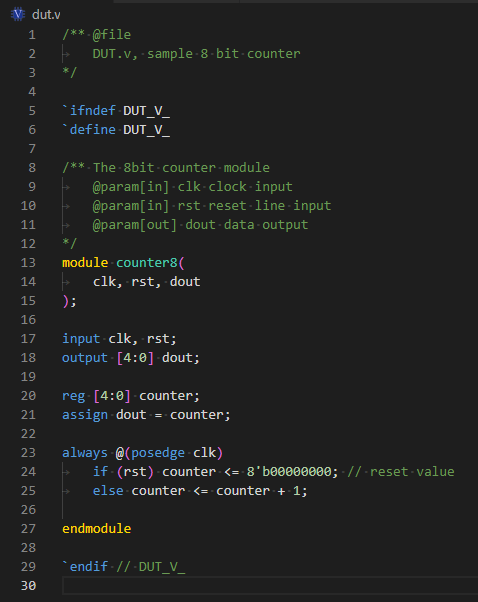

という点です。実用は考えず?ロジックを画面上でお試しするためのツールであるLogisimはメンドイ初期化などせずにロジック書き始められるようにとの配慮じゃないかと思います。まあVerilogで書くときは普通に初期化信号で初期化すると。作製したVerilogのソースが以下に。

動作確認

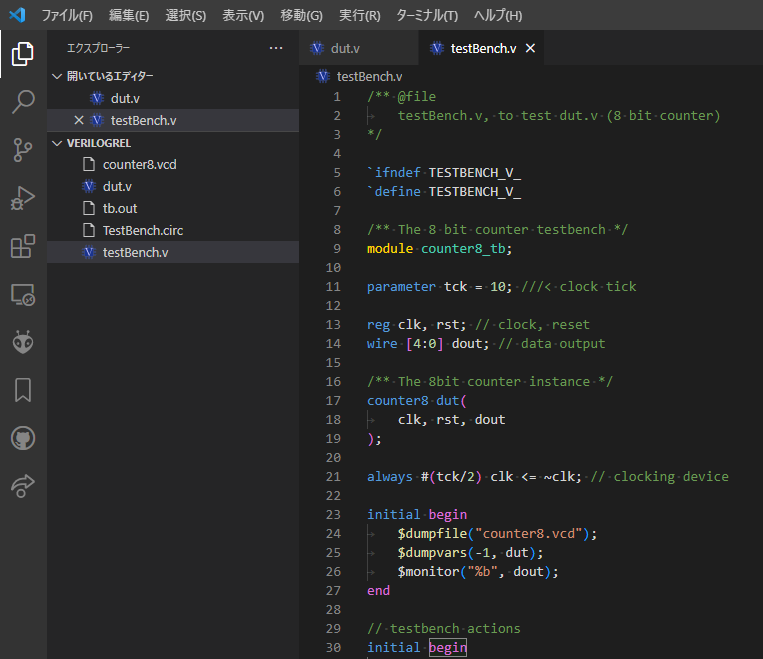

上記 dut.v と、上記のモジュールを駆動するための testBench.v (冒頭のアイキャッチ画像にみえとります)が出来たらば、以下の手順にて、シミュレーション結果をwave表示できます。

$ iverilog -o tb.out testBench.v dut.v $ vvp tb.out $ gtkwave counter8.vcd

VSCode上からもプラグインのお陰で右三角ボタンを押せばエラボレート&Goできることは確認済です(まだ波形表示は出来てません。)

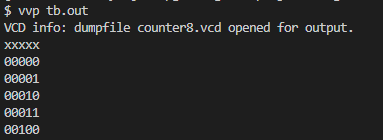

vvpで、シミュレーションしているところが以下に。画面表示と並行に裏でvcdファイルが作成されとります。

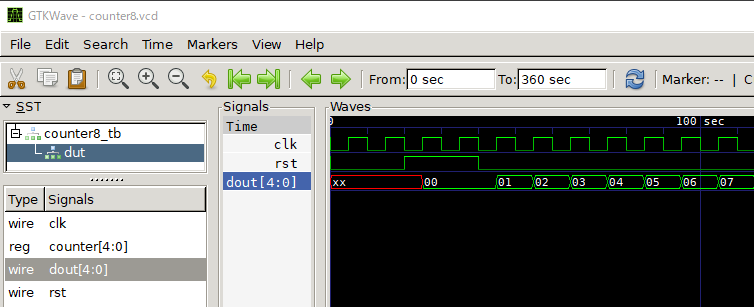

GTKwaveの波形表示画面です。

カウンタしているみたいです。

まあ、Logisimの環境とVerilogの環境を並行して動かしていきたいと思います。冗長なお楽しみ。