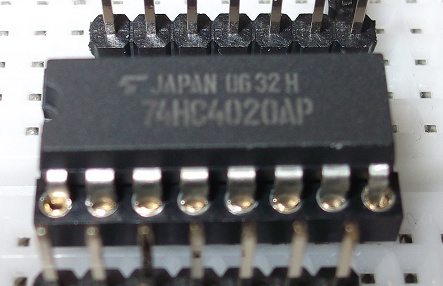

別シリーズで「分周器」が必要であったのでTC74HC4020APを購入。いったい74HCシリーズなんだか、4000シリーズなんだかハッキリしろい、という感じのネーミングのデバイスであります。その心?は4000シリーズの同一型番品と端子機能互換だけれども電気的には74HCシリーズ同等ってことかい?知らんけど。

※「部品屋根性」投稿順Indexはこちら

TC74HC4020AP

東芝殿の製品ページが以下に。多分オリジナルは遥か「古代」のCMOS黎明期に遡るデバイスだと思うのでありますが、いまだに愛されて?おるようです。まずはめでたい。

データシート的には14-Stage binary counterとあります。14段、リップルキャリー(下から成り行きでパタパタとフリップフロップが変化していくタイプ。出力タイミングを特定のクロックに同期したりしない)タイプのバイナリカウンタです。

動作は簡単。制御は2端子のみ。

-

- CLR、ハイを入れるとカウンタをリセット

- CLK#、立下りエッジで最下段をヒックリ返す。後は成り行きで伝播

上記2端子と14段の出力と考えると16端子が埋まってしまい、16ピンパッケージではVCC、GNDが収容できませぬ。元々の4020の仕様がそうだったのでしょう。14段もある(分周器)の下の方の出力は使うまい、ということで最下位のQ1の次は2ビット飛ばしてQ4となってます。これでVCC、GNDに上記制御2端子、カウンタ出力が12ビットということにあいなります。省かれた2端子が必要ならば4040使えと、そのかわり12段だと。

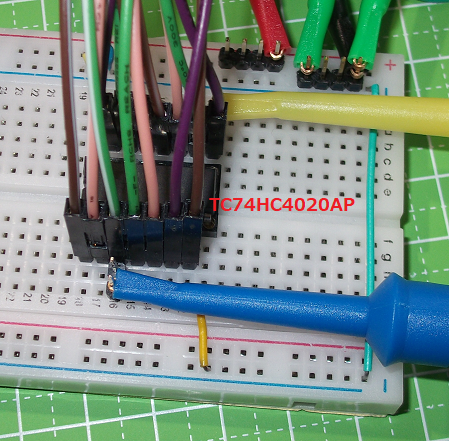

動作確認実験のためにDigilent Analog Discovery2に接続したところが以下に。

動作確認

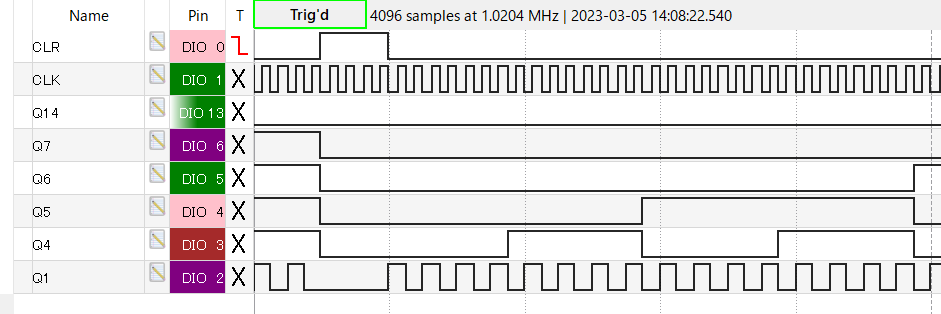

デバイス的には電源電圧5V系でも3V系でもへいちゃらなのですが、AD2のロジックパターンジェネレータの出力電圧が3.3Vなので、電源電圧は3.3Vに設定いたしました。CLR信号にハイパルスを一発、CLK信号を動かしつづけて、AD2のロジアナ機能(Analog Discovery2といいつつ、デジタル信号も観察できるのです)で観察するとこんな感じ。途中のビットが多いので端折りました。

CLKからみると、Q1出力が2分周、4分周と8分周の端子は省かれており、次のQ4端子が16分周ってことかい。その先Q14にて16384分周とな。

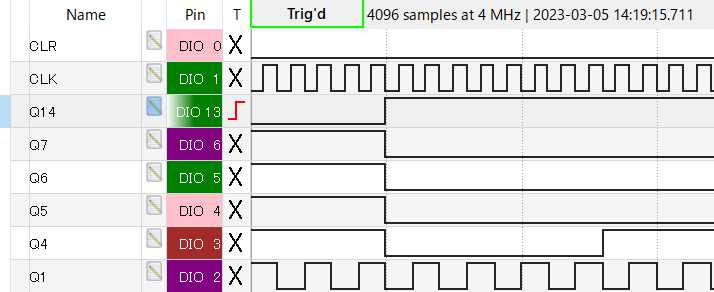

Q14が動くのはCLR信号から遥か先なので、ちょいと設定をいじってQ14がカタリと動くところを観察してみました。拡大するとこんな感じ。

「リップル」している筈なのだけれども、上のロジアナ波形では観察できませぬな。

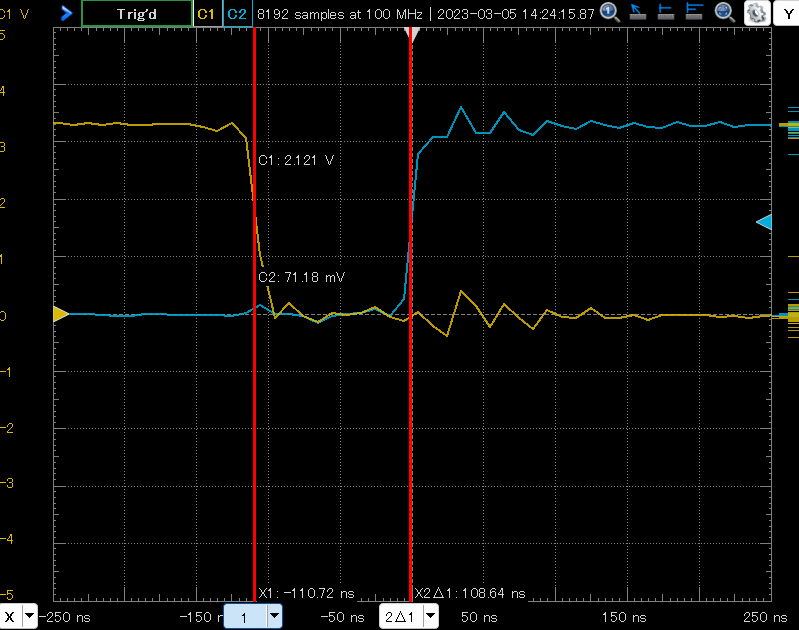

そこでQ1出力とQ14出力をオシロで観察いたしました。最後はアナログです。黄色C1がQ1、青のC2がQ14信号です。Q1の立下りからQ14の立ち上がりまで「リップル」が伝播するのに約108n秒かかっておるようです。

データシート的には、初段(CLK端子からQ1)を除き、Q1からQ14の各段の伝搬遅延時間は、標準5ns、最大14ns(ただし@Vcc=5V、25℃)であります。108÷13=8.3nsecなので、データシート的にはOKか。ま、だいたい。

これで分周できるな。といって何分周するのだか決めてないのだけれど。。。肝心のことを考えてないな、自分。