Dフリップ・フロップを数珠繋ぎにすればシフトレジスタになる、とLTspiceの”dflop”を並べてみたらば挙動がオカシイです。あれれ、クロックの立ち上がり一発、並べたdflopをデータが一気通貫、クロック毎にシフトしてくれないのよ。調べてみたらば原因は簡単。デフォルトの遅延ゼロ。ちょいと遅延を与えたら解決。トホホ。

※「SPICEの小瓶」投稿順インデックスはこちら

LTspiceのDigitalコンポーネント

LTspiceにも論理ゲートのコンポーネントがあり、以下のDigitalというフォルダから選択することが可能です。

よく使いそうな論理ゲートは、だいたい網羅(極性とか考えるとも少しバリエーション欲しいけど)してます。これ使えば簡単なロジック回路は勿論、ロジックとアナログの混在回路のシミュレーションなども出来、便利。ただし注意しなければならないのは、ここに含まれている「コンポーネント」どもは全て

Behavioral

な回路だということ。理想、いや純粋? 例えば電圧。こいつらのデフォルトでは論理0はGND、論理1は1Vです。現物回路的な動作に近付けるためには、いろいろと設定に味付けが必要じゃと。

D-Flip Flop (dflop)

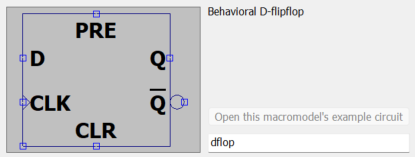

さて今回の「お間抜けシミュレーション」の対象になったコンポーネントが dflop です。Dフリップ・フロップね。データを保持してくれるやつ。シンボルが以下に。

端子の意味は以下のようであろうと推察。

-

- CLK、クロック入力、立ち上がりエッジでDの値を保持する

- D、データ

- Q、保持している値

- Qバー、保持している値の反転

- PRE、プリセット、ハイ入力で値を1にセット

- CLR、クリア、ハイ入力で値を0にクリア

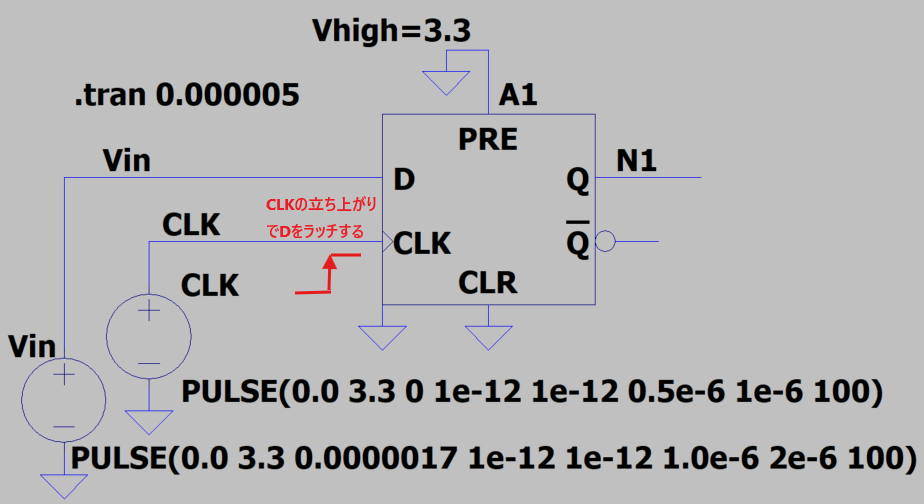

それっぽい波形にするために、dflopのアトリビュートからSpiceLineのところに、Vhigh=3.3を与えてます(通常は非表示ですが、表示オプションにチェックいれてあります。)これによりロジック・ハイのとき3.3V(ローはデフォルトで0V、なお回路スレッショルドはVhight=3.3とすると、(3.3+0)/2=1.65Vってことみたいです。

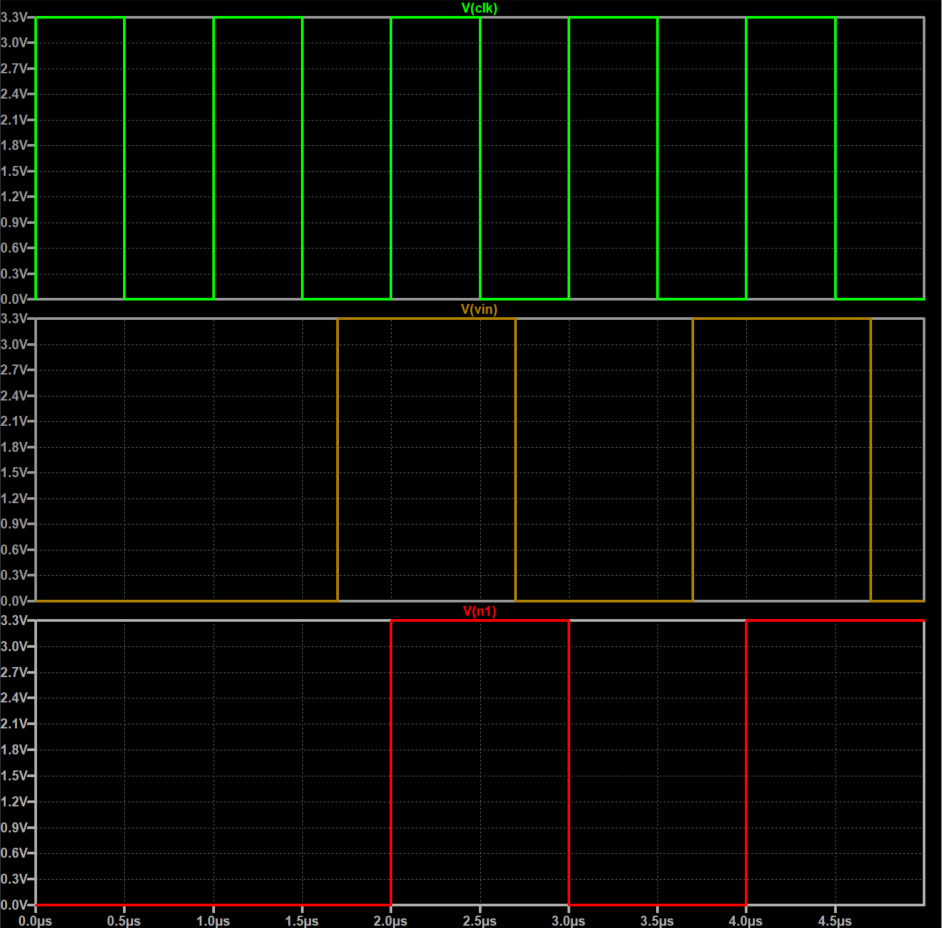

まあ、CLKの立ち上がりのときのDの値をラッチしてくれているね。

シフト・レジスタ動作

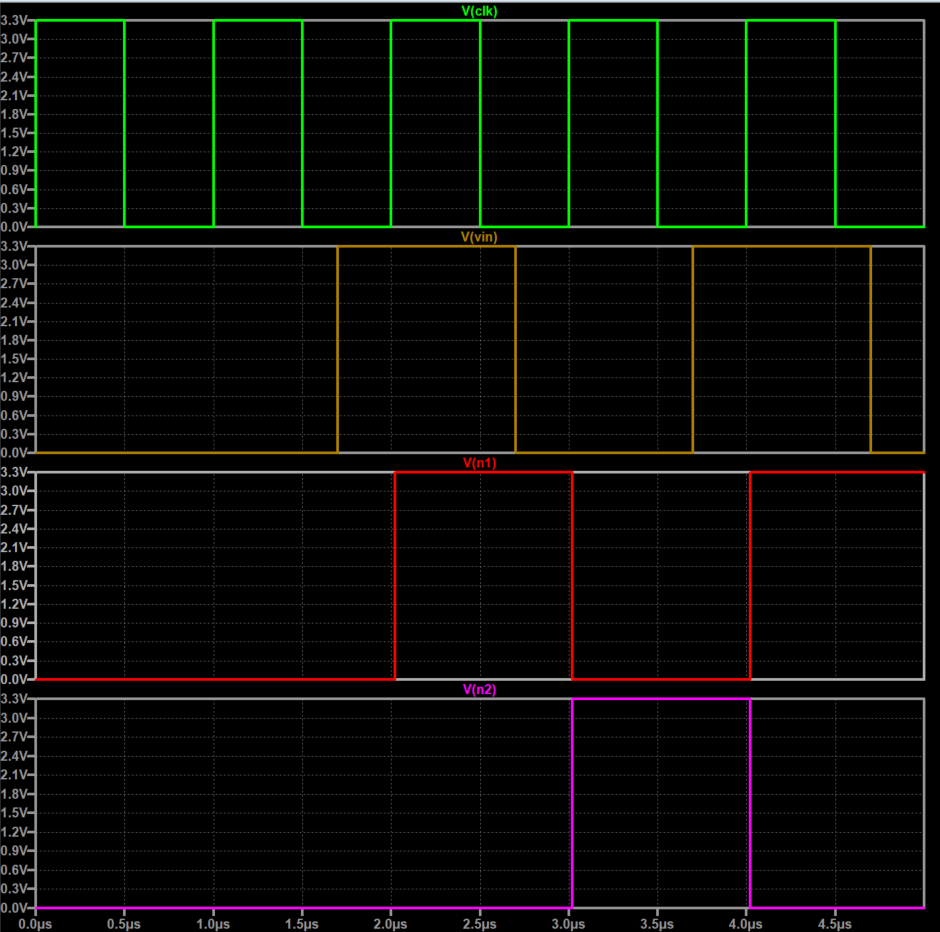

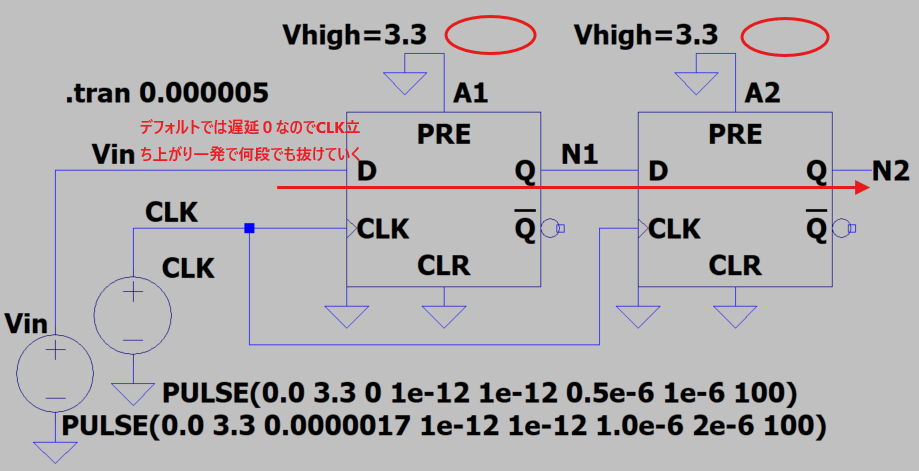

ありがちなシフトレジスタ(2ビットだけれども)を作ってみたものが以下に。 Vhighは設定してますが、他のパラメータはデフォルトのままです。シミュレーションしてみると上の回路に赤字で書きこんだとおり「抜け」ます。こんな感じ。

Vhighは設定してますが、他のパラメータはデフォルトのままです。シミュレーションしてみると上の回路に赤字で書きこんだとおり「抜け」ます。こんな感じ。

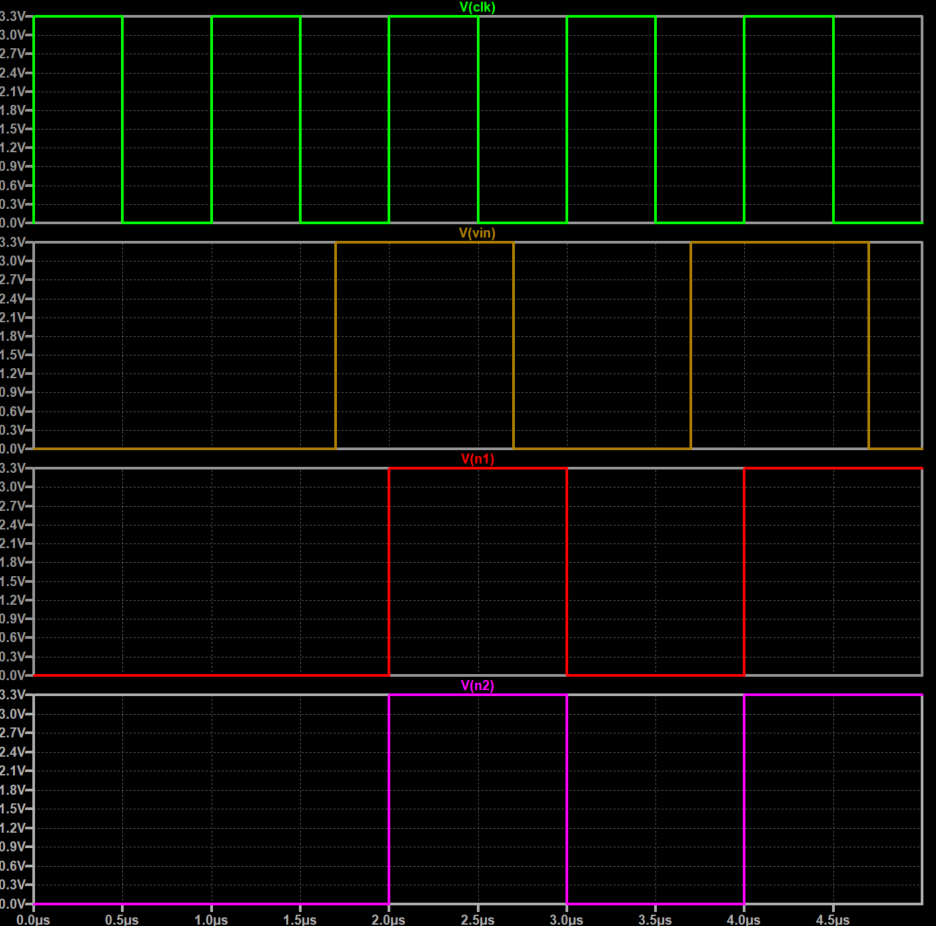

おっと、CLKの立ち上がり一発で、dflop2個分貫通しているよね。そして貫通しているのはまさにCLK立ち上がり時点のDの値。

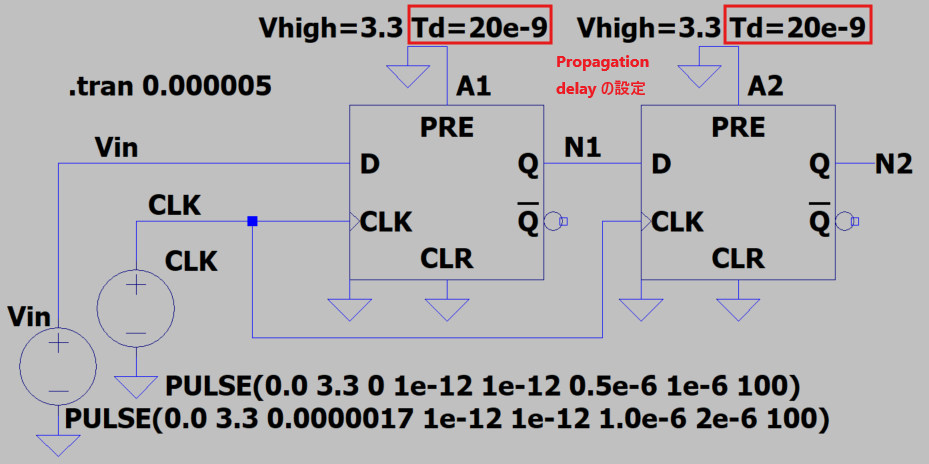

意外な挙動にチョイとたじろぎました。が、それならば伝搬遅延を与えるべしと。パラメータTdはPropagation delayです。

遅延20nSは、手元にあった74HC74Dがtyp 13ns、max 20nsというところから適当に入力です。

おお、ようやく「シフトレジスタ」的な動作になったようです。

Behavioralなロジック・コンポーネントを使うときはパラメータ設定を忘れずにってことかい。