今回から白色雑音(ホワイトノイズ)の発生に入ります。ちょっと問題だったのは手元にゲートレベルの「回路図」から論理シミュレーションする環境が無かったという件。今時「回路図」書いて「論理」でもないものな~。しかたがないのでアナログシミュレータのLTspiceで論理シミュレーションしてしまいました。出来るのですがクセが強い。

※「手習ひデジタル信号処理」投稿順 Indexはこちら

※参照させていただいております三上直樹先生著の教科書は以下です。

工学社『「Armマイコン」プログラムで学ぶデジタル信号処理』

今回は実機もArm社のMbedのWeb環境(要登録、無料)も使用しておりません。なお三上先生の御ソースはMbed環境内で公開されており、「呂」で検索すれば発見できます。

「M系列信号」を使う「白色雑音」発生

今回手習ひさせていただくのは、以下のようなシナリオです。

-

- M系列信号発生器で「疑似乱数列」を発生する

- 上記の乱数列を低域通過フィルタに通して帯域制限する

これで白色雑音が得られると。

M系列、Maximum length sequenceは通信系では定番で、私も何度かお世話になったことがあります。LFSR (Linear Feedback Shift Register)、線形帰還シフトレジスタ使って0/1の疑似乱数列を発生するもの(今回は0/1でなく、ー1/1の列のようですが。)

LFSRそのものはCのコードで簡単に書けます。しかし、やっぱり、ということで三上先生も、DフリップフロップとXORの「回路」でご説明をされとります。私も同感であります。

そこで三上先生がお示しになった 「MSeq16クラス」の回路図をまずは動かしてみよう、としてハタと困りました。手元にゲートレベルの論理シミュレーションできる処理系の手頃なものがないです。

HDLで書いたソースではツマラナイ。ということで考えたのはちょいと目的外使用ですが毎度お世話になっているLTspiceを使わせていただく、という案です。LTspiceはアナログシミュレータであるので、これをゲートレベルの論理シミュレーションに使うというのは「牛刀割鶏」的ではあるのです。しかしゲートレベルの論理回路のためのコンポーネントも幾つか用意されているのでそれを使えば論理シミュレーションできそうでした。

LTspiceでの論理シミュレーション

LTspiceで論理シミュレーションするのは初めてだったので面食らうことが多かったです。ちょっと調べて慣れないとよう使い切りません。目立ったところを書き出すと以下のようです。

-

- 全ての論理素子にグラウンド端子がある

- デフォルトでは論理1が1V、論理0が0V。パラメータで変更可能

- 伝搬遅延はパラメータTdで設定可能

グラウンドの件などは衣の下のアナログシミュレーターが見えている感じですな(嫌いじゃないです、この感じ。)

ま、ただ、今回クロック信号を1sが1単位時間みたいなつもりで周期0.5Hzで立ち上がり立下り0.1秒の緩い波形にしてしまったために、DFLOP素子にTdを漏れなく定義しないと「DからQに抜けてしまう」問題が起きました。考えれば当たりまえなんだけれども。

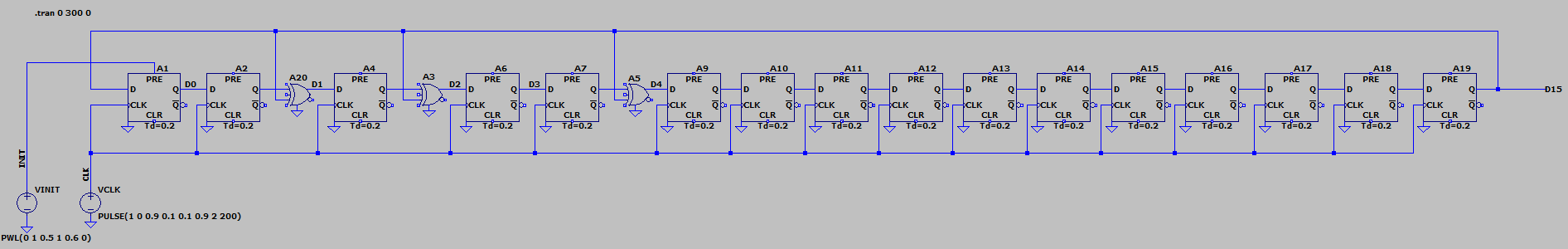

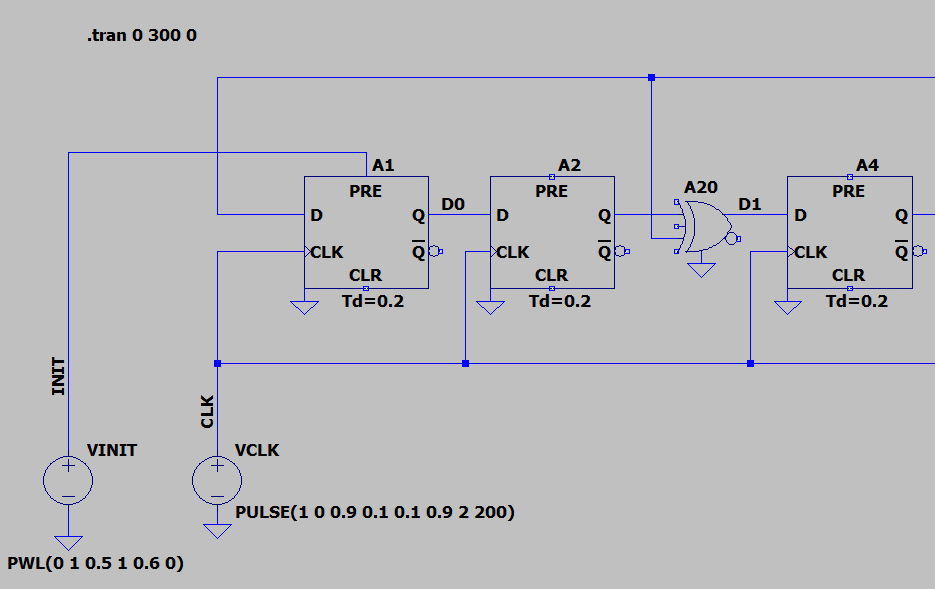

全体像の雰囲気を冒頭のアイキャッチ画像に掲げました。その左端部分の拡大図が以下に。これでシミュレーションの設定が分かるかと。なお、INIT信号は、DFLOPの初期値がオールゼロにならないように起動時に最下位ビットに1を入れておくためだけに使っています。

シミュレーションした結果が以下に。

上側の青色はCLK信号です。それに対して下側の黄緑色は最上位ビット16から出力された「M系列信号」です。まあ乱数に見えるような気がします。ホントは1周期以上動かして自己相関とってみれば確認できるような気もしますが面倒なので省略。

しかし、ゲートレベルの回路図からの論理シミュレーション、昔は普通にやっていたことが出来なくなるものか。この復旧?にも取り組まないといけない気もしてきましたぜ。