別シリーズでゲートレベルの小さな論理回路図の動作を確認したかったのです。HDLからもっと高級な方へ動いている世の中でゲートレベルの回路図の論理シミュレーションなど今は昔?しかたないのでアナログシミュレータLTspiceのロジック使いで切り抜けました。牛刀割鶏。その後なにか無いかとNetを探しまわった結果がコレです。

※「やっつけな日常」投稿順 indexはこちら

その動作確認をしたかったのが、以下の投稿です。

手習ひデジタル信号処理(38) M系列信号を使う白色雑音の発生その1

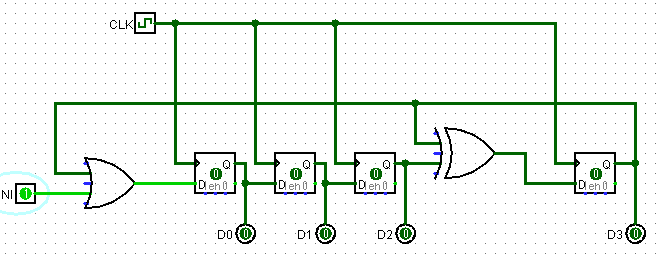

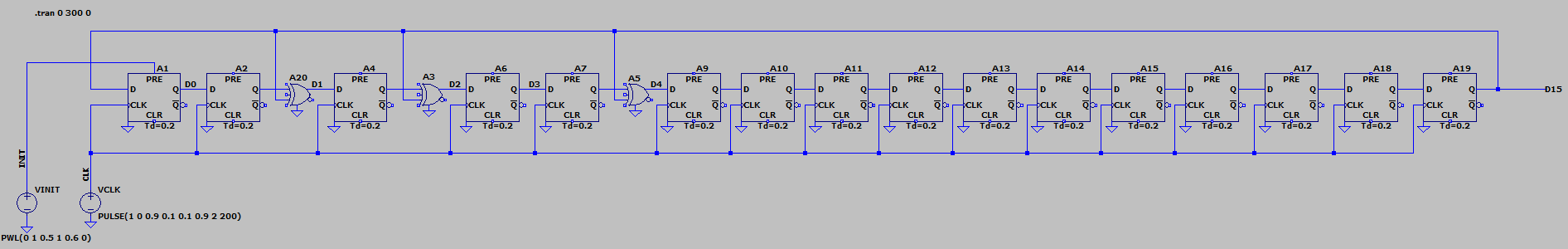

まあ、よくあるLFSRを使って疑似乱数を生成する回路です。Cで書けば簡単ですが、第2回でCのコードは使うので、第1回では、参照させていただいている教科書どおりに回路図でやりたかった次第。仕方なくLTspiceで描いた回路が以下に。

LTspice、実用ツールなので、遅延もあり、SPICEネットリストの出力も可能であります。一応論理デバイスの用意もあるので使わせていただきましたが、ちと目的外使用感があり。。。

ゲート回路図をシミュレーションできるフリーなツールを探す

そこでフリーのツールで、Windows上で利用できる「回路図を論理シミュレーションできる」「軽い」ものを探してみました。せいぜい上のような教科書に載っている典型回路を実際に動かして観察する程度の目標です。

この手のツールを幾つかダウンロードして試用してみたのですがどれも似ています。

-

- 論理設計の実用に供することは考えてない(と思われる)

- よって後段ツールにネットリストを出力する機能など無い

- よってゲート遅延など存在しないか、あっても極めて限定的

- ロジックレベルはせいぜい0,1、あってHiZ(ストレングスどころか、Xすら無かったりする。ほえほえ~)

- 基本ステップ実行、バッチでRunも可程度。

その代わり

-

- 画面上でロジックレベルが移り変わる様を観察できる(教育用途?)

- 一応階層設計に対応しているので、回路的にはスッキリ描ける

Raspberry Pi上のコンテストで賞をとったらしい SmartSim もWindows上で走るのですが操作性がイマイチ(個人の感想です)で却下。

その中で今回選択してみたのが以下です。なお、Logic Friday というツールもあったのですが、論理圧縮の Espresso など内蔵していて、論理シミュレーションというより論理圧縮ツール的なものです。これはこれで面白いのですが、最近はFPGA用の論理合成ツールが全盛なので出る幕ないか。

Logisim

LogisimのWebページは以下です。

ただし、以下1行引用させていただく残念なお知らせが冒頭に書いてあります。

Note: Further Logisim development is suspended indefinitely. [More information] (11 Oct 2014)

既に10年近く前に開発止まってます。まあ、それでもこのツールが良いなと思ったのは以下の理由からです。

-

- 動作が軽快

- 操作方法が分かり易い(HELP内蔵しているがHELPを読む必要もない)

- 意外と高機能(トランスミッション・ゲートとか、メモリ、ALUとかあり)、バンドルも使えるのでちょっとしたマイコンの回路くらい描けそう

- テーブル形式のシミュレーション結果ファイル出力も可能

- インストール不要。Windows上のファイルサイズ 6.8M

ちょっと残念なのは、この手のツールに共通するのですが入力スティミュラスファイルを読み込む機能が無いことです。しかし、LogisimにはROM/RAMのサポートあり、ビットパターンをファイルから読めるみたいなので、ちょっとしたテストベンチ回路を追加すれば実質OKかと。

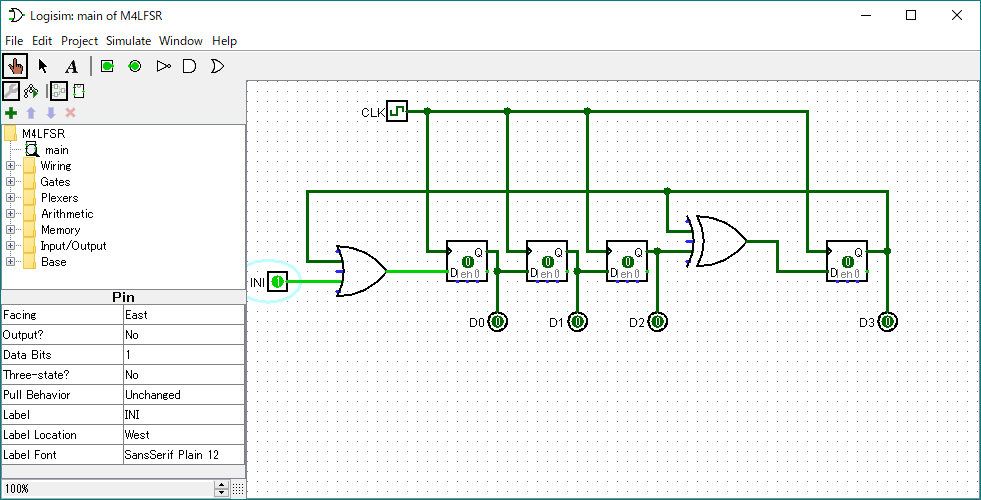

サンプルとして4ビットのLFSR回路を描いていたところが以下に。

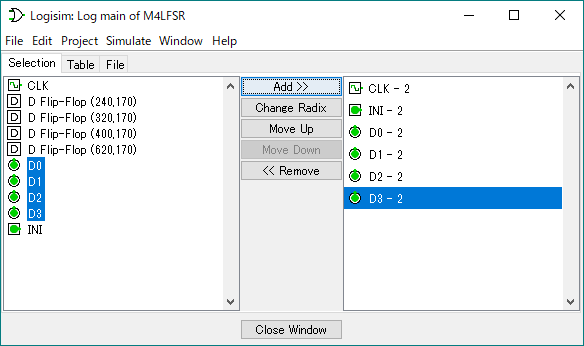

シミュレーション結果を出力するためのLOGファイルの設定ウインドウが以下に。

シミュレーションすれば、画面上でチカチカと回路上の値が色変します。実行レートを早くすると読めなくなりますが、ファイル出力を指定しておけば結果は残ると。こんな感じ。

CLK INI D0 D1 D2 D3 1 1 1 0 0 0 0 1 1 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 1 0 0 1 0 0 1 0 0 1 1 0 1 1 0 1 0 0 1 1 0 1 1 0 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 0 0 0 1 1 1 0 1 0 0 1 1 1 0 0 0 1 1 1 1 0 1 0 1 0 0 0 1 0 1 0 1 0 0 1 0 1 0 0 0 1 0 1 1 0 1 0 1 1 0 0 1 0 1 1 1 0 1 1 0 0 0 0 1 1 0 0 1 0 0 1 1 0 0 0 0 1 1 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 1 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0

LFSRしておりますがな。たまに説明のための回路図などをこれで描いて動かしてみるのはアリかもしれませぬ。後は根気ですな。そこが一番の問題。