前回につづき、AMD(Xilinx)様の「UG945 – Vivado Design Suite チュートリアル: 制約の使用」にしたがって、制約 constraints の設定の練習をつづけてみます。前回は「タイミング制約」でした。後半の今回は「物理制約」です。なにやらコマケーが設計の死命を制する制約が仰山。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

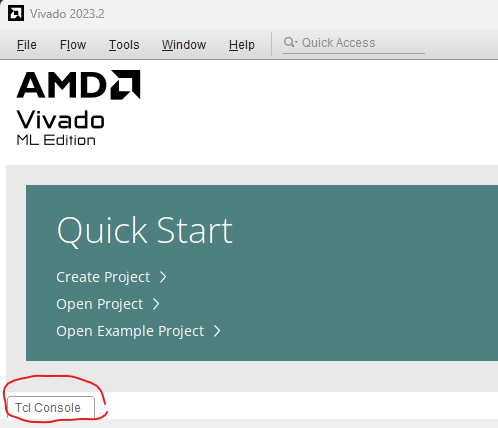

今頃一つ気づいたこと

物理制約の練習に入る前に、今頃一つ気づいた事があるので画像を貼り付けておきます。デスクトップ上のVivado アイコンをクリクリやって起動するGUIの初期画面です。いつも上の方のリンクばかり使っていて全体を見てなかったので気づいてなかったです。左下隅をみると、ほれこのように。

「コンソールウインドウ」自体は隠されているのですが、Tcl Consoleというタブがひっそりとおかれてました。このタブをクリックすればTclのコンソールが燦然とあらわれます。やっぱTCLなのね。

物理制約

今回練習するのは「物理制約」なのですが、その中をざっくり分けると以下のように分けられるみたいです。

-

- セルなどの配置制約

- IO端子の配置制約

- オブジェクトのプロパティの制約

- 設計全体のプロパティの制約

FPGAは膨大なトランジスタを搭載したデバイスです。具体的機能を担う回路ブロックを実際にデバイスのどこに配置するかによって、いろいろ遅延とか変わってくるはず。ただし回路ブロックによってはどこにでも置けるわけでなく、内部の構造により配置可能な場所は限られたりする、みたい。まあ、遅延などゆるゆるな設計(お惚け老人が過去やっているような)であれば、「お任せ」ということでVivado様によきに計らってもらえますが、シビアな設計では設計者が制約を課したいと。また、IO端子の割り当てなどは、外のボードの都合もあるのでVivadoにそれを伝えておかないとなりまへんな。そして、各オブジェクト(回路ブロック)などの物理的設定や、設計プロジェクト全体の設定にも膨大な選択肢があり、出し入れ可能っと。

正直いって、そんな多数の選択肢をFPGA素人の忘却力老人はよう把握できてません。しかし、ま、チュートリアル通りに操作していけば、設定の仕方は学べると。なにをどう設定しているのかは分からんけど。そんなこって良いのか?

配置制約(LOC、BEL)

物理的なCellをどこにどう置くかは、物理制約の華みたいです。歴戦のFPGA設計者の方はテキパキとやってしまうのかも。しかし、お惚け老人はチュートリアルに従って手を動かすのみ。

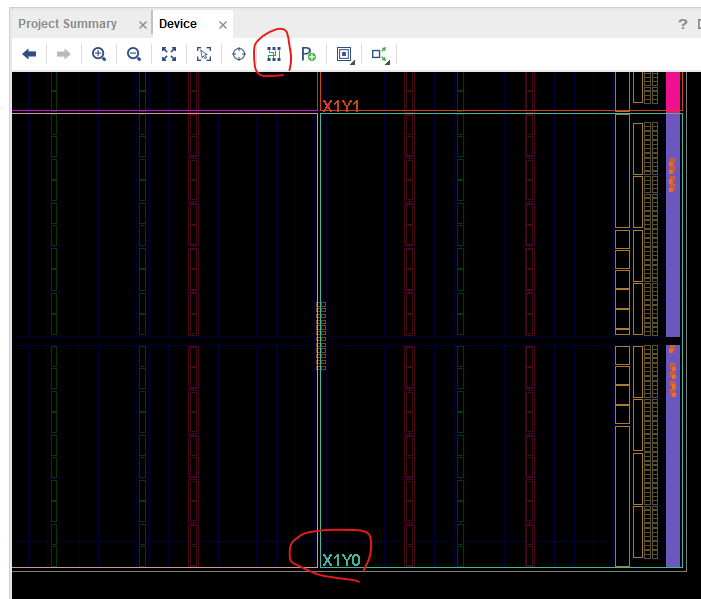

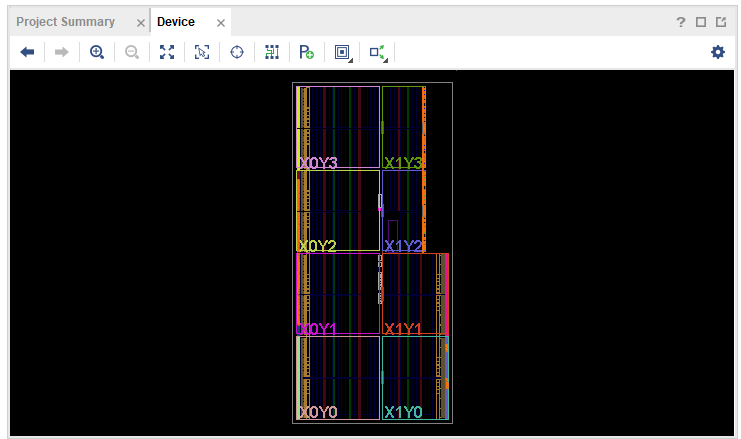

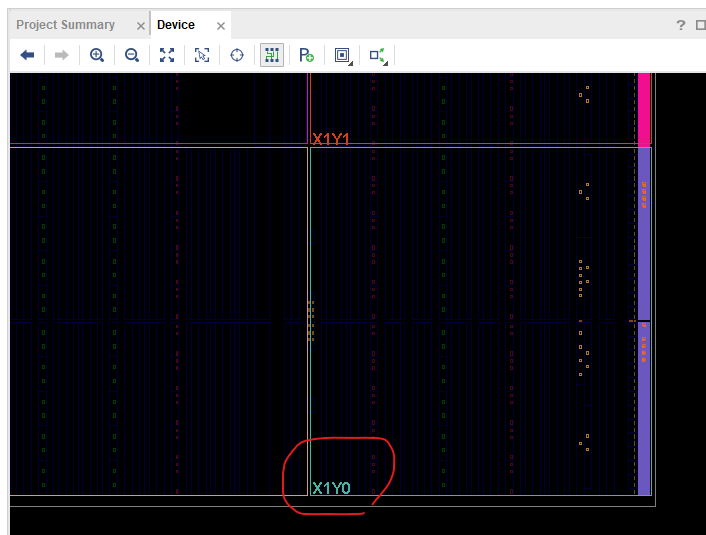

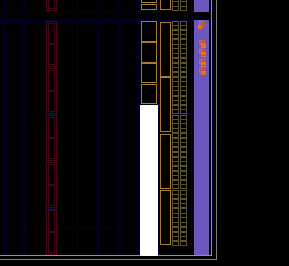

今回ターゲットのOP1200プロセッサのSynthesized DesignのNetlistを開き、Deviceタブを眺めます。

これがチップの全貌なのね。なお、XnYmみたいな大きな箱は、どうもクロックを同じくするモノどもの集まりみたいです。

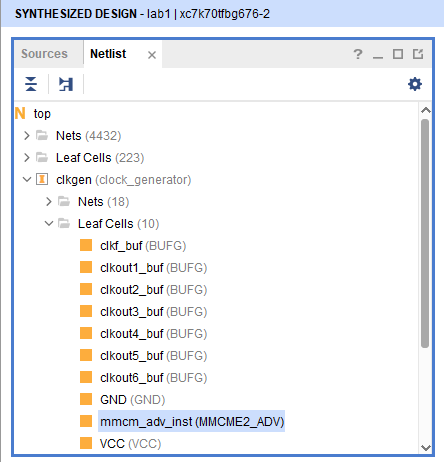

さてここで配置してみる練習用のターゲットは、ネットリストのハイアラーキー上は以下にあるmmcm_adv_instというお名前のLeaf Cellみたいです。

わざわざ題材にされるくらいなので、ちょい「クセ強」でどこにでも置けるような代物ではないみたいです。

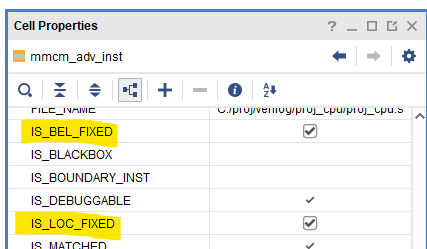

まずは、CellのPropertiesからSTATUSを調べてみます。

上記のように UNPLACEDです。これは特に指定してないので、このままインプリすると「よきに計らってもらう」必要がある状態みたいです。

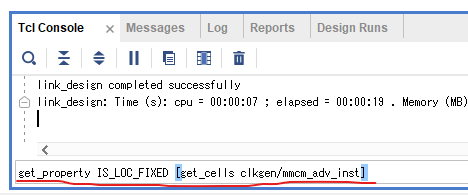

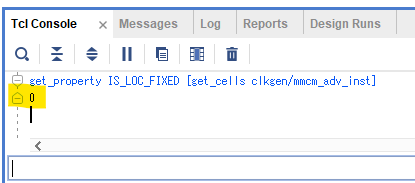

念をいれてTCLコマンドでロケーションが設定されてないことを確認せよ、と。 上記入力した後、コマンド行でリターンすると、結果は素気ないです。0だと。

上記入力した後、コマンド行でリターンすると、結果は素気ないです。0だと。 対象セルはX1Y0という領域に配置すべしとのご沙汰です。X1Y0を拡大(ルーティングリソースは非表示状態)したところが以下に。

対象セルはX1Y0という領域に配置すべしとのご沙汰です。X1Y0を拡大(ルーティングリソースは非表示状態)したところが以下に。

箱どもが現れいでます。

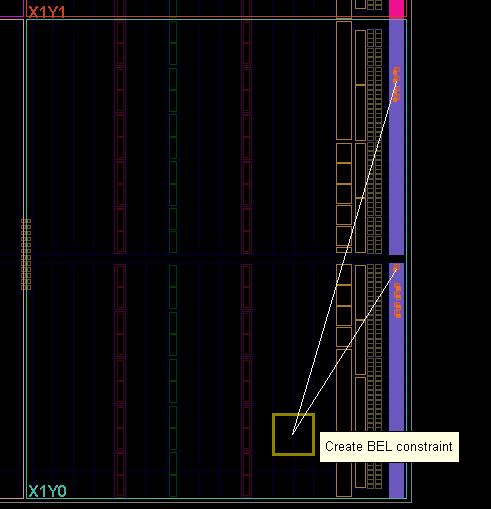

このウインドウに先ほどのNetlistのハイアラーキーからセルをドラッグ・アンド・ドロップできるみたい。ドラッグしているところが以下に。

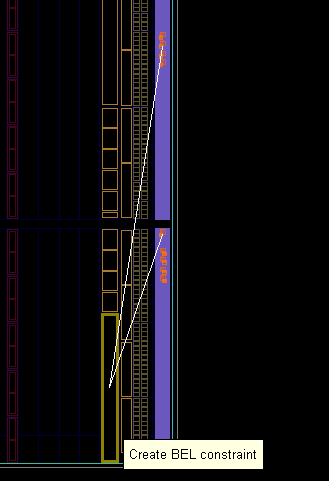

ただし、適当なところでドロップしても反応ありませぬ。「ツボ」にハマったところ(配置可能ということか)に到達するとこんな感じ。

そこでドロップすれば、このように。配置された、ってことかい?

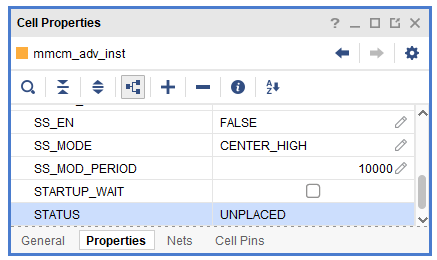

プロパティで確認してみると以前に無かったプロパティが増えている上に、チェックが入ってます。おお 。

。

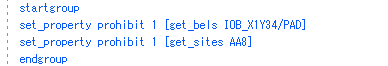

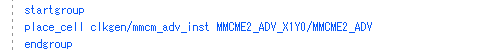

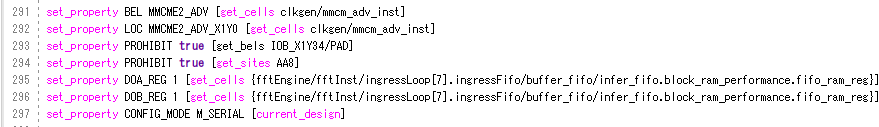

そしてTCLウインドウを見やれば、生成された制約がコマンドになってます。

結局、GUIをクリクリやってできたのは、TCL上ではこれだけなのね~。

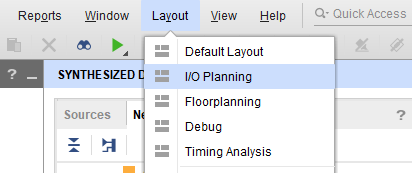

IO端子の配置制約

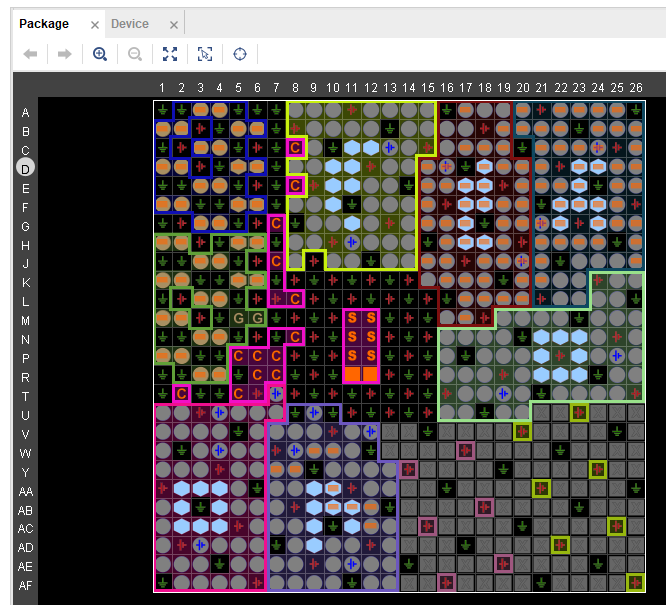

IO端子の配置制約は IO Planning Windowというものを開くところからです。Vivado素人の老人はそれを開くのに戸惑いましたが、メニューみればあったのです。こんな感じ。

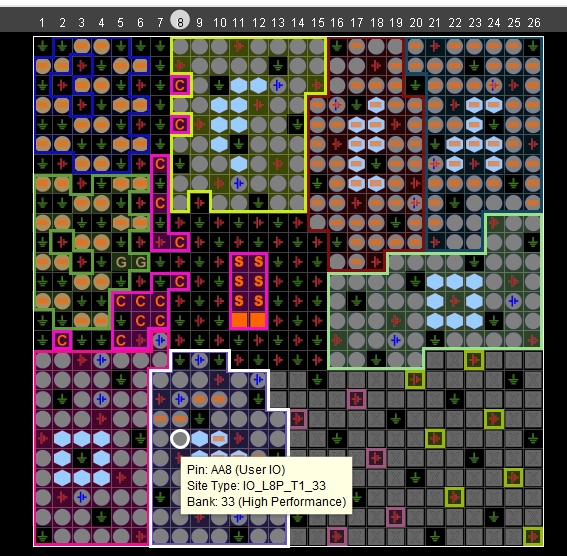

ターゲットFPGAのピン配そのものみたい。沢山ありすぎてようわかりません。

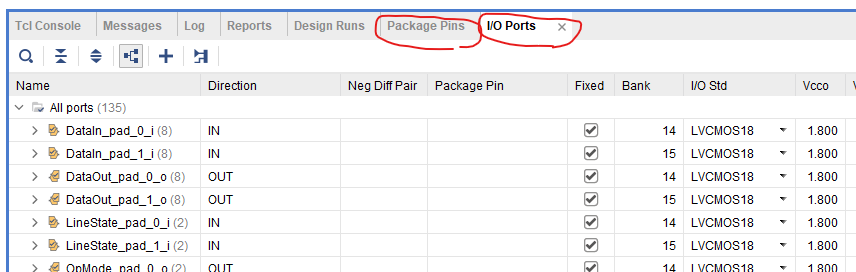

しかし、メインの上のウインドウに気をとられているとひっそりとテーブル形式のウインドウが下の方に2つも同時に開いていることを見落としそうです。

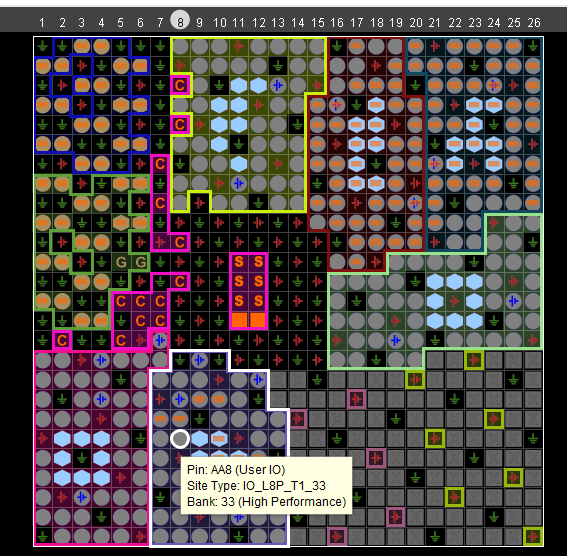

さて、今度の実習は「AA8」ピンをProhibit指定せよ(「使うな」という理解で良いよね)ということらしいです。AA8ピンはここです。

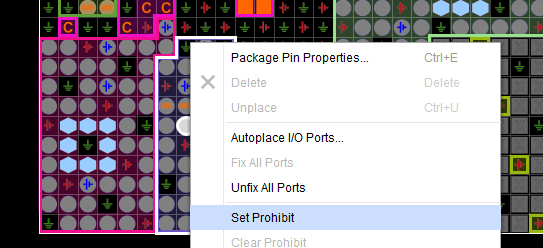

AA8ピンをクリックして選択し、右クリックでメニューを開きます。

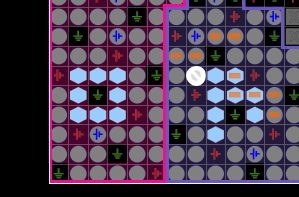

Set Prohibitというコマンドがあったので、それを選択。すると画面は以下のように変わりました。「禁止」アイコン?

オブジェクトのプロパティの制約

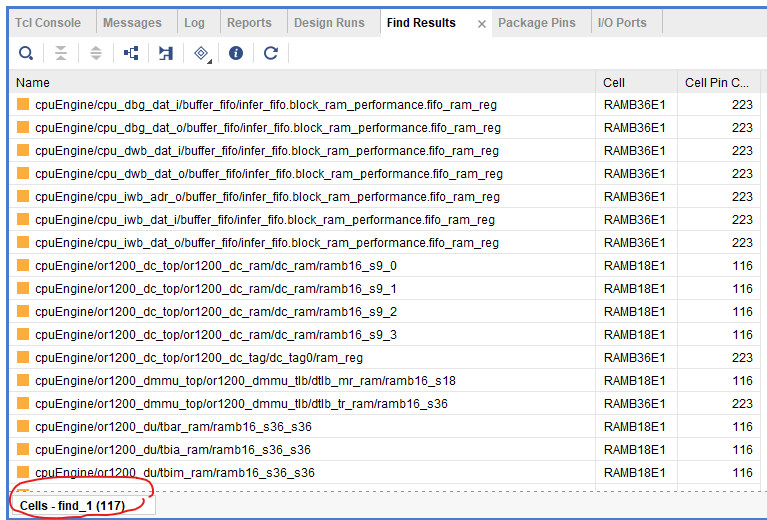

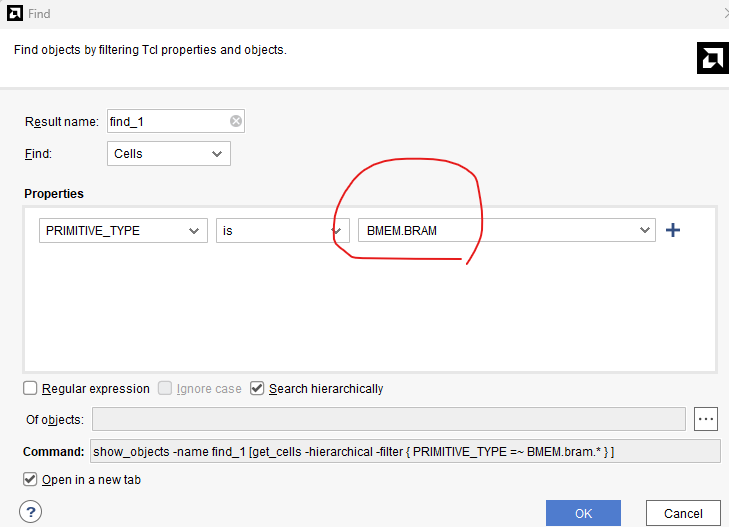

続くは、内部の特定オブジェクトに制約を加える練習みたいです。ターゲットはBRAMというメモリブロックらしいです。多数のメモリブロックが使われているので、ターゲットを探すのにまず、find しろ、ってことみたい。

おいおい、117個もあるじゃん。さらに「虫眼鏡」アイコンで絞りこめと。

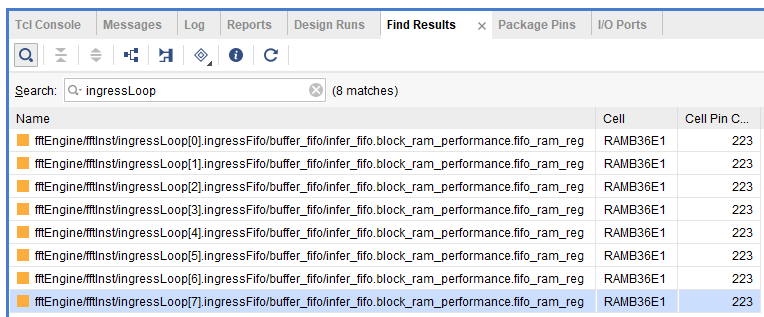

ようやくご指定のブロックとその親族が8個ならんでいるのに行きつきました。ターゲットは[7](つまり8番目の)インスタンスみたいです。

ここで上記のブロックに関する詳細なレポートを作製するために以下のTCLコマンドを発行する必要がありました。

report_timing -from [get_cells fftEngine/fftInst/ingressLoop[7].ingressFifo/buffer_fifo/infer_fifo.block_ram_performance.fifo_ram_reg]

なお、上記をわざわざ1行で書いたのは、TCLコマンドに勝手に改行を紛れ込ませてはならない、からです。途中に改行を入れたいなら以前やったとおり「継続行」としてエスケープしないといけません。お惚け老人はテキトーにコピペして、エイヤーと動かしたら改行が紛れ込んでいてエラーになりました。TCLだね。

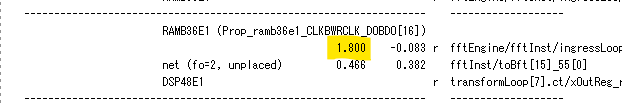

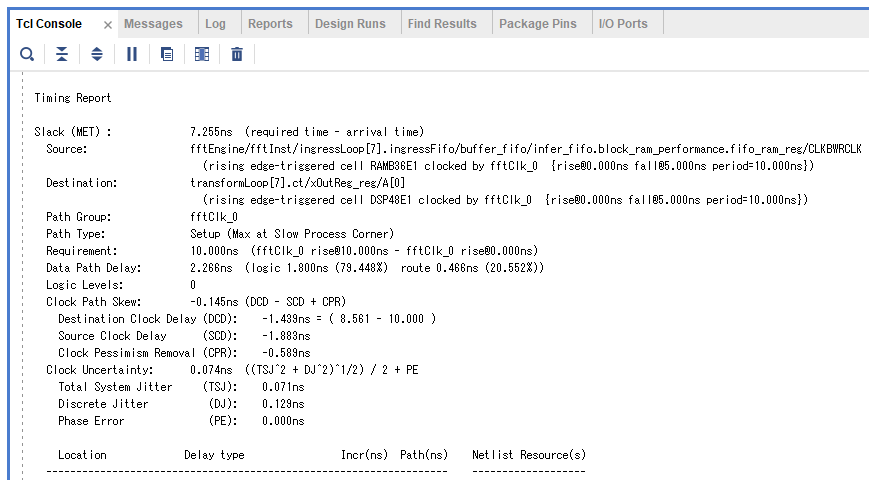

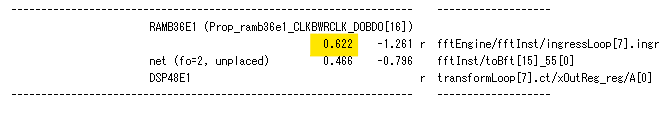

上記の結果は「小さくなったTCLウインドウ」では確認できないくらいデカイです。全画面した上でその先頭部分を取り出したところが以下に。

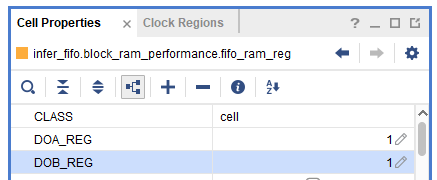

黄色のマーカ引いた 1.800nsが目立つので、これを短縮したいということらしいです。それはPropertyウインドウで以下の設定をするよろし、と。

上記のDOA_REGとDOB_REG、初期状態では0でした。言われるままに、1に変更しただけ。

そして再度上記のレポートを再生成して眺めてみれば、こんな感じ。

確かに短くなっているみたい。

設計全体のプロパティの制約

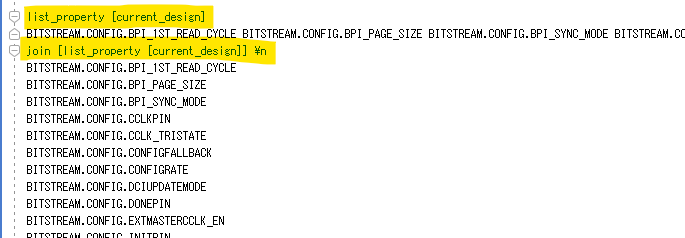

上記は「部品」のプロパティ制約だったですが、設計全体のプロパティもあるみたいです。一覧する方法が書いてありました。

黄色いマーカのコマンドのうち上では、設定されている全プロパティが1個のリスト(1行の文字列)で返ってきます。人間がみるのは不向き。そこでjoinを使って改行で区切れと書いてあります。標準TCLのコマンドだね。やっぱりTCL知ってないとマズイ。

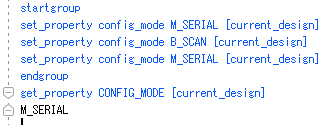

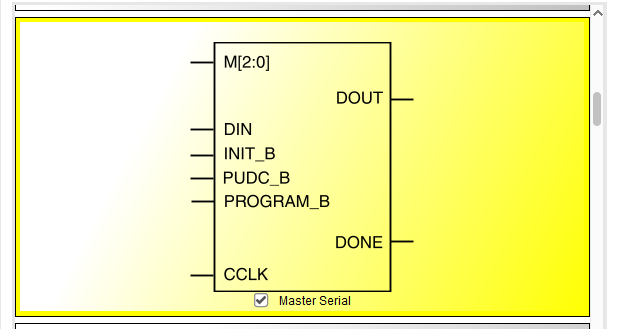

さてこのステップではMaster Serialというものをイネーブルにしておけ、ということらしいです。しかし1点コマケー話なんだが、チュートリアルでは以下のようにつづられてます。

「Mater Serial」

AMD(Xilinx)様の中の人もタイポを見逃すのね。いつも誤字脱字なお惚け老人はちょいと親近感。

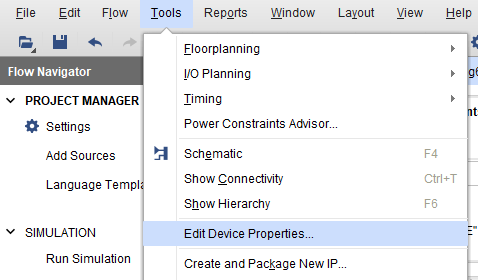

さて、使用するのはまたMenuからのコマンドです。EditDevicePropertiesとな。

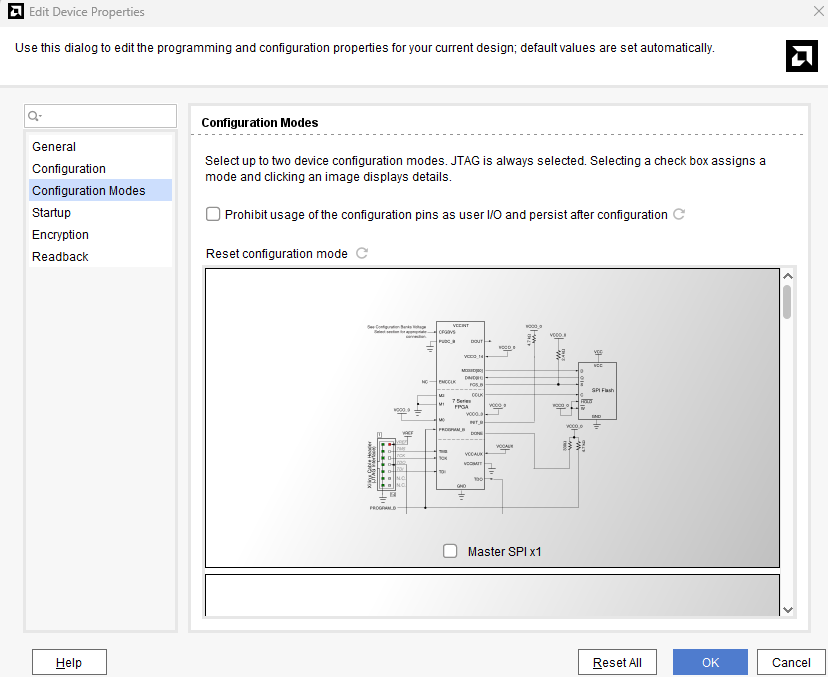

ウインドウを開き、その中で「Configuration Modes」を選択したところが以下に。選択されていない項目は灰色になっているみたい。

ズルスルと下の方を見て行って Master Serialを発見、イネーブルにしたところが以下に。イネーブルにしたら黄色になりました。

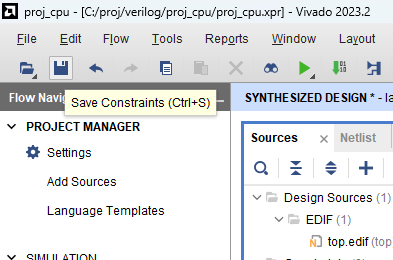

最後にセーブ

設定できたできたと喜んで、ここで閉じてしまうと全てはRAMの上、消えてしまうようです。セーブしないとね。セーブはツールバーのアイコンから。

設定した制約は「アクティブ」に設定されている制約ファイル(.XDC)に書き込まれるようです。エディタで制約ファイルの内容をのぞき見したところが以下に。

GUI使って随分仕事したような気がするけど、TCLコマンドとしたら、こんだけかい。