Vivado2024.1の導入後ボードにビットストリームの書き込みができることが未確認だったので、前回は「初心にもどって」作業実施。書き込みできているみたいです。そこでRISC-Vコアへ再突入かと思いましたが、今回は急がば回れということで「フツーの」MicroBlaze MCSコアで動作確認してみるかと。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

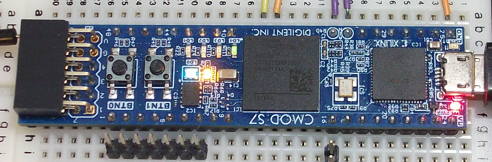

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

「フツーの」MicroBlaze MCSコアにはドキュメントあり

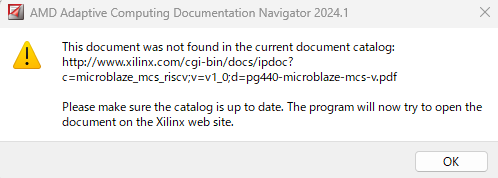

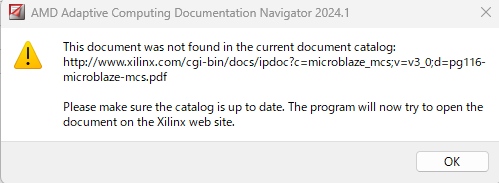

RISC-Vコアの MicroBlaze V MCS を使用しようとした回でぶつかったのが、以下の警告です。

それでもOKボタンを押せば、Web上に探しにいってくれますが、あえなくそのようなドキュメント(PG440~)は無いと拒絶されました。

一方、「フツーの(V無)」MicroBlase MCSの場合も、以下のような警告がでます。

しかし、Web上をあさると、PG116~の方は存在しました。v3.0 それも日本語版ありです。

https://docs.amd.com/v/u/ja-JP/pg116-microblaze-mcs

ただね、上記のドキュメント読んてみたんだけれども、今、お惚け老人が直面している問題を解決してくれそうなことは書いてなかったです。トホホ。

「フツーの」MicroBlaze MCS搭載のビットストリームは書き込める

多分、RISC-Vの方であっても同じだったかと思いますが、今回は

-

- MicroBlaze MCS搭載のビットストリームファイルはCmod S7に書き込み可能(ハードウエアの動作自体はOK)

- しかしVitis側で生成したELFファイルを変換してターゲットのメモリに書き込みするところでエラーとなり、ソフトは動かなかった

です。

忘却力の老人なので、以下さくっと(そうでもないか)手順を書き留めときます。

-

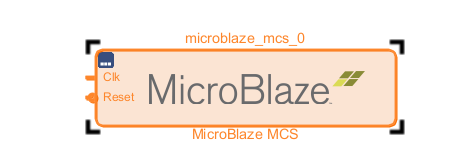

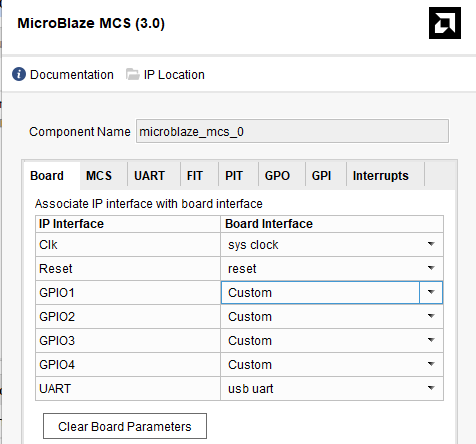

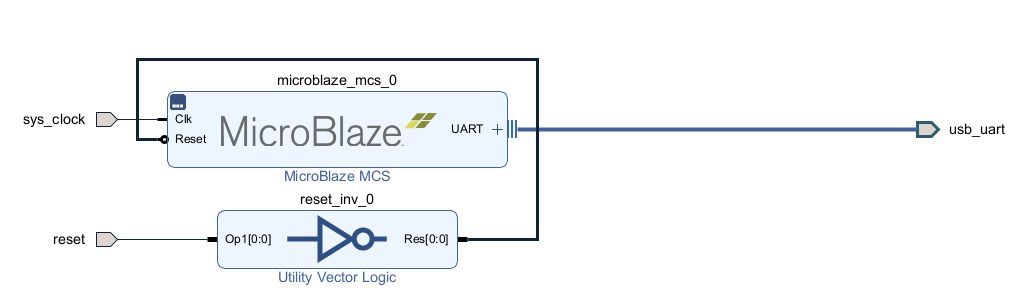

- MicroBlazeコアをAdd IPして設計を始める

-

- 上記コアのプロパティを開いて設定する

-

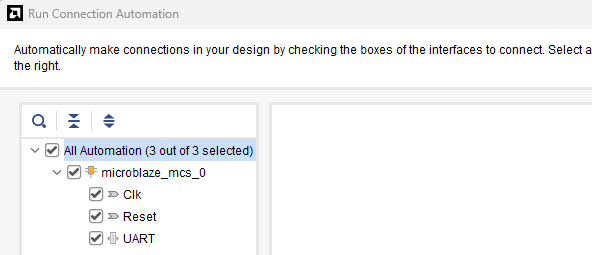

- Vivadoにオートで配線してもらう

-

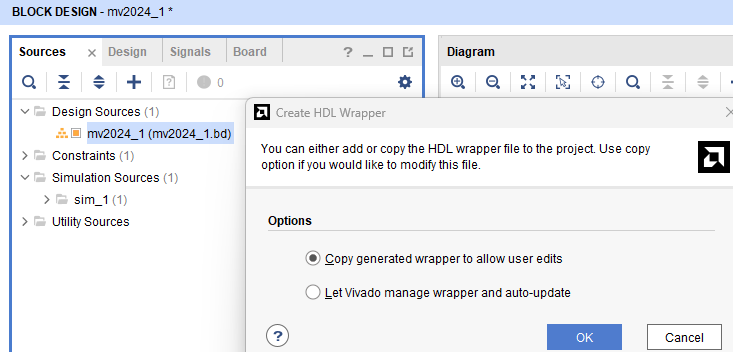

- ラッパを自動生成してもらう。

-

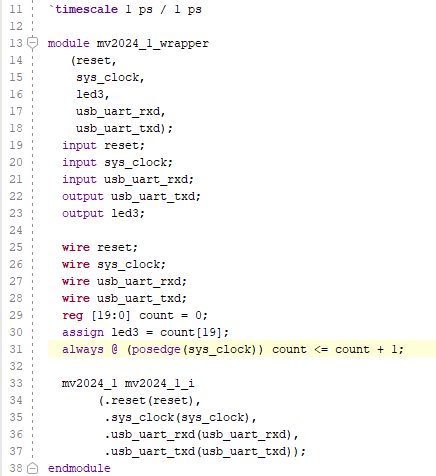

- 生成したラッパソース(Verilog)にお印(ハードLチカ)をいれておく

ちゃんとビットストリームが書き込めて動作していることを、ソフトウエア無でも確認できるように前回もつかった「ハードウエアのLチカ」コードを忍び込ませておきます。こんな感じ。

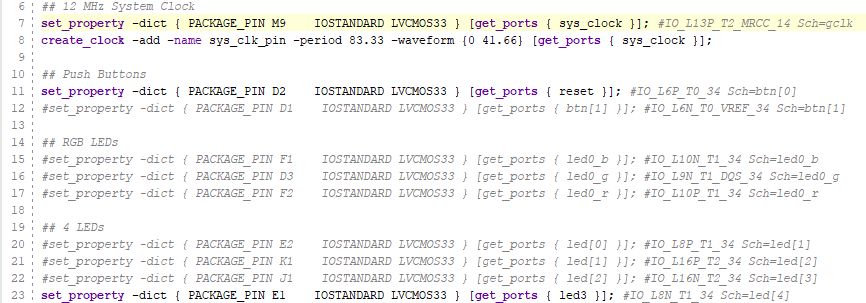

なお、その際、制約ファイルにも変更を。こんな感じ。

-

- ビットストリームの生成、書き込みへ

「AssociateELFの手続き」は行って、シンセシス、インプリ、ビットストリームの生成と走らせました。

中央の目立つ青と赤のLEDの上に、4個ならんだ緑のLEDのうち、一番右の1個が「鈍く」光っているのがハードウエアのLチカのお印です。MicroBlaze MCSコアを搭載したビットファイルの書き込み自体は成功しておるっと。

しかし、Vitis上でELFファイルをビルドして上記に書き込もうとするとエラーになってしまうっと。お惚け老人の混迷は深い。最近そんなのバカリだな、自分。

唯一Vitisからの書き込みがうまく行っているMCSでないコアを使った設計にまでもどってみるかい。。。