前回、FPGA上のRISC-Vコア(MicroBlaze V)を使って「伝統の」Dhrystoneベンチマークを走らせようと試み、「メモリが足りん」と怒られたところで中断。今回は仕切り直しであります。ようやくDhrystone 2.1成功。12MHzクロック、キャッシュレスという質素な構成ではありますが。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

Dhrystoneに必要な構成

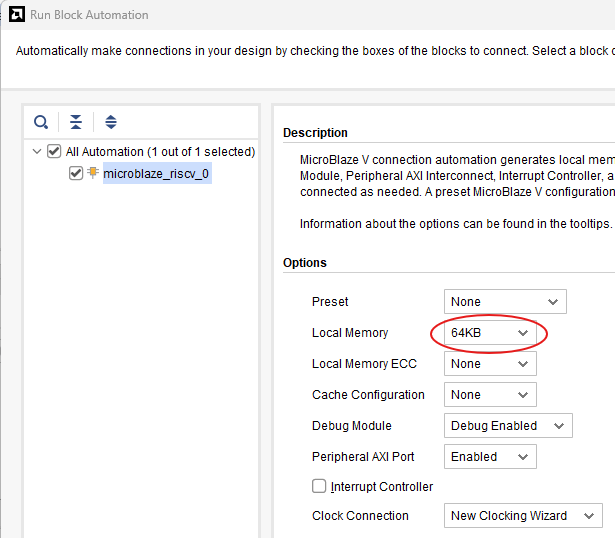

結局、前回の試行錯誤にて、Vitis開発環境のExampleのDhrystoneを実行するためには、RISC-Vのプラットフォームは最低でも以下の条件がみたされてないとならないことが分かりました。

-

- メモリ(命令、データ兼用) 64Kバイト

- 標準出力(printf)に使えるUart

- AXI-TIMER

特に1番は、最初32KBくらいでも大丈夫みたいなメッセージであったので、その気で作ったら、前回の最後で「後4Kバイトちょい足らん」とちゃぶ台返しをくらった因縁?のパラメータであります。まあ、32KBの次は自然な流れで64KBとなりました。流石に今度こそ大丈夫だろ。

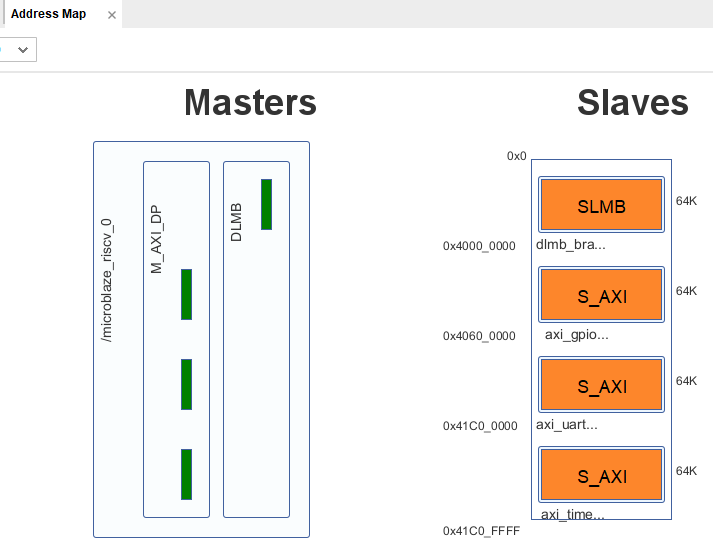

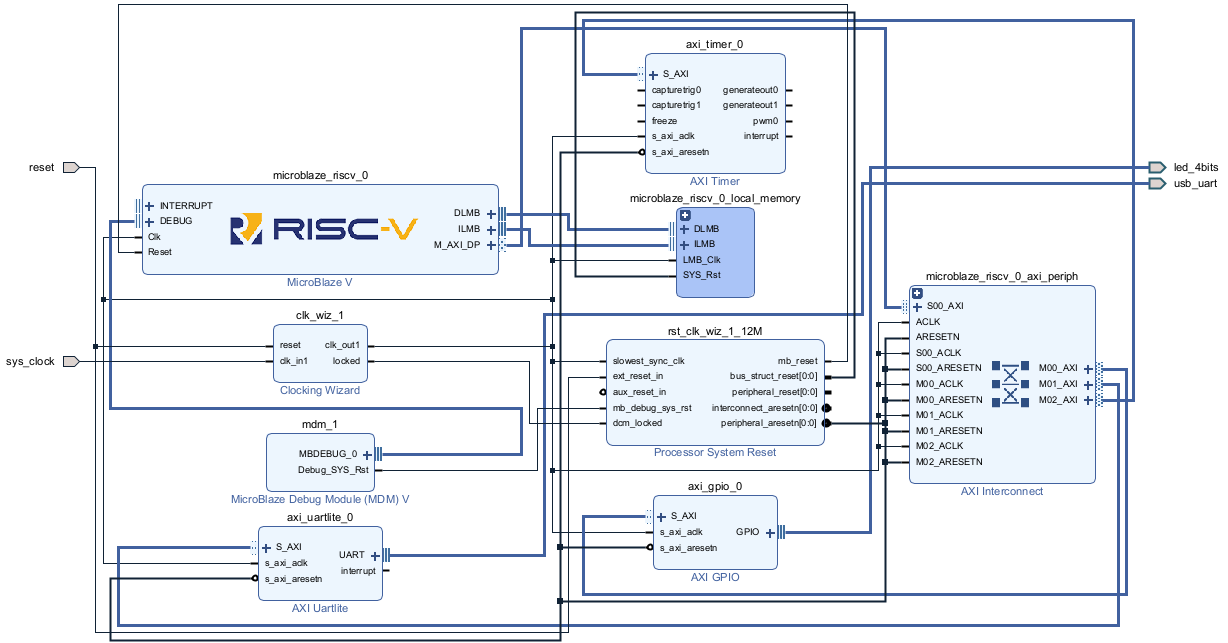

そして上記以外に過去回で使ったLチカ用のGPIOも取り付けてあります。全体像がこちら。

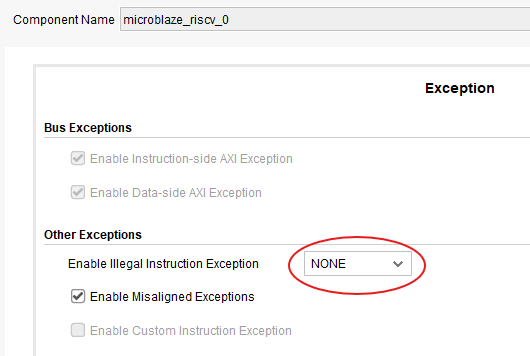

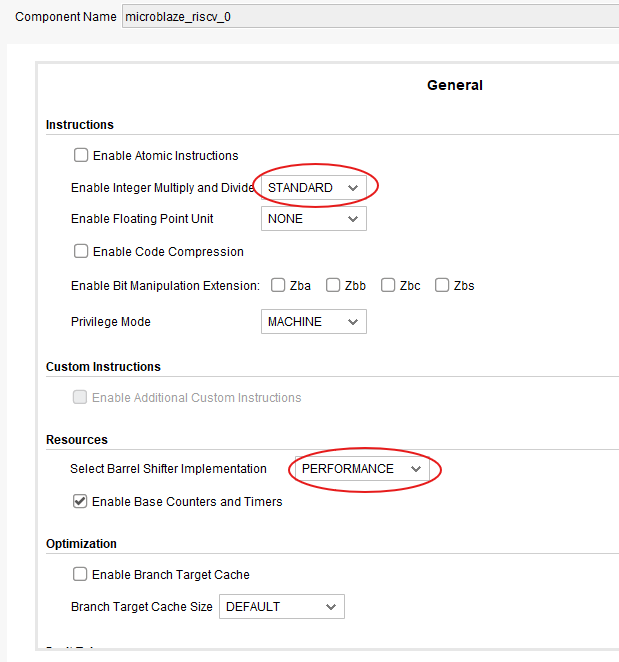

RISC-Vコアの味付け(コンフィギュレーション)のうち、掛け算、割り算、バレルシフタの実装あたりの設定 。

。

Vitis上でのソフトウエアのビルドと実行

上記のハードウエアのビットストリームを含む XSA ファイルをXilinx Vitis へ輸出。まずは Platform プロジェクトを作製、これをビルドしておきます。

その後、Vitisの Exampleプロジェクトの中から Dhrystone を選択、ターゲットのプラットフォームを上記にむけて設定し、アプリケーション・プロジェクトを作製します。

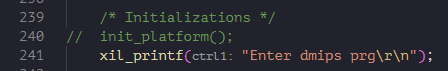

ここでソースをみると2か所、不要というか、あるとビルドが通らないコードをmain()関数内に発見。以下2か所を勝手ながら手動でコメントアウトさせていただきました。

まずはinit_platform()関数の呼び出し。こいつの中でキャッシュを初期化したりしているのですが、今回のプラットフォームにはキャッシュ搭載してません。不要。

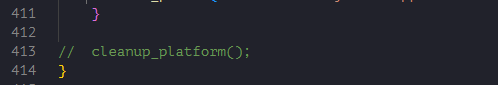

そして上記と対になるcleanup_platform()関数。こいつはキャッシュをディセーブルにする後始末。これまた不要。 多分ね。

多分ね。

さて、アプリケーション・プロジェクトをビルド、ターゲットのCmod S7ボードを接続してRunかけてみます。

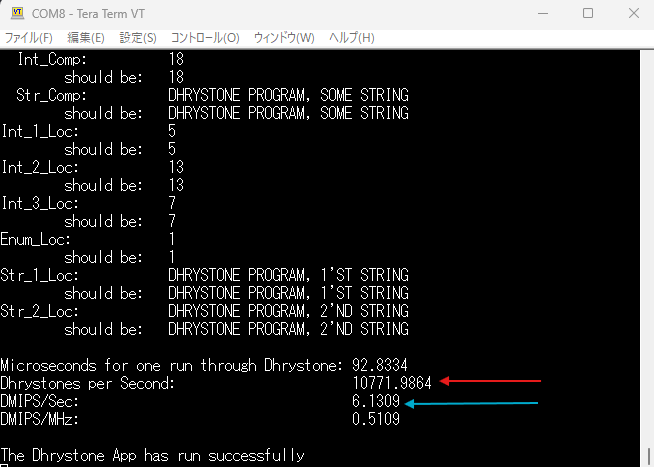

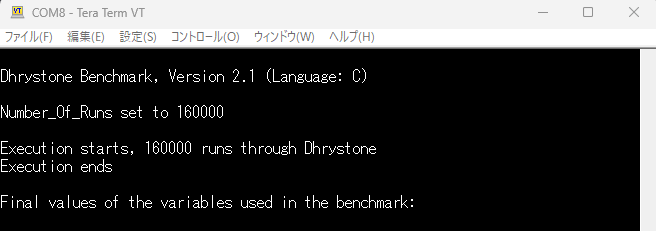

スタートしたところはこんな感じ。ようやく起動した Dhrystone Benchmark, Version 2.1がまぶしいっす。

なお、仮想端末の行末コードは「LF」設定にしておくのがよい感じです。

赤矢印のところの 約10772というのが、この12MHz(キャッシュなし)のRISC-Vシステムの「ドライストーン値」です。そして青矢印が、「いわゆるドライストーンMips値」ね。お化粧など皆無のほんわかした性能っす。

ハードウエアプラットフォームのユーティライゼーション

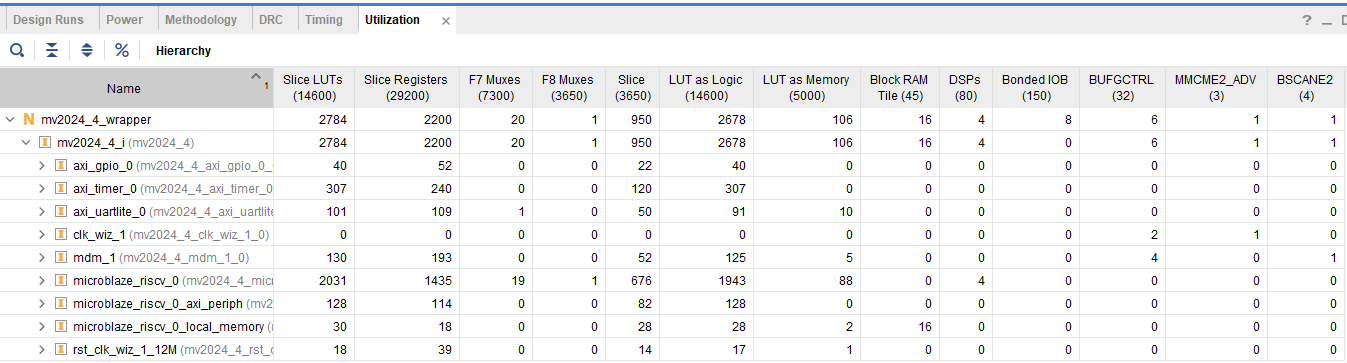

このときのハードウエアプラットフォームがFPGA上のどの程度のリソースを食っているのが気になったので、Vivadoへ戻って調べてみました。こんな感じ。

ギリギリまでFPGAのリソースを使おうなどとは思わないお惚け老人ですが、まだまだ余裕じゃね。ちょこっとブロック追加して動かしてみるくらい出来そうな。ホントか?