前回、RISC-V(MicroBlaze-V)のコアの設定画面、各チェックボックス、プルダウンメニューの一つ一つに神だか悪魔だかが宿っておるということで調べてみました。その中でも大物といえばFPUデス。小さなSpartan-7 FPGAに収まるのかどうかちょいと不安だけれども追加してみましたぞ。追加するだけなら簡単。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

MicroBlaze-VのFPUオプション

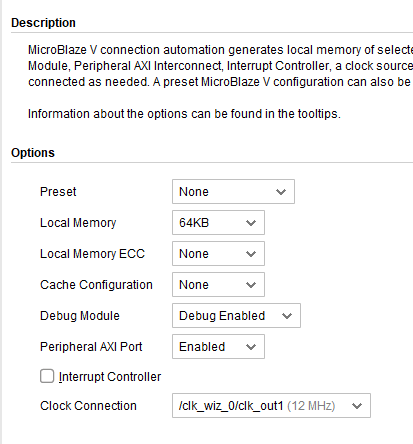

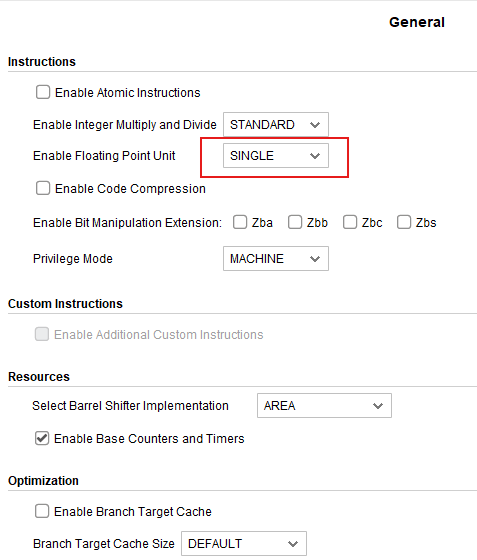

FPU(浮動小数点計算ユニット)をコアに加えるのは簡単です。Microblaze VプロセッサIPの設定画面の2ページ目の以下の赤枠のプルダウンメニューから「SINGLE」を選択すれば、RV32F、単精度の浮動小数点命令群が追加されるようです。

手元のVivado環境ではDOUBLE(RV32D)という選択肢は存在しませんでした。まあ、ちんまい組み込み用途なら単精度計算できれば御の字と。なお、RISC-VのFPUは、質素倹約を旨としているRISC-Vなので演算は加減乗除に平方根、そして積和演算命令のサポートであります。変な命令(超越関数など)はありません。まあ普通。

FPUが必用とするリソース量

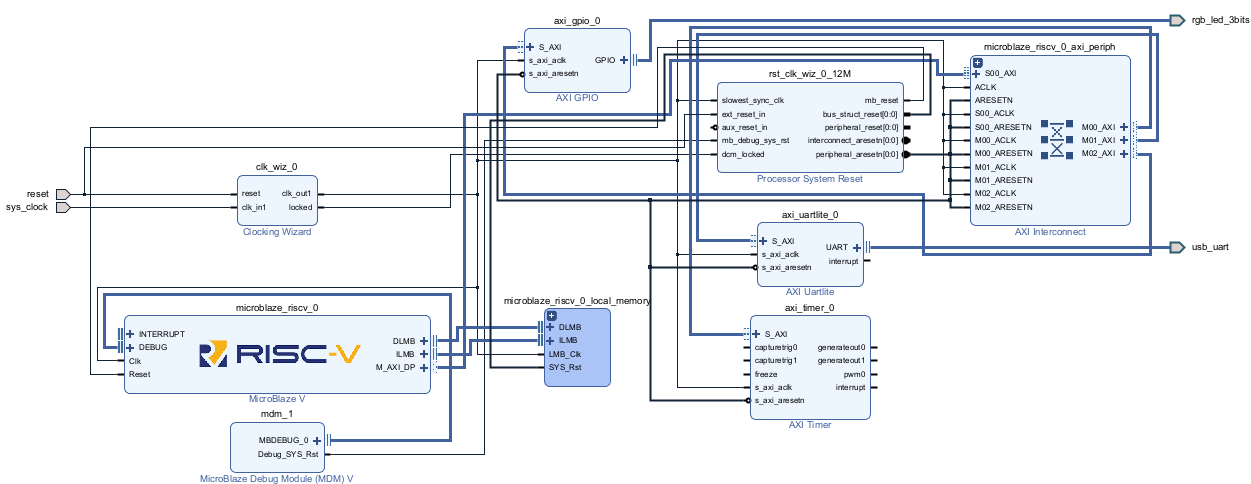

貧乏な老人としては、FPUが必用とするリソース量が気になって夜も眠れません。まあ、実際に作ってみれば分かると。そこで組み立てたブロックダイアグラムが以下に。

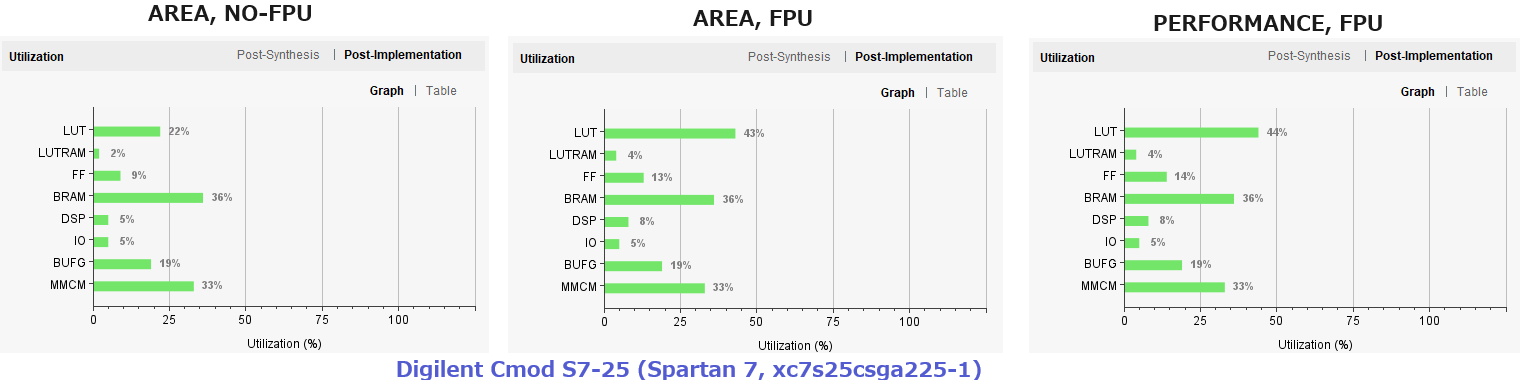

上記設定にて、以下の3つの構成でシンセシス、インプリメンテーションを行ってみましたぞ。

-

- FPUなし、AREA優先設定(3ステージパイプライン)

- FPUあり、AREA優先設定(3ステージパイプライン)

- FPUあり、PERFORMANCE優先設定(5ステージパイプライン)

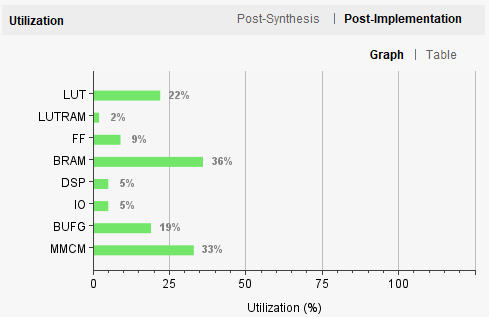

タイミング・エラーなど出ているのですが、そこは踏みつぶしてしまって、作成されたインプリ結果をVivadoにグラフ化してもらったものが以下に。

-

- FPUなし、AREA優先の場合

これは以前にもやった設定です。総LUT量が14600の小さいFPGAがターゲットなのだけれども整数コアだけならかなり余裕。

これは以前にもやった設定です。総LUT量が14600の小さいFPGAがターゲットなのだけれども整数コアだけならかなり余裕。

-

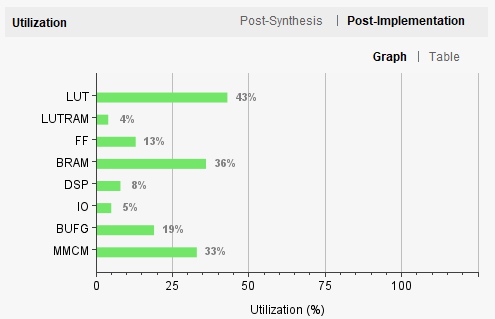

- FPUあり、AREA優先の場合

FPUいれたら、ほぼほぼ倍増って感じでしょうか。でもま、ハシボーでもないです。これがSpartan7、xc7s25cの底力か?知らんけど。

-

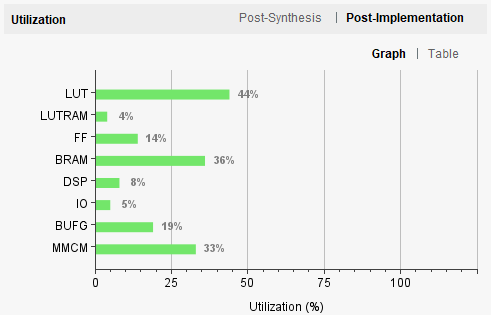

- FPUあり、PERFORMANCE優先の場合

FPUを使う場合(整数コアでソフトウエア浮動小数点しないってこと)、処理速度にコダワリありということですな。その場合、AREA優先というのはおかしくないかい。前回調べた通り、Microblaze Vは4種類の実装を提供してくれているので、その上から2つめ、5段パイプラインのPERFORMANCE優先にしたものが以下に。

これみると、ビミョーにLUTとかFFの使用量増えているけれども、大したことねえっす。PERFORMANCE設定でいいんじゃね。