前々回、RISC-V(MicroBlaze-V)コア(12MHz)の中でタイミングエラーでお悩み。前回試みに「より速くてデカいFPGA」に100MHz実装。タイミングエラー消滅。やったね。でも念のため元のFPGA(Spartan-7)で100MHzクロックを試してみました。あれよ、ノーエラーじゃあーりませんかあ。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

念のため100MHz動作をお試し

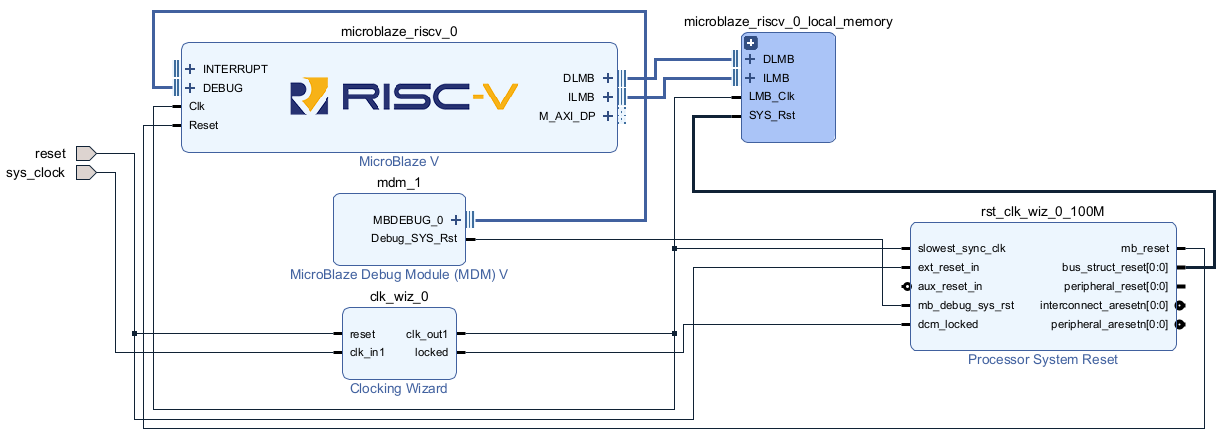

手元のCmod S7ボード(Spartan-7、xc7s25csga225-1 FPGA搭載)ターゲットにXilinx社のMicroBlaze-Vコア(RISC-Vのソフトコア)を実装、そのときのクロック速度は12MHzです。しかし、内部にタイミングエラーがでていてFPGA素人老人は途方にくれました(まあ、実機に書き込めば動くんだけれどね。)

その対策として素人老人はクロック速度を「落とす」方向で試行。10MHzにクロック速度を落とすとちょいと改善する雰囲気があったのです。ただ、あいにく「クロック・ウイザード」様におかれましてはミニマム周波数があります。それ以上落とし切れませぬ。かといえ諸般「クロック・ウイザード」で「よきに計らって」もらっているので使わないのはムツカシー。

どうしたものかということで、手元にはないのですが「ちょい良いめの速くて容量もデカいFPGA」にターゲットを変更、デフォルトの100MHzで実装してみたらばノータイミングエラーね。やっぱ「お足」の問題?金が全てか?

しかしちょいと気になるのが「クロッキング・ウイザード」様のデフォルト値が上記の「良い目FPGA」でも元々のCmod S7ターゲットでも100MHzであること。ダメ元でCmod S7ターゲットでも100MHzを試してみました。

RISC-Vのコアは、PERFORMANCE設定。それ以外はデフォルトのまま(乗算器なども使用なし)です。メモリも16Kバイトとミニマム。

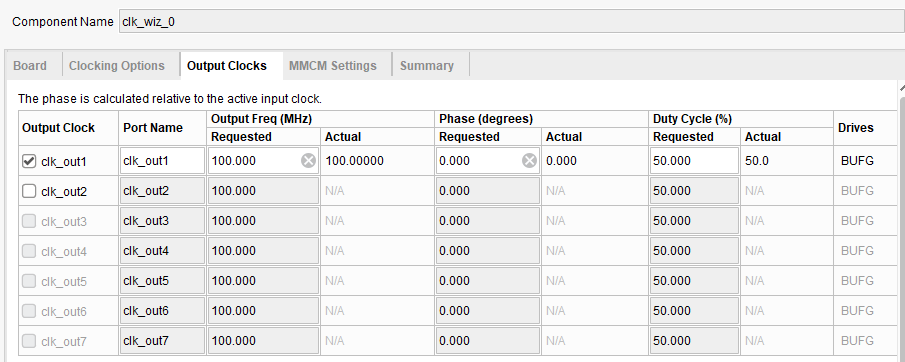

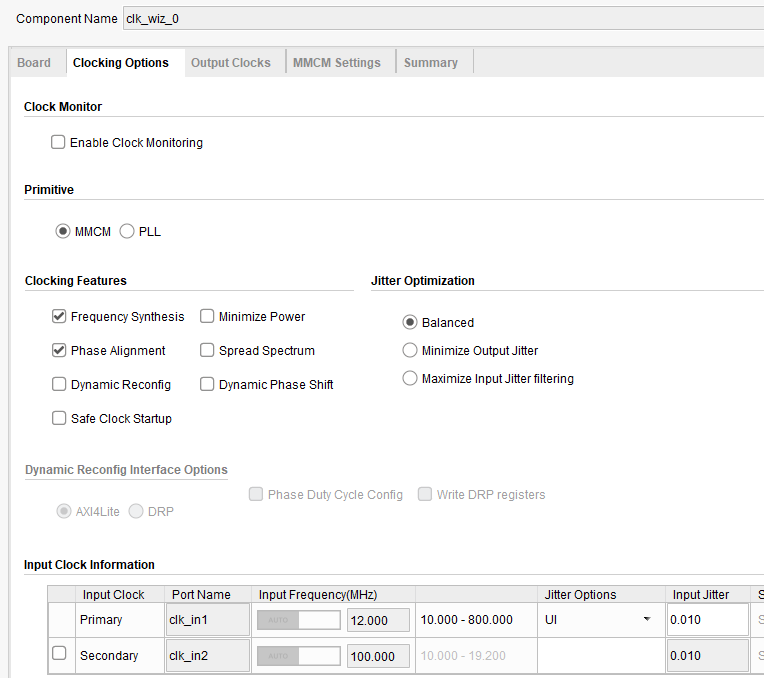

そして肝心のClocking Wizardの設定はデフォルトのまま、まったくいじってません。入力クロック設定は以下に。

100MHzクロックでどうよ。

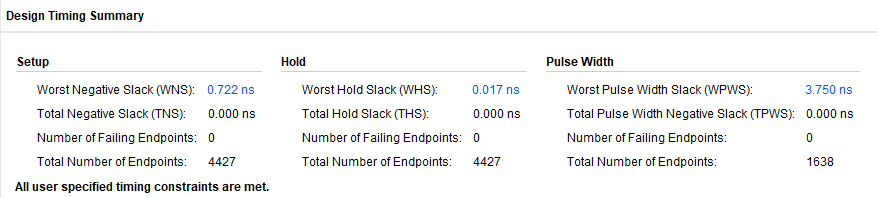

この設定でHDLラッパを生成、シンセシスしてインプリメンテーションしてその結果が以下に。

およよ、ノータイミングエラーじゃん。。。

Clocking Wizardのクロック生成について理解しておらんFPGA素人老人は愕然。でもまよかった。ターゲット・ボードを買い替えなくても演習は続けられそうだ。