前回までに、ラズパイPico2搭載のRP2350とPico搭載のRP2040の電源、クロックなどの比較を行いました。いよいよチップの内部です。最初は「プロセッサ・サブシステム」部分。PicoのRP2040はデュアルArmコア、RP2350ではデュアルArm+デュアルRISC-Vだと。でも実は構造、かなり似てました。

※Pico関係投稿一覧は こちら 『Pico三昧』は一覧の末尾付近にひっそりと。

※Raspberry Pi Pico、Raspberry Pi Pico2のデータシートは、以下からダウンロードできます。

Picoでのデュアルコア

Picoがローエンド風(実際お求めやすい価格だと思います)の味付けの割にちょっと過激なのは、プロセッサ・コアを2個搭載し、並行に動作させることができる点です。組み込みでもハイエンドでは珍しくはないデュアル構成ですが、Picoクラスで猪口才な(個人の感想っす。)

おかげでそのデュアルコアを使うために以下記事書いております。

MicroPython的午睡(12) ラズパイPico、簡単!マルチコアでLチカを

鳥なき里のマイコン屋(133) ラズパイPico、C/C++SDKでマルチコアもお手軽

上の方は、MicroPythonから2コアを使う方法、下の方はC/C++ SDKから2コアを使う方法です。

Picoでは2コアともArm Cortex-M0+でした。ぶっちゃけ、Arm Cortex-Mシリーズ中、一番下の方に位置している普及型のコアです。

Pico2でのデュアルコア

Pico2では、搭載しているArmのコア、かなりグレードアップしてます。Arm Cortex-M33です。浮動小数点処理(FPU)、デジタル信号処理(DSP)にも対応可能な上に、「セキュリティ」にも対応する現代化されたコアです。一方、RISC-Vコアも搭載してます。Hazard3と呼ばれるオープンデザインのコアみたいです。こちらは命令セット的にはRISC-Vの中では一番普及品的な味付け。ちょうどArmにおけるCortex-M0+に似たような立ち位置でないかと思います。

Arm Cortex-M33もデュアル、RISC-V Hazard3もデュアルなのでどうなってんのというと、意外と前世代のPicoを踏襲してました。こんな感じ。

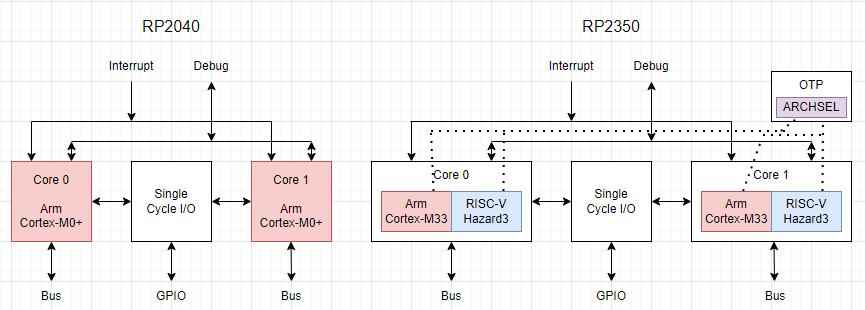

左がPico、右がPico2です。どちらもデュアルコアのCore 0とCore 1があり、それぞれBusファブリック(その先にメモリや周辺回路がある)に接続されています。また割り込みやデバッグI/Fは両方のコアと共通接続されてます。

コアの間にはSingle Cycle I/O(Pico、Pico2の関連文書では略してSIOと書かれてますが誤解されそうな表記です)というブロックがあり、この中にCore間通信の仕組みなどが含まれてます。ここにはコア間通信の仕組み以外にもインタポレーター(補間器)などの計算アクセラレータ的なハードウエアや、タイミング的に正確な直接GPIOアクセス機能などが含まれてます。なお、RP2040でSIOに含まれていた整数除算器はRP2350では取り除かれてます。これはコア側に含まれているためのようです。

なお、RP2350ではSIOブロックは2重化されています。Cortex-M33はモダンでちょっと高級なコアなのでSecure/Non-secureの種別があるからです。Secureで動いているのにNon-secureなコアからちょっかい掛けたりできませぬ。SIOはSecure/Non-secureの区別ありです。これはM33側のみの機能だと思います。細かくみるといろいろありーの。

遠くから眺めると「似たような」構造のRP2040とRP2350が決定的に異なるのは、RP2350がCore 0内にArmとRISC-Vの2コア、Core 1内にもArmとRISC-Vの2コアと合計すれば4コアを搭載していることです。

どちらのコアを使用するのかは、OTPブロック内の制御レジスタARCHSELにセットされている値をハードウエアがRESET時に参照して決定されます。OTPブロックはOne Time Programmingメモリを搭載したブロック(1度しか書きこめない)ですが、ブロック内の制御レジスタには読み書き回数の制限はないと思われるので、何度でも切り替え可能(ただしRESET必要)でしょう。Core 0側、Core 1側それぞれ独立にArmかRISC-Vか選択できるので、Arm+Arm、RISC-V+RISC-V構成以外にArm+RISC-V構成もハード的には可能であるようです。物理的に同時に走れるのは2コアだけのようです。ただしオブジェクトプログラムの生成については「混ぜると」とてもメンドイような気がします。多分、どちらか1種類だけの方がお楽(まだRISC-Vのオブジェクトは作ってないけど。)

先ほども述べたとおりで、Secure-Bootなどとセキュリティ機能を使いたいときはArm Cortex-M33側選択が必須となるようです。

近寄ってみるとRP2350は、プロセッサコア以外にPower-On State Machineなどというものあり、SystemのROSCとは別なring oscillatorをブート用にもっていたりするようです。かなり高級よな。RP2040と似てはいるけどレベチ?