LTspice配下のExampleフォルダ内Educationalフォルダ所蔵の回路図を巡回中。アナログ素人老人が「ノイズ・シミュレーション」に取り組んでます。前回は雑音指数、今回は差動アンプの「スイートスポット」を探ります。元より素人、シミュレーションしても何も分かってないんだが、それでもシミュレーションは動くと。

※「SPICEの小瓶」投稿順インデックスはこちら

※アナログデバイセズ社のLTspiceのガイド、ヒント、便利な情報については以下へ。https://www.analog.com/jp/resources/design-tools-and-calculators/ltspice-simulator/ltspice-recommended-reading-list.html

stepnoise.asc

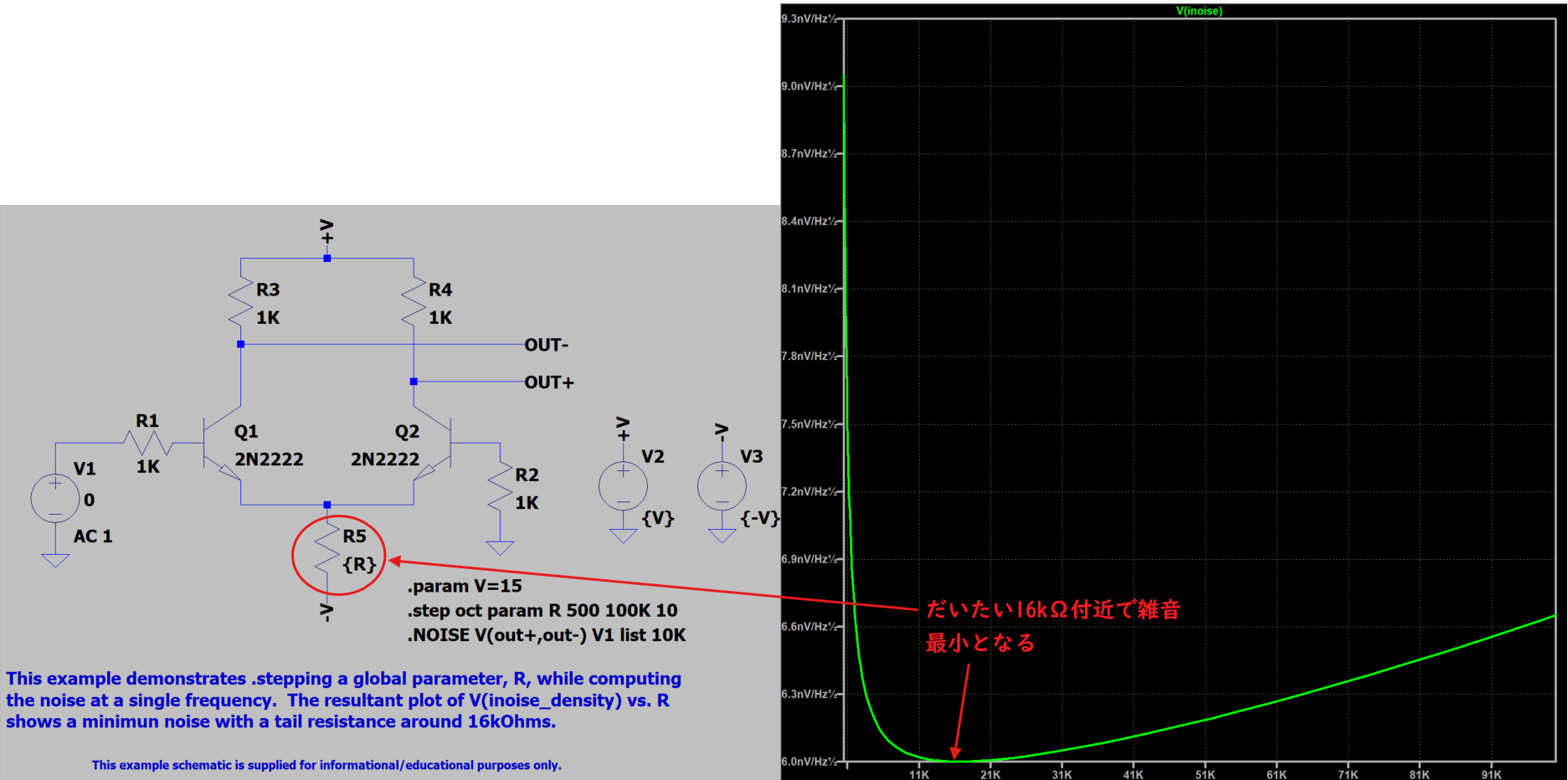

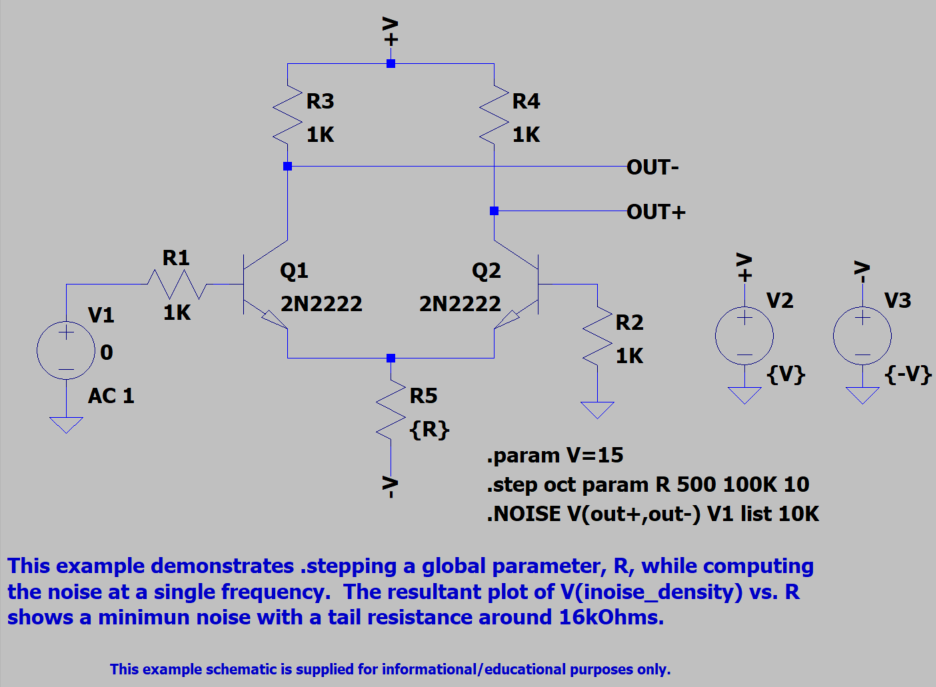

今回のExample回路図のお名前は stepnoise.asc です。回路図が以下に。

定番のバイポーラトランジスタ(Nch)、2N2222を使った差動アンプの回路みたいです。電流源である抵抗R5の値を段階的に変化させたときに、特定周波数(10kHz)における出力ノイズ密度がどのように変化するかどうかを調べるための回路みたいです。

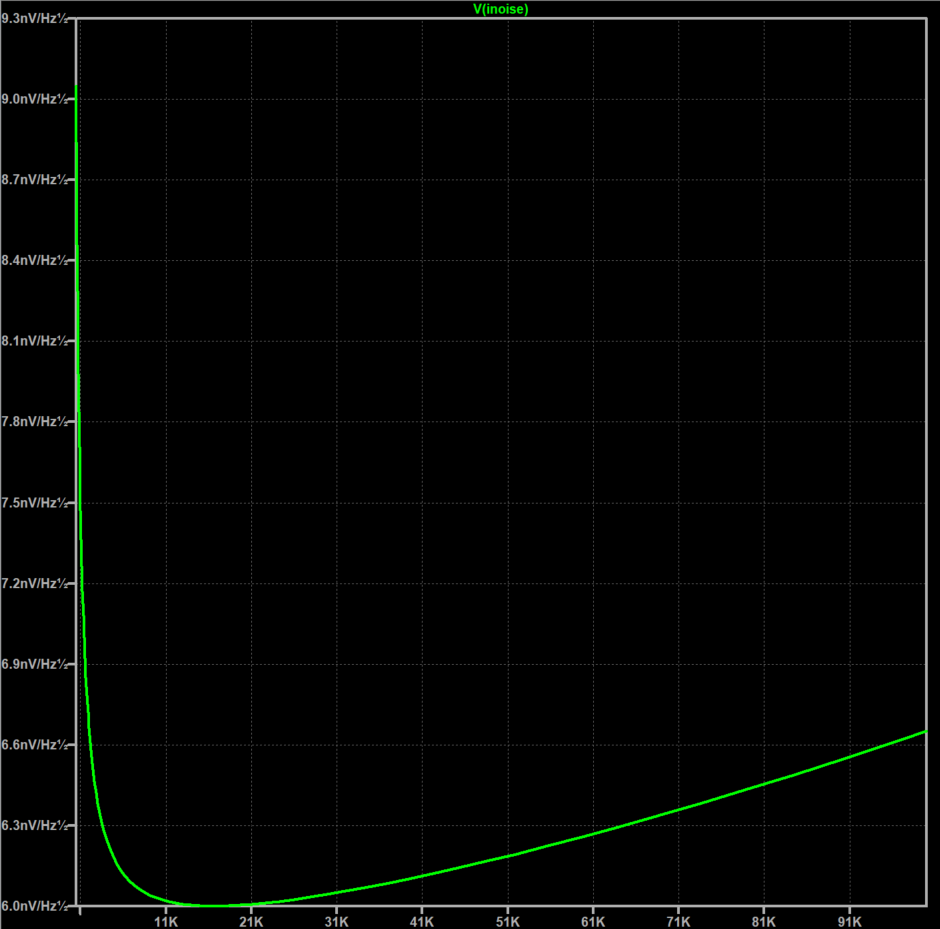

シミュレーション結果のグラフが以下に。縦軸が出力ノイズ密度[nV/Hz]、横軸が抵抗値[Ω]です。

抵抗が低くても、高くてもノイズ密度はデカく、特定の周波数(回路図のコメントに書き込んであるとおり16kΩ付近)でノイズの最小値が観察できます。

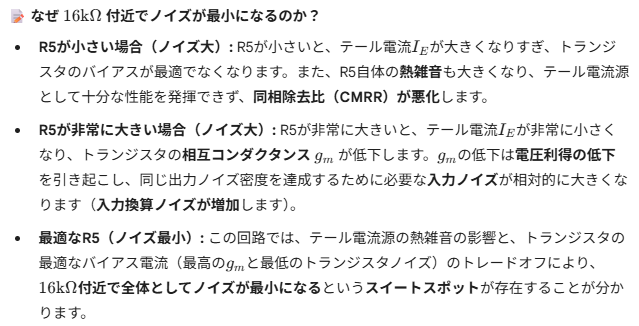

アナログ素人老人が云々言うのも何なので、Googleの生成AI、Gemini様に御伺いを立てたところ、以下のようなご回答を得ました。

ううむ、Gemini様は何でもお見通し、ホントか?