アナログ素人老人がLTspice配下のExample内Educationalフォルダ所蔵の回路図を巡回中。今回は前回のPLL使ったFSK復調回路(PLL.asc)の改良版?(PLL2.asc)デス。さらに「スマート」になってます。でもね、使用しているビヘイビアなコンポーネントのモデル、どこにあるの?

※「SPICEの小瓶」投稿順インデックスはこちら

※アナログデバイセズ社のLTspiceのガイド、ヒント、便利な情報については以下へ。https://www.analog.com/jp/resources/design-tools-and-calculators/ltspice-simulator/ltspice-recommended-reading-list.html

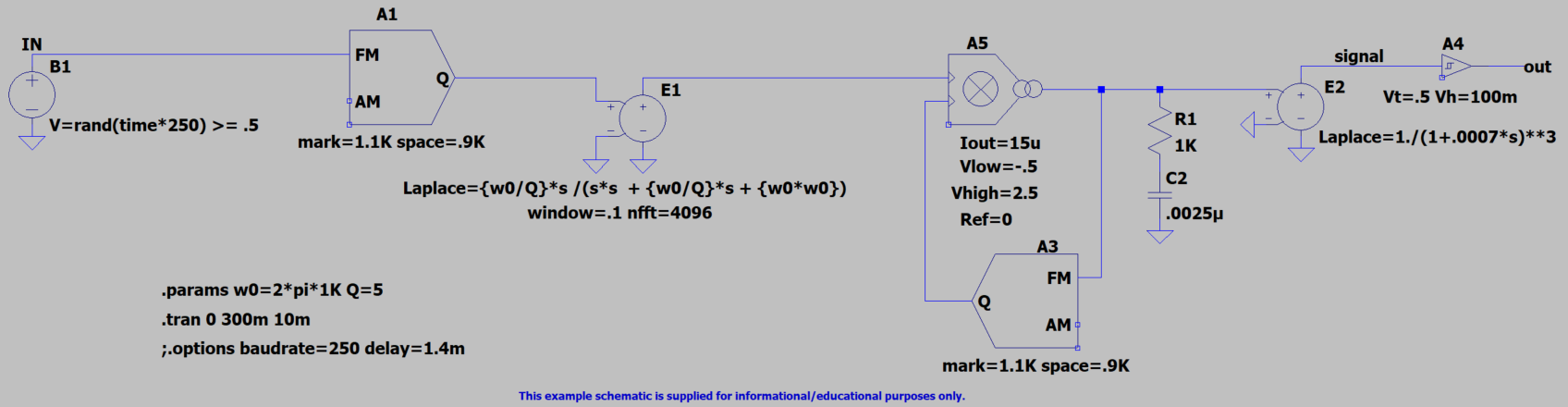

PLL2.asc

今回動かしてみるEducationalフォルダ所蔵の回路は PLL2.asc です。

前回同様、ビヘイビアなPLL回路が中核となっているデモです。回路全体としては、

前回同様のFSK変復調のデモ

です。前回のPLL.ascとの違いはといえば、前回のPLL.asc が位相比較器として単純明快なXOR(排他的論理和)を使っていて、その出力パルスをLPFにかけることでアナログ的な位相のズレ信号を作り出していたのに対して、今回のPLL2ではLTspice が持っている Special Functions というもののひとつ

PHASEDET

XORでは「今ズレとるかズレとらんか」という情報しか出力できませんが、PHASEDETだと、

-

- 進んでる、遅れてる

- どのくらい差がある

といった情報まで出力させることが可能みたいっす。

でも、LTspiceのHELPファイルの Special Functions を見ると恐ろしいことが書いてあります。以下引用です。

Most of these and their behavior are undocumented as they frequently change with each new set of models available for LTspice.

“undocumented” ってどゆこと? それでもごく一部のfunctionの機能のアリガチな説明はあるのですが、肝心のPHASEDETについての記述は見当たりません。

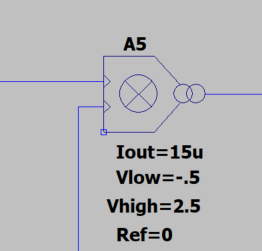

PHASEDETで使われているシンボル

phidet.asy

についてはLTspiceのデータホルダ配下の\lib\sym\Digitalに存在し、以下のような説明が与えられていることは判明してます。以下も引用です。

Behavioral Type 3/4 Phase Detector (phase/frequency detector). NOTE: Limit input rise times

Type 3/4って何よ? 3/4てことは、Type 1とかType 2とかあるんだよな。そう思って調べました。多分ありました。前回何度となく練習したよな、と過去回へリンク張った「定番のPLL IC」の位相比較器部分、1と2とお名前がつけられているではないですか。これがType 1、Type 2の実体みたい。でもま、アナログ素人老人にはType 3/4に心当たりはありませぬ。lib配下のlibとかsubとか検索しても該当しそうなモデルはなく、

現物に聞く

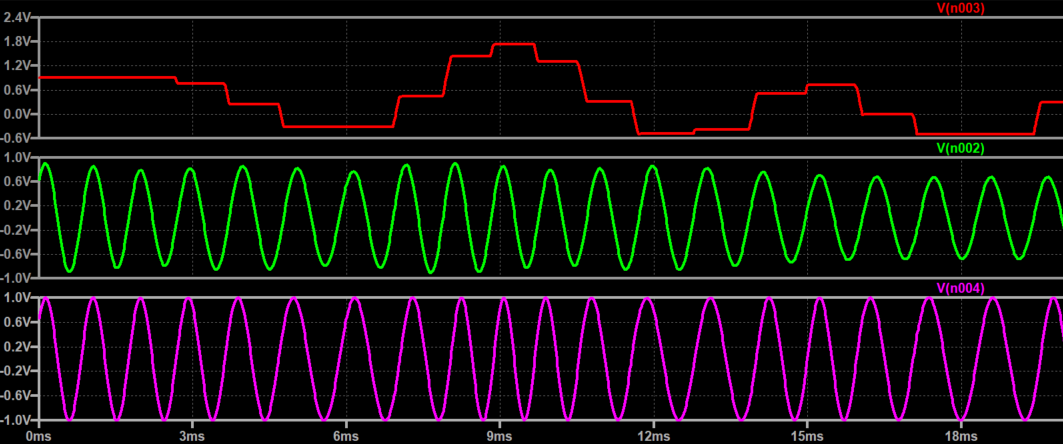

緑が入力側、ピンクがフィードバック側、赤が出力です。上をみると位相がピッタンコのときは中心にある電圧が、出力の位相が早くなるとマイナス側に、遅くなるとプラス側に振れることがみてとれます。まあ、こういうもんだ、と飲み込むしかない?いい加減だな。

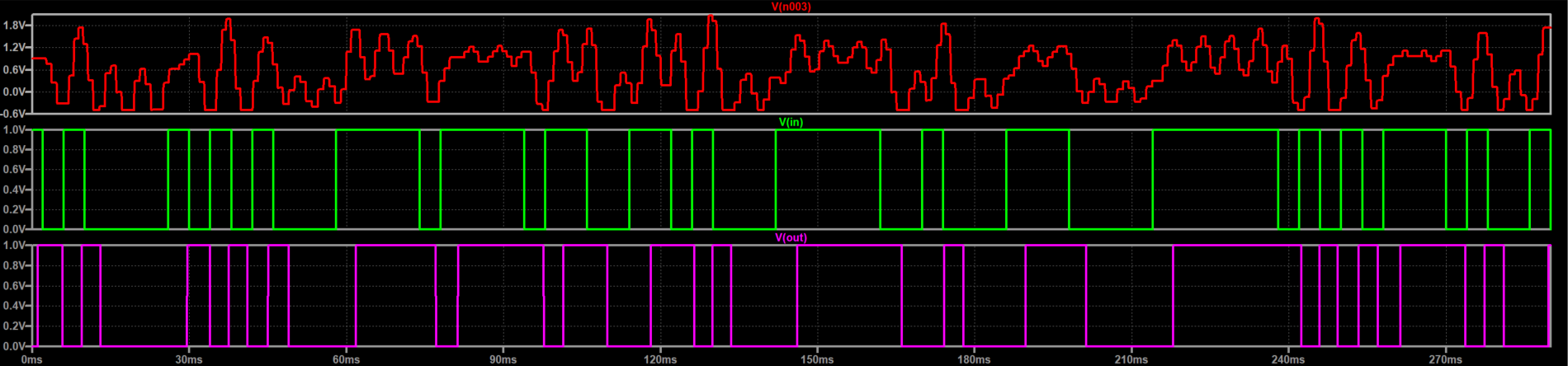

シミュレーション結果

素のPLL2.ascのままだと、下2つのペインしか現れませぬ。前回同様、入力のランダム乱数列が「復調」されていることのみの出力です。それだけでは味わい難いので、一番上のペインにPHASEDETの出力波形を加えてみました。復調途中の雰囲気は出ていると。ホントか?