前回、SAR ADCの実例に後戻りしてしまったですが、今回は、前々回の続きのデュアルスロープADCです。前々回にLTspiceシミュレーションで、動作の雰囲気は分かった(ホントか?)ので今回は実機でGoと思ったらどうもシミュレーション用の回路図と、実体回路図の間に違いがある感じです。まずは差異を調べるところから。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

アナデバ社(ADI社)のWeb記事『StudentZone』の2022年2月号もようやく大詰め、記事の末尾『追加の実習-デュアルスロープADC』です。前々回、LTspiceでデュアルスロープADCの動作を眺めたので、ブレッドボード上に回路を組み立てようとして手が止まりました。

シミュレーション用の回路図とボレッドボードの実体回路図に差異

ありです。まずはどうしたもんだか検討せにゃならんです。

※2022年9月24日追記:以下記事、節穴です。コマケー違いしかないなどと認識してますが、次回記事で実体回路図にフェイタルな「動くわけない」問題複数発見。ダメダメです。

LTC1043

今回の主役は「LTC1043 デュアル精密インストルメンテーション用スイッチト・キャパシタ・ビルディング・ブロック」というデバイスです。スイッチト・キャパシタ回路で使うICみたいです。アナログ素人には恐れ多いデバイスであります。製品ページが以下に。

上記のページからデータシートなどダウンロードできます。

差異の確認

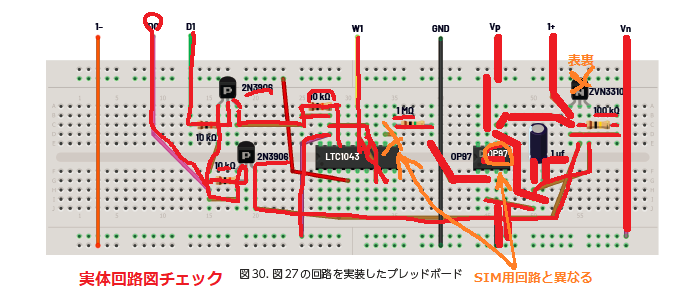

差異の確認は、人手というか、目ん玉です。アナデバ様の記事の中の該当の実体回路図を引用させていただき、そこに汚らしく線を引いてチェックしたものを冒頭のアイキャッチ画像に掲げました。

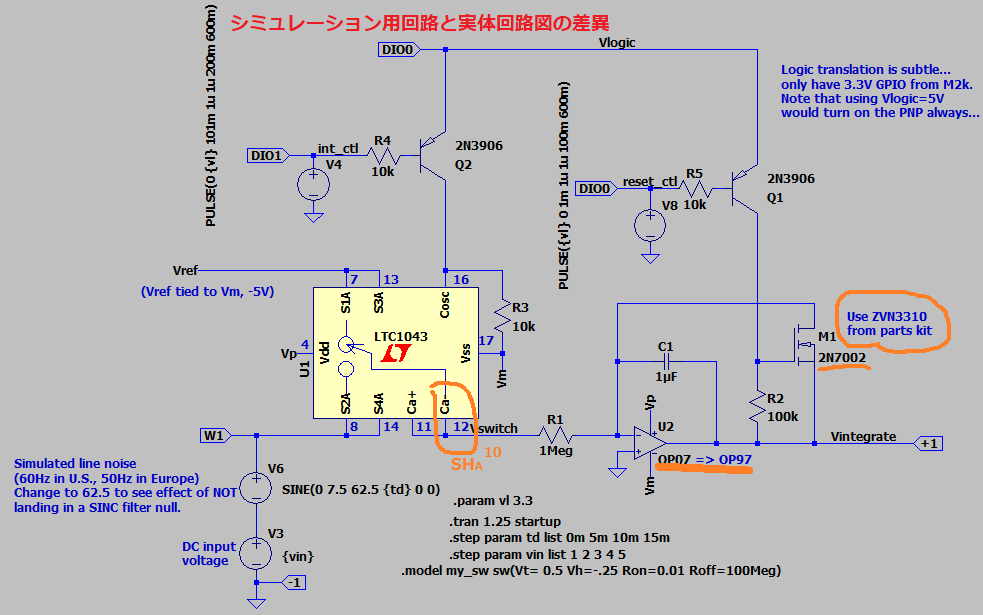

アナデバ様サイトからダウンロードしたLTspiceの回路図に差異の点を書き込んだものを下に掲げました。

列挙すれば以下のとおり、

-

- オペアンプ(積分回路に使用)が、シミュレーションではOP07から実体回路図ではOP97に変更になっている。察するにOP07はADALP2000部品キットには含まれていない(けれどLTspiceにはモデルが含まれる)けれど、OP97はADALP2000部品キットに含まれており(けれどLTspiceにはモデルが無い)というねじれのためかと。知らんけど。

- シミュレーションのMOSFET 2N7002が、実体回路図ではZVN3310に変更になっている。これも上記同様のLTspiceとADALP2000部品キットのねじれの関係の回避策かと。こちらについてはLTspiceの回路図上にコメントあり、ZVN3310使えとあり。

- なお、実体回路図ではZVN3310は、カマボコ型の丸い方を背中にして平らな面を手前において結線しているがそうすると、ソース、ドレインの結線がひっくり返る。ZVN3310は、丸みを帯びた側(丸いけれど扁平なのでこちらにマーキングあり)を手前にすると回路図通りとなる。多分、実体回路図ではBJTの絵を流用しているために実際と差が出ている?知らんけど。

- 主役、LTC1043、SPICE回路図では CA+(11番ピン) CA-(12番ピン)に接続されている出力が1MΩを介して積分器に入力されている。しかし、実体回路図では、11番のCA+と10番のSHAに接続されていて、CA-には接続が無い。アナログ素人は「スイッチト・キャパシタ回路用」に恐れおののくばかりだが、多分、きっと、ここの場合はCA-だろうと、SHAだろうと問題ない?知らんけど。

どれもコマケー話。分かっている人は歯牙にもかけないのでありましょう。差異は分かったんだから、次回こそちゃんと実機で動かせよ、自分。