Vivado 2024.1より、RISC-V(MicroBlaze V)の公式サポート開始。年甲斐もなく熱狂。前々回はRISC-Vコアの簡単なハードでbitファイル作成。前回はその上で走るHello Worldコードをビルド。ELFファイルまで出来。しかしダメ。ターゲットボードが認識されてない。RISC-V以前の問題。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

お間抜けな顛末

熱狂してRISC-Vコア応用の「マイクロ・コントローラ・デザイン」に取り組んだものの、開発ツールVitisがターゲットボード、Cmod S7を認識せずまさかの失敗であります。よく考えてみれば、Vivado 2024.1を新にインストール直後、ターゲットボードを接続して書き込みができるとか一切確認せぬままに、RISC-Vに突っ込んでました。先を急ぎ過ぎだな、自分。

まずはVivado 2024.1環境で、ちゃんとCmod S7を接続してビットストリームを書き込むことができて、実行できる確認からやり直すことにいたしました。具体的には、以下の過去回で Vivado 2023環境でやったことを再度実施。

帰らざるMOS回路(43) Digilent CMOD S7導入。AMD(Xilinx)だ。

ただ上記を振り返ってみると、以下のDigilent社のチュートリアル通りに実施しているので、具体的なことを書いてないデス。忘却力の老人は思い出すのに難渋。このさい、ステップ・バイ・ステップで経路を記しておこうと。実施するのはVerilog記述のハードウエアLチカです。

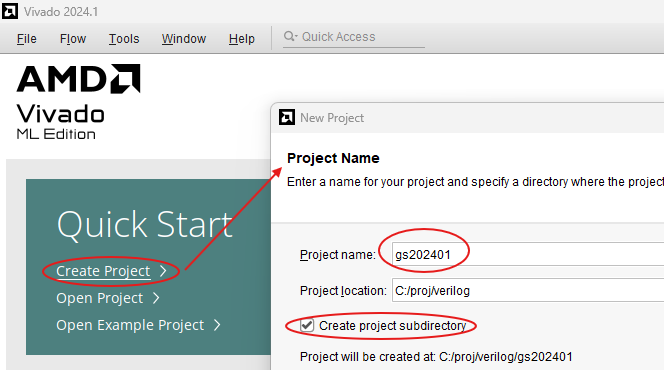

まずはプロジェクトの作成から

プロジェクトの作成はCreate Projectからっす。ここはいつもの通りね。

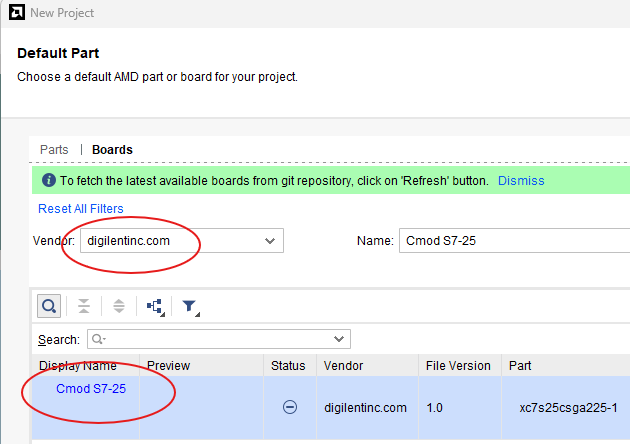

そして、ターゲットFPGAまたはターゲットボードの選択。すでにDigilent社のサイトからDigilent社のボード情報をダウンロード済なので、ターゲットのCmod S7ボードを選択するだけです。

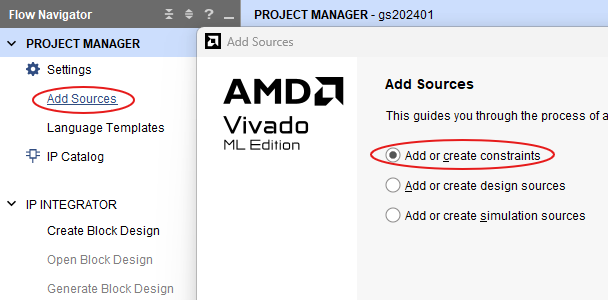

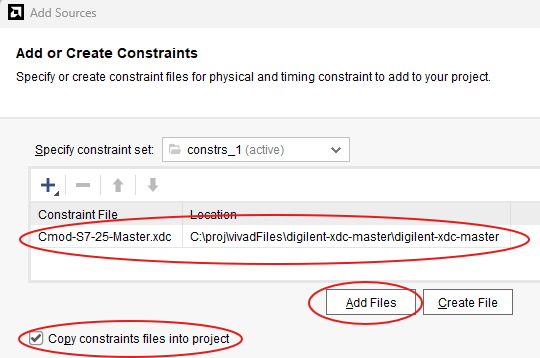

つづいて「制約ファイル」constraintsをプロジェクトに加えます。

これまた、Digilent社のサイトからダウンロード済なので、Add Constraintsで場所を指定するだけ。なお忘れずにCopy constraints files inot projectにチェック(コピーすれば書き変えてもオリジナルはそのままなので。)

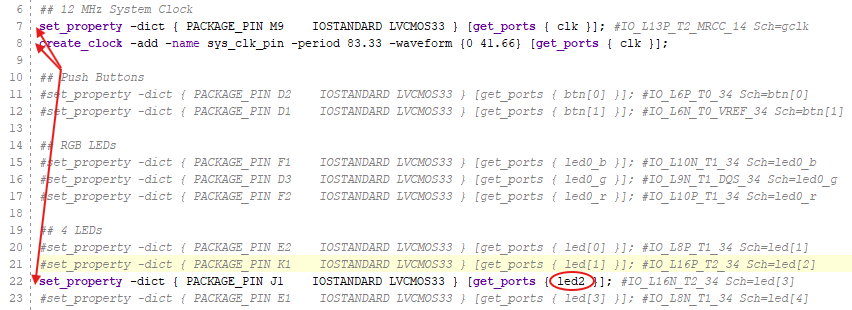

そして制約ファイルを開き、12MHz System Clock以下の2行と 4LEDの下の1行のコメントを外します。矢印のところね。これで オンボードのCLK源とオンボードのLEDのうち1個が使えるようになりました。なお、過去回と変えて点滅させるLEDは左から3番目のLEDとしてあります。お名前は led2 ね(自分で名前を変えておいて後で痛い目にあうのでした。)

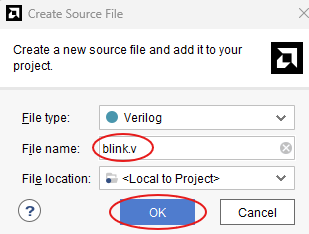

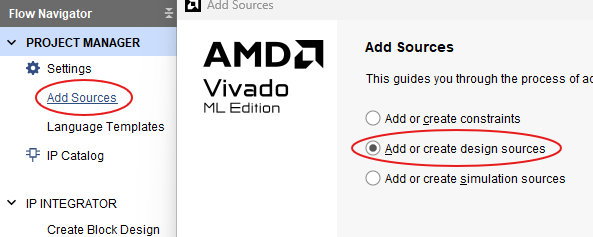

つづいて、ハードウエアLチカのための Verilog コードを追加します。

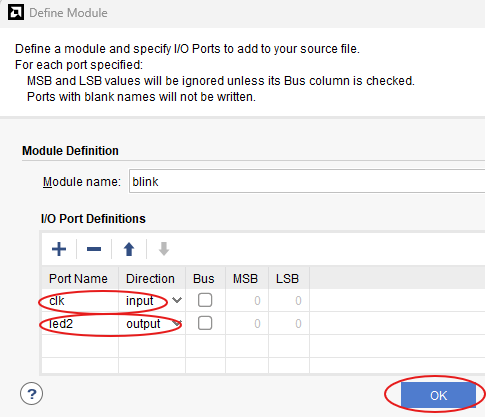

モジュールの入出力端子を聞かれるので、今回は clk と led2 と答えておきます。(ここまでは覚えていたのね。)

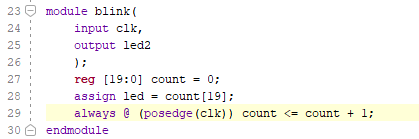

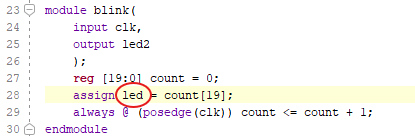

そしてLチカのソースを書き込みます。モジュールの引数どもは、上のウインドウの定義から自動入力されてます。下の3行は手入力です。ここでは気づいてないですが、led2とすべき信号名を ledなどとしてます。ヤバイよ。

なお、クロック源が12MHzなので、20ビットのカウンタ(1Mカウント)通せばすごく早い速さでLEDが点滅するけど肉眼確認できる筈。

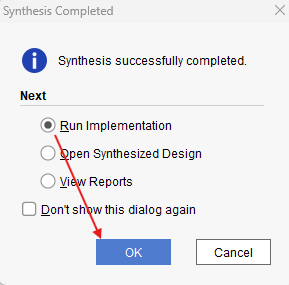

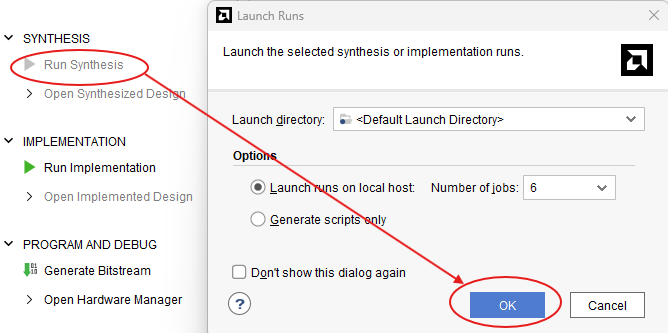

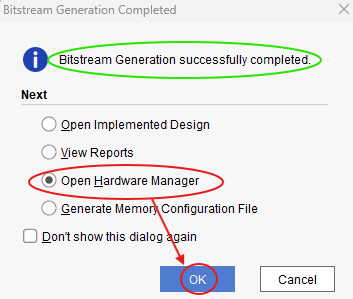

ソースができた(バグがあるけど)ので、シンセシスから。シミュレーションやっておけばバグに気づくのだけれども「ハードの設定だけ」のつもりなのでやらない。急がば回れっていうだろ~。

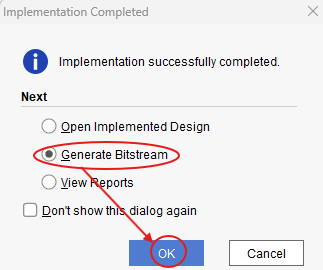

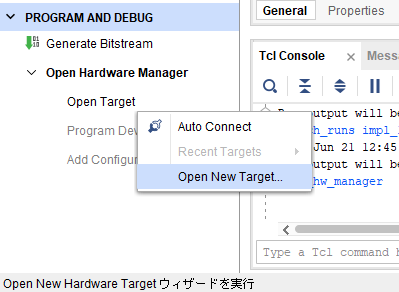

ああ、ビットストリームの生成できました。ここからが問題ね。ターゲットボードを開発機に接続し、ハードウエア・マネージャを起動。えい。

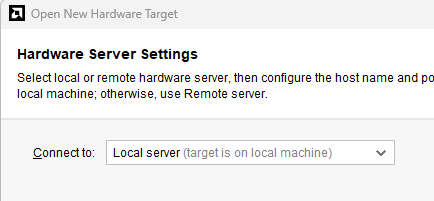

開発機にボードは接続してあるので、Local server指定。

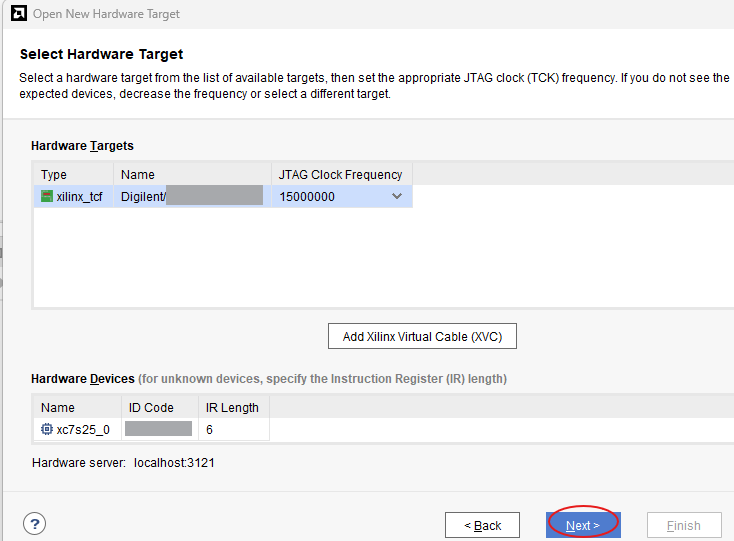

問題なく、検出されているみたい。前回とかはこの辺のステップを吹っ飛ばしてたものな。。。

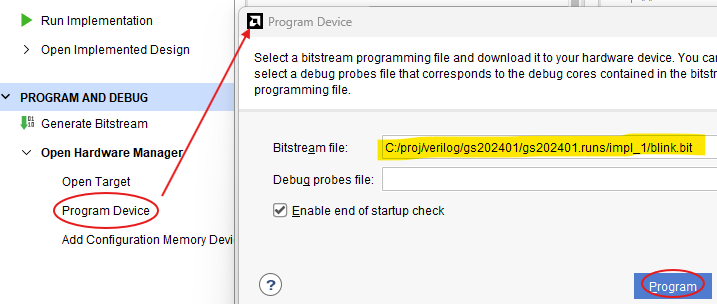

さてボードが認識されたので、Program Deviceへ。生成したビットファイルを指定。

書き込みました。

しかしLチカしませぬ。

ここでVerilogソースのバグに気づきました。

大間抜けをFIXしたらLチカOK

以下のled と書いてあるところ、led2 に修正いたしました。

その後、当然ながらシンセシス以下の工程を再度繰り返しました。トホホ。

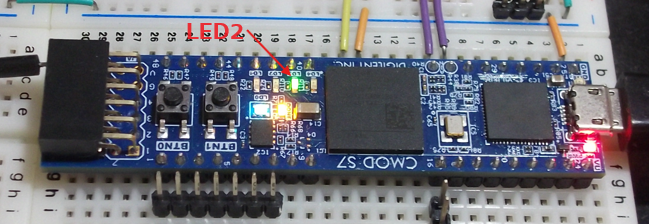

結果が以下に。LED2(4個ならんでいるうちの左から3個め、高速に点滅しておりますぞ。)

やっと、接続確認ができたな。