別シリーズにてx86のアセンブラを古き16ビットから順に練習中です。段々煮詰まり、バス波形を参照しないと動作が説明できん命令に近付いております。しかし今時8086のバス波形など説明するための土台がありませぬ。そこで今回は何を今更8086/8088のバス波形(Read)をWaveDrom使用で描いてみました。

8086、8088のモードとバス

半世紀ほど前の8086/8088の端子やバスなどを覚えている人も今や珍しい、というか若者どころか中年の方々も御存じないと思います。お惚け老人はそういう世代とは言え、忘れてます、忘却力。

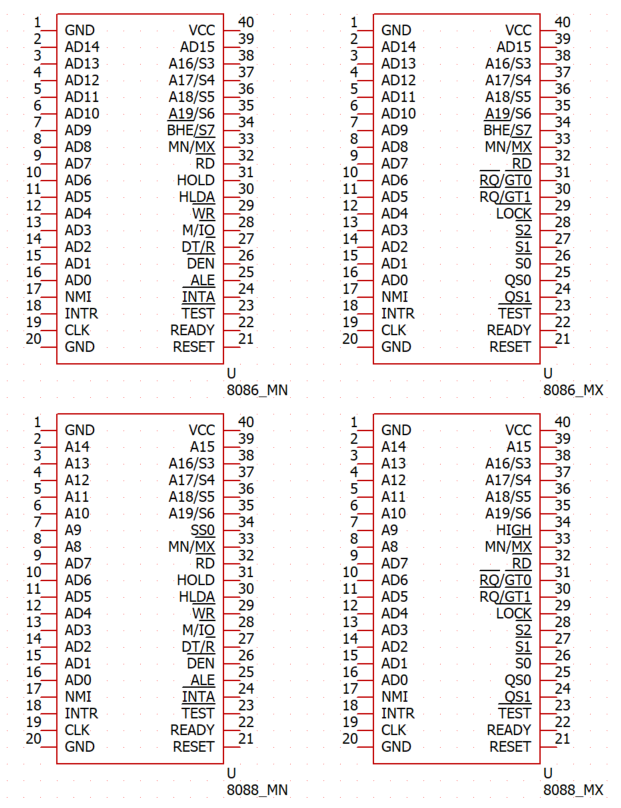

まず思い出さねばならないのは、「兄弟チップ」であり、最初のx86である8086、8088の端子について、おおきく以下の2つについてそれぞれ2つ、合計4ケースに分けられるということです。

-

- 8086は16ビット幅のデータバス、8088は8ビット幅のデータバス

- 8086も8088もバスモードにはミニマム・モードとマクシマム・モードがある

データバスの幅は見れば分かる話なので置いときます。ミニマム・モードとマクシマム・モードというのは8086でも8088でも同じように装備されている機能です。

-

- ミニマム・モードとマクシマム・モードはCPUのMN/MX#(#はロウアクティブと思ってくさされ)端子に印加する電圧で決まる。

- ミニマム・モードは8086または8088が唯一のCPUとして動作する「最小構成の」システム(DMAくらいは使えるが)を想定したモードで、バスの制御信号などは8086または8088から直接制御される。

- マクシマム・モードは、複数のCPUが混在するような大規模なシステム(有名なところではインテル・マルチバス)で使う想定のモードで、8086や8088はステータス信号を出力するが、実際のバス制御信号は外部のバスアービターによって制御される。バスアービターが複数のCPU間の調整をよろしくやってくれる(筈。)

実際に8086と8088で、ミニマム(MN)とマクシマム(MX)で端子機能がどう変わるかを比較したものが以下に。全て40ピンDIPのイメージっす。

いろいろあってメンドクセー。

8086、ミニマムモード、リードサイクルのバス波形

さて表題のときの波形を WaveDromを使って描いてみました。タイミングチャートの作成ツール、WaveDromについては以下の別シリーズ過去回にてやってます。

帰らざるMOS回路(36) タイミングチャートを描きて~ ツールは何?

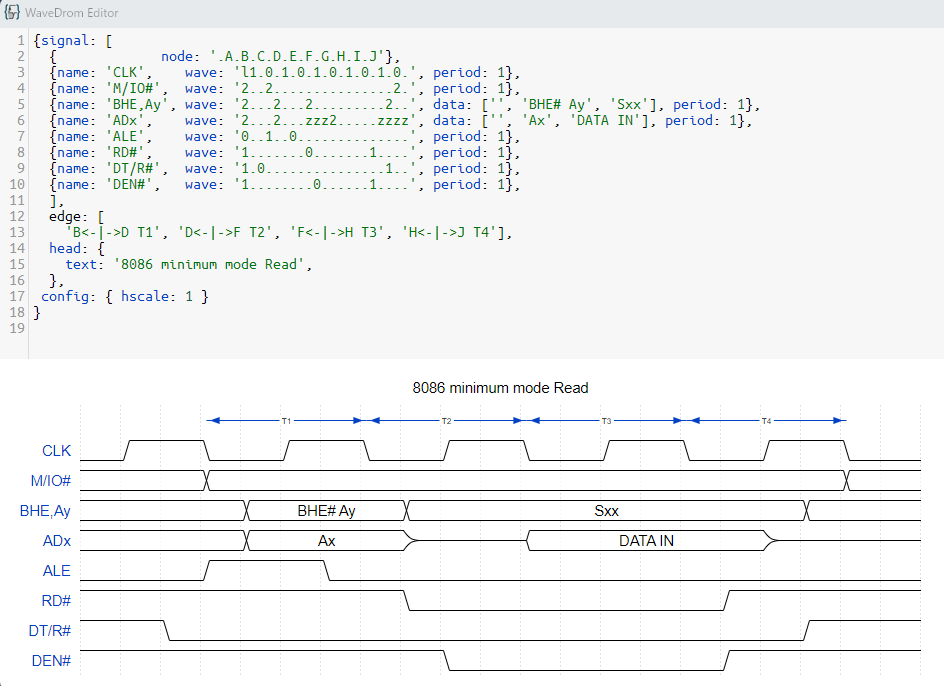

波形定義が以下に。

{signal: [

{ node: '.A.B.C.D.E.F.G.H.I.J'},

{name: 'CLK', wave: 'l1.0.1.0.1.0.1.0.1.0.', period: 1},

{name: 'M/IO#', wave: '2..2...............2.', period: 1},

{name: 'BHE,Ay', wave: '2...2...2.........2..', data: ['', 'BHE# Ay', 'Sxx'], period: 1},

{name: 'ADx', wave: '2...2...zzz2.....zzzz', data: ['', 'Ax', 'DATA IN'], period: 1},

{name: 'ALE', wave: '0..1..0..............', period: 1},

{name: 'RD#', wave: '1.......0.......1....', period: 1},

{name: 'DT/R#', wave: '1.0...............1..', period: 1},

{name: 'DEN#', wave: '1........0......1....', period: 1},

],

edge: [

'B<-|->D T1', 'D<-|->F T2', 'F<-|->H T3', 'H<-|->J T4'],

head: {

text: '8086 minimum mode Read',

},

config: { hscale: 1 }

}

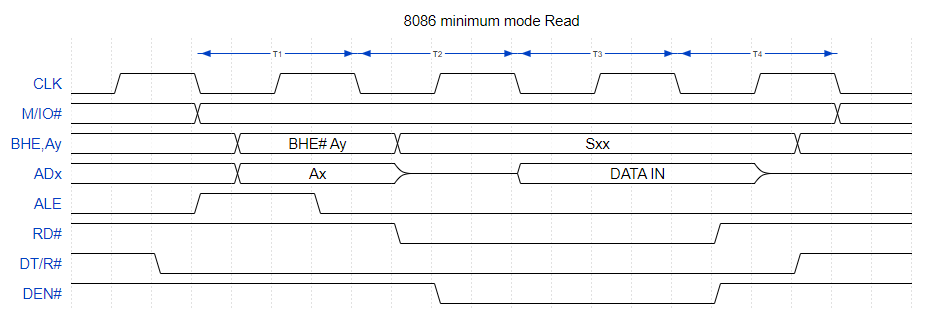

古き時代の8086/8088は4CLKで1バスサイクルです。x86にはメモリ空間とIO空間の種別があるのでM/IO#信号でこれを区別してます。アドレスバスとデータバスはマルチプレクス(時分割でアドレスになったりデータになったりする)なので、先ずアドレスを出力しておいてALE(アドレス・ラッチ・イネーブル)信号の立下りでアドレスを外部で保持する必要があります。また、8086の場合、16ビットデータバスとはいえ、8ビット縛りの動作をすることもあるので、BHE(バス・ハイ・イネーブル)信号で、上位8ビットのデータバスの有効、無効を示します。

リードサイクルにおいては、アドレスの出力後、アドレス・データバスは引き続くデータリードのために、CPU側はハイインピーダンスとなります。データバスのイネーブルを制御するためにDEN#信号、方向を制御するためにDT/R#信号、読み出しを制御するためにRD#信号があります。上記であるとRD#の立ち上がりのところでデータバスのDATA INがCPUに取り込まれてリードサイクルが完了します。

いい加減だけれども、こんな感じでよいかしら?