アナデバ様のWeb記事『StudentZone』の2025年9月号(日本語版)の実習初回。今回は歯ごたえありそうなテーマっす。アクティブ・ミキサね。周波数を掛け算すると和と差が出てくるアレっす。一方アナログ素人老人はしばらく実習休業、身体がついていきませぬ。初回はリハビリ、シンプルなシングル・バランスド・ミキサです。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

※今回のシミュレーションについては次回にて問題点発覚、その件についてはこちら

シングル・バランスド・ミキサ

単にバランスド・ミキサとだけ言われることもあるみたいです。シンプルな回路は良いけれど、いろいろ欠点もアリーので、実際には余り使われない回路みたい。でもま、万里の道も一歩からということでリハビリ。実際に回路を組み立てるのは、また次回に先延ばしして、今回はシミュレーションでお茶を濁します。

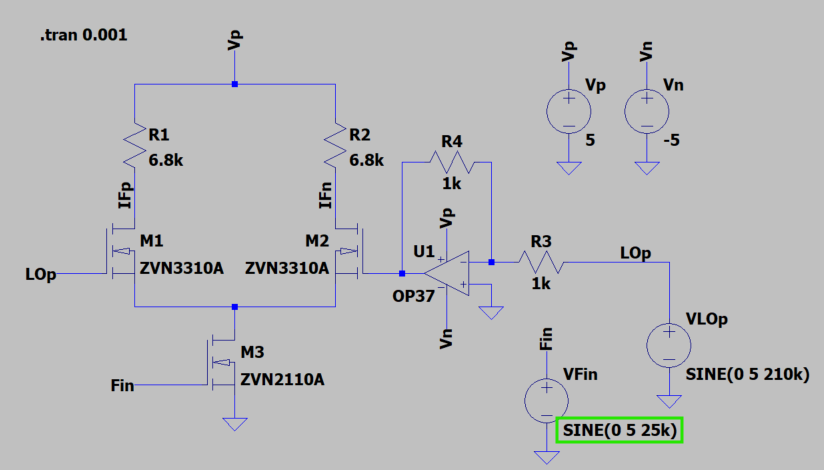

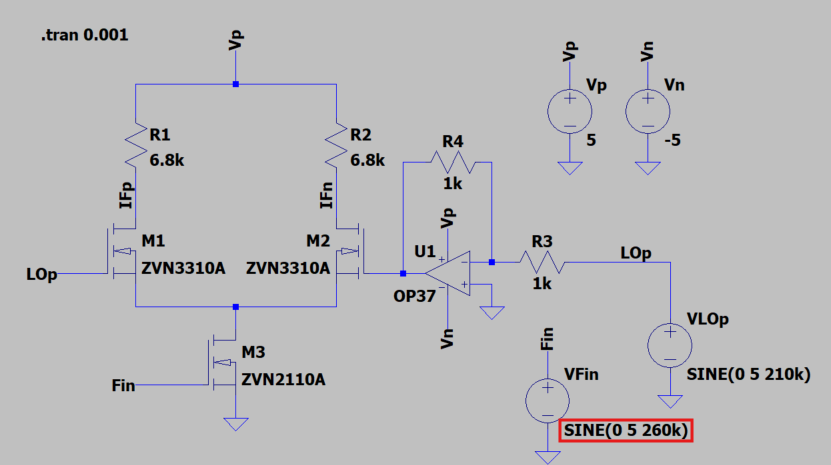

まずは最初のシミュレーション回路(アップコンバージョン用設定)が以下に。

使用しているNch MOSFET、ZVN3310AとZVN2110Aはアナデバ製学習用部品キットADALP2000に含まれてますが、残念なことにSPICEモデルはLTspiceの標準ライブラリには含まれておりません。以下のかなり前の過去回にてDiodes Incorporated社のモデルをダウンロードさせていただいております。それを使用。

SPICEの小瓶(1) MOSFET、MOSMODELパラメータとSUBCKTの切り替え

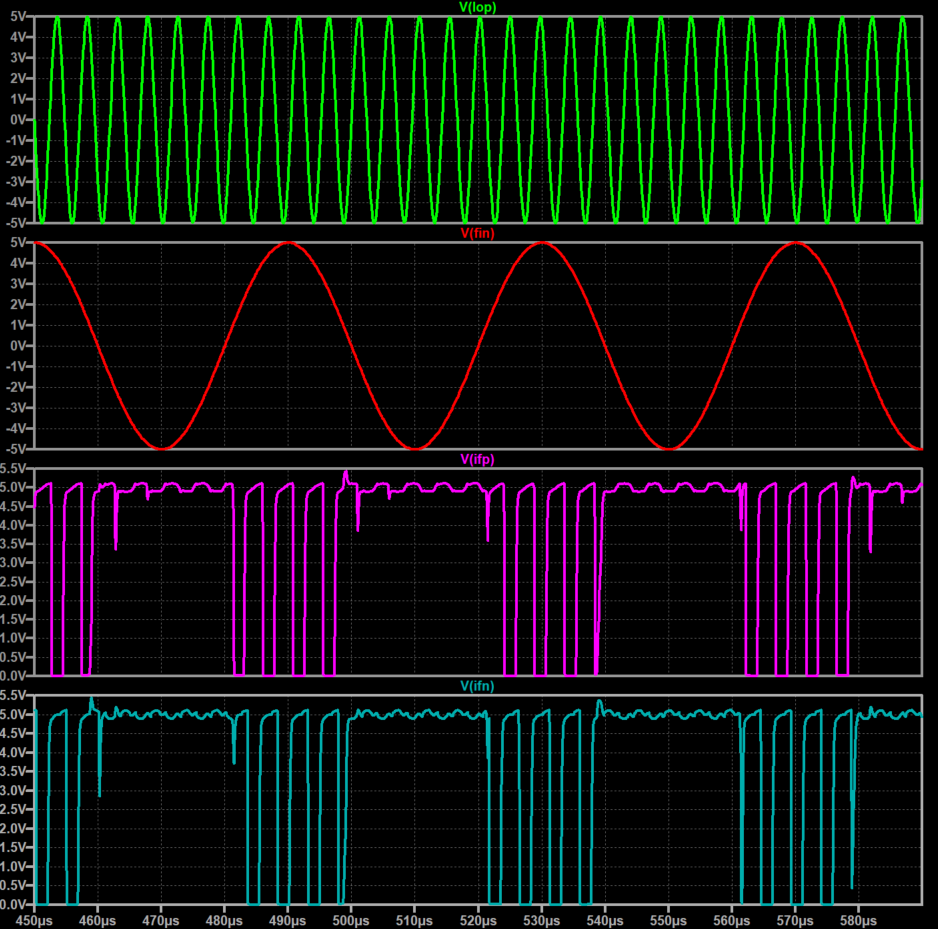

さて、上記のシミュレーション回路を走らせてみると、時間波形(拡大)はこんな感じ。

一番上の緑の波形が、LO、局発ってやつ、210kHz。次の赤の波形が変調波、Finってやつ、25kHz。そして下の2つが、LOの周波数-Finの周波数の出力波形と、LOの周波数+Finの周波数の出力波形っす。しかし時間波形みていてもサッパリです。

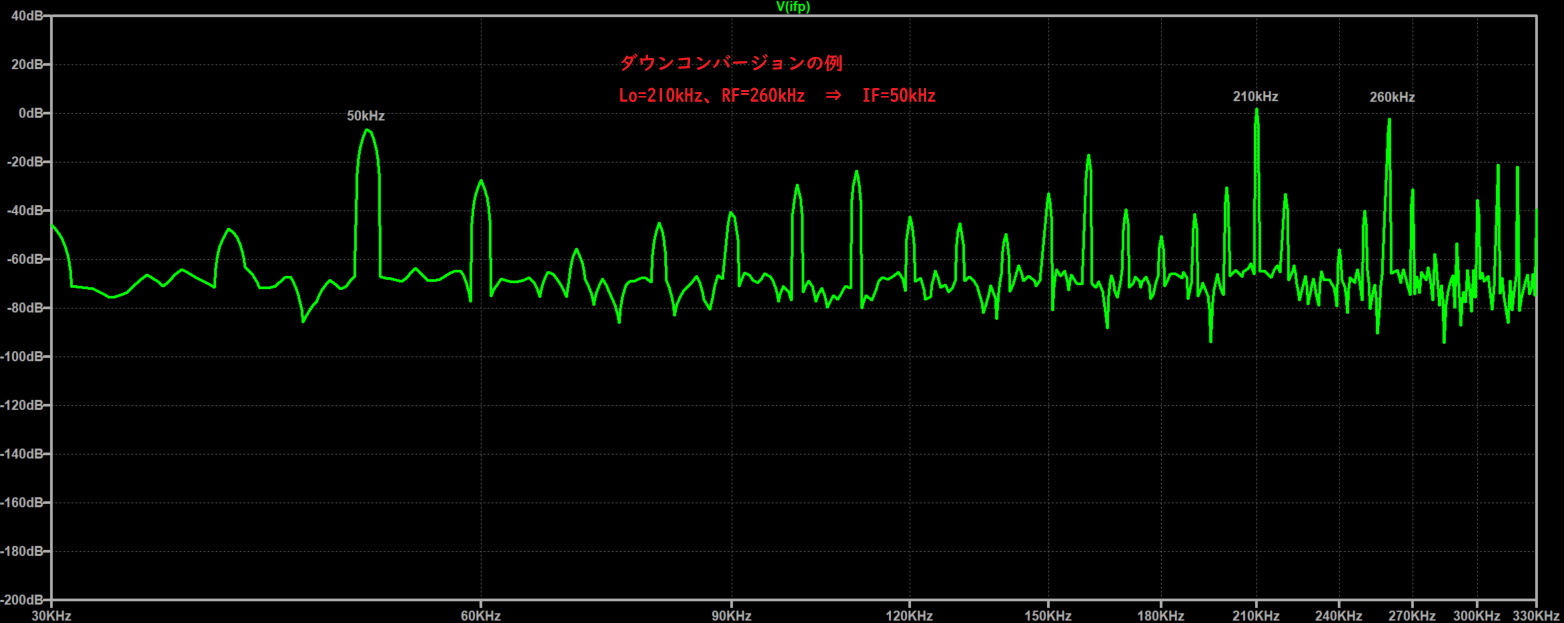

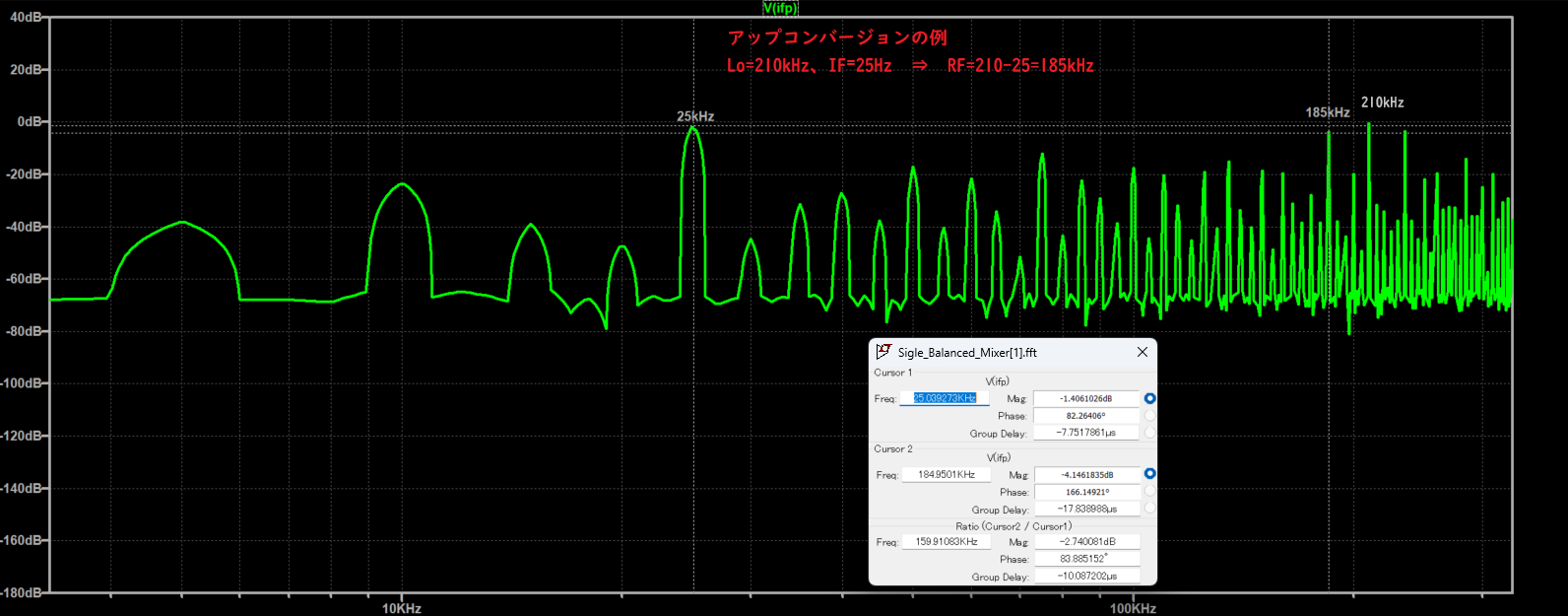

アップコンバージョンの結果をFFTにかけてみたものが以下に。

左手の方に、25kHzの山(Fin)が見え、右手に210kHz(Lo)と185kHz、235kHzも見えているみたい。両方見えてるじゃん。いいのかこれで。

一方、ダウンコンバージョン(高いFinの周波数から低いIF周波数を得る)用のシミュレーション回路の設定がこちら。

210kHzのLoに、260kHzのFinを掛け合わせると、260-210kHz=50kHzが出てくると。三角関数の公式からは「当然」なんだけれども、リハビリ途上のお惚け老人には何が何やら、落ち着かないよ。