前々回に開発ツールのインストールを済ませたAn Logic社のFPGA、EG4S20BG256を搭載したSiPEED社TANG PRiMERボードなのであります。開発ツールにはユーザーズマニュアルが付属しておるのでありますが、中国語(簡体字)でした。どうもこれを読み込まさないことには先に進めそうにないので、「読んで」みることにいたしました。Goolge翻訳のお助けで。

※「部品屋根性」投稿順Indexはこちら

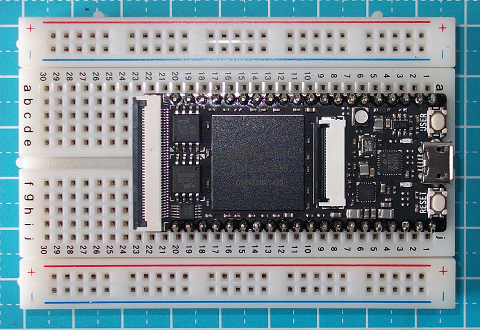

前々回からハード的に「一歩前進」したのは、アイキャッチ画像に掲げましたとおり、ボードにピンヘッダを半田付けしたことであります。これでブレッドボードに刺せるようになりました。ただし、ピンヘッダに取り出せている信号はチップ全体からするとわずかにすぎません。

- ピンヘッダ左右合計40ピン、そのうち電源等に割り当てられているものあり

- デバイスはBGA256、ユーザI/O端子は最大193端子

なお、ピンヘッダに出ている端子は、RISC-VコアをこのFPGAに書き込んだときにちょうど使えるような塩梅になっておるようです。

蛇足ですが、USB経由でFPGAを制御しているのはGigaDevice社のGD32シリーズのマイコンですが、調べてみるとArm Cortex-M3コアのGD32F150という系列のものでした。RISC-Vマイコンではありませぬ。

さてこのFPGAの開発ツール(IDE)は、Tang Dynastyというお名前であります。「唐王朝」でありますな。日本も遣唐使を送っていたくらいで「盛唐」が未だに皆さんの心に響くので在りましょう。当時、日本が輸入した漢字文化の末流のお陰で、日本式に書けば「軟件手冊」、ソフトウエアマニュアルもある程度は意味が取れるのであります。しかし、もっと良いものがありました。

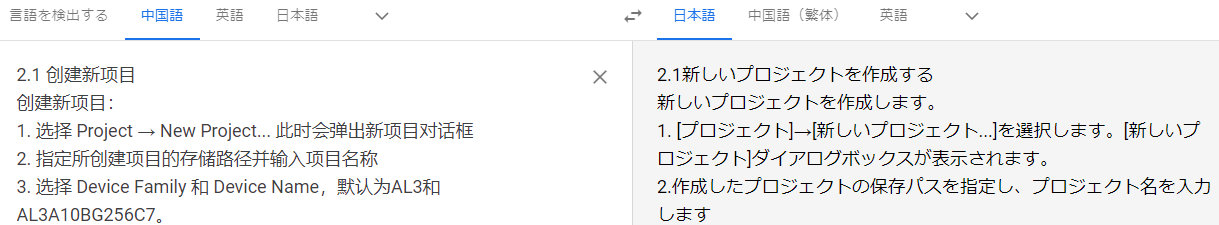

Goolge様の翻訳に頼れば、これこのように、簡体字中国語も一撃で日本語になりまする。そのうえ、マニュアルのような構文と用語に制限の多いものでは、かなりな精度。まったくもって問題ない。

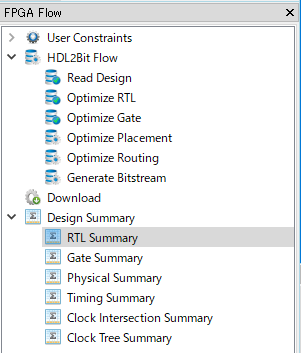

さて、FPGAを設計するにあたって、このTang Dynastyソフトウエアが主として遂行してくれるのは、

- 使用するIP(回路ブロック)を準備する

- 論理合成

- その結果をビットストリームにしてFPGAへ書き込む

という、必須の部分であります。

起動するとあらわれる画面の通常左したにあるであろう、FPGA Flowというところに、その工程がサマライズされています(どこかの会社のツールにもこういう画面があったな~)

起動するとあらわれる画面の通常左したにあるであろう、FPGA Flowというところに、その工程がサマライズされています(どこかの会社のツールにもこういう画面があったな~)

まあ、この画面にそって作業をするまえに、

新たなプロジェクトを始める。その際には、ターゲットのFPGAデバイスを選ぶ

というProjectの作成あり。そのプロジェクトへソースコード(VerilogでもVHDLでもよいみたい)を追加し、といった必須の準備があります。また、自力で一からプロジェクトを起こすだけでなく、ISE、Quartus IIといった某大手FPGAメーカのツールのプロジェクトから変換することも可能なようです。

ようやく、今回の本題ですが、このフローの中で表向き欠落しているのが、

論理シミュレーション

です。Tang Dynastyは、シミュレーターとのインタフェース(必要なソースをそろえる)機能は持っているのですが、シミュレータそのものは含んでいません。定番の商用のツールである、ModelsimとかVCSとかを使う前提です。某大手FPGAメーカのツールだと、商用ツールにインタフェースできるのは勿論、商用ツールには劣るもののバンドル版のシミュレータを含んでいたりもするのですが、Tang Dynastyにはありませぬ。

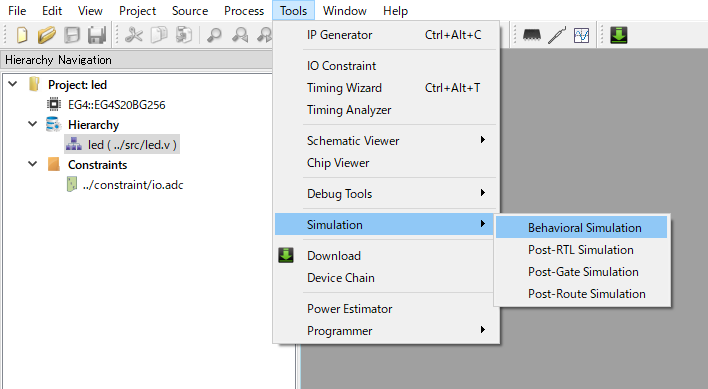

とりあえず、論理シミュレータへの接続機能を見てみます。Toolsメニューの下にSimulationがあり、その中に選択が4つありました。

このメニューは、上のFPGA Flow画面の中の、HDL2Bit Flowに対応していて、Read Designの状態であると、ほぼ素のままのRTLを使ってBehavioral Simulationに対応しており、合成の段階を経るにしたがって実装の検証のためのコードが取り出せるようになっています。当然、先に進めば進むほど、シミュレーションにもFPGAの実装に依存した「ライブラリ」が必要になってきます(各段階で必要になるライブラリのソースはツールのインストール配下に段階毎のフォルダにわけて入っていました)

さて、商用ツールを使わずにシミュレーションを行うために思い付いたのが、以下のツールであります。以前にもインストールしてみたことはあったものの、本格的に使ったことはありません。

さて、インストールにあたっては、ソースからビルドする手間を避け、以下のサイトからIcarus Verilogのバイナリ・インストール・パッケージをダウンロードさせていただいて、使用させていただきました。なお、パッケージにはIcarus Verilogだけでなく、GTKWaveも含まれているので1つでシミュレーションに必要な環境ができあがりました。

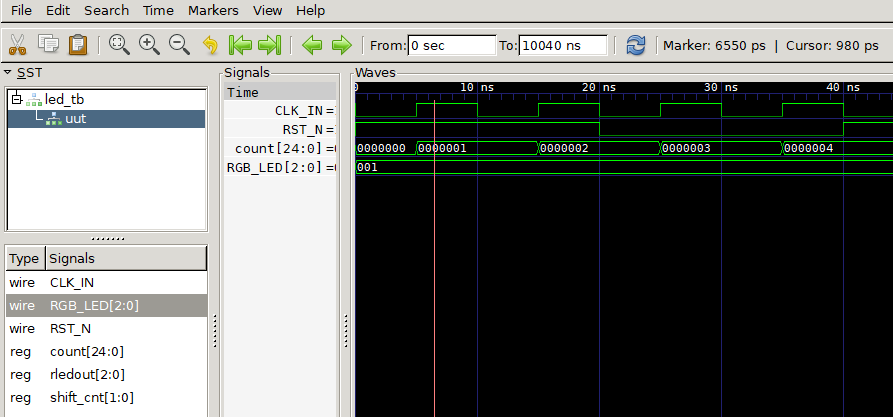

さて、Tang Dynasty上で、前々回FPGAへダウンロードしたLチカのサンプルプロジェクトについてBehavioral Simulationを選択してみました。simulation用のソースを入れるためのディレクトリには、以下の名前のテストベンチ用のファイルが一つ生成されました。

led_tb.v

本体の led.v については、とくに変形も加わっていないので、そのまま使えということのようです。当然ですが、テストベンチのファイルにはスティミュラス的なものは書かれておらず、自分で書け!ということであります。

テストベンチの「空っぽ」ファイルの後半に自分で書き加えたものがこちら。

//Stimulus process

always #(PERIOD / 2) CLK_IN <= ~CLK_IN;

initial begin

//To be inserted

$dumpfile("led.vcd");

$dumpvars(-1, uut);

$monitor("%b", RGB_LED);

RST_N = 1;

CLK_IN = 0;

#(PERIOD * 2);

RST_N = 0;

#(PERIOD * 2);

RST_N = 1;

#(PERIOD * 1000);

$finish;

end

Lチカ用のテストベンチの内部で、以下のようにglblというFPGAの初期化?モジュールを呼んでいるのですが、Tang Dynastyのインストールディレクトリ内のsimフォルダ内で該当のモジュールが直ぐに見つかったので、それをコピーして使いました。必要なモジュールをそろえてライブラリ化するような方法は宿題であります。ただ、今回は、素のRTLのままなので、このモジュールをコメントアウトしてもシミュレーション上は問題ないようでした。

//glbl Instantiate glbl glbl();

さて、

- iverilogコマンドでVerilogコードをコンパイル

- vvpコマンドで、コンパイル済のオブジェクトをシミュレーション

- GTKwaveコマンドでシミュレーション結果を表示

という段取りであります。今回は、テストベンチの中の$dumpfileで led.vcd なるファイルにシミュレーション結果を格納するようにしたので、これを開きます。

シミュレーション動きました。が、RST_Nのところ、何か変でないかい。。。

シミュレーション動きました。が、RST_Nのところ、何か変でないかい。。。

残りはまた次回だな、Tang DynastyでGateレベルに落とした後で再度シミュレーションしてみますか。