前回、Verilogを使えるようにしたので、さらに歯止めが効かなくなりました。普通なら、Verilog書いて、シミュレーションしてOKなら、論理合成デス。でもま、今回商用ツール使っている分けでもなく、またゲートレベルなので合成は無理、と思っていたら、面白いツールがありました。LogicFridayとな。

※かえらざるMOS回路 投稿順 INDEX

Logic Friday

Logic Fridayは、組み合わせ回路のミニマイズ(論理圧縮)と、ゲートレベルへのマッピング(合成)を実行してくれるフリーウエアです。論理圧縮の裏で動いているのはEspressoという、確か加州立大バークレーあたりで開発されたソフトウエアです。私も1980年代くらいにちょいとお世話になった記憶があるもの。ゲートレベルへのマッピングも同世代に開発されたものではないかと。

LogicFridayは、それらのフロントエンドGUIに見えます。便利なのですが、以下のポップアップのURLにアクセスするとセキュリティの警告が出ます。ううむ恐ろしいな。かなり古いソフトなのでネットを検索するとダウンロードできるサイトが複数あります。私はご本家でないところから降ろしました。今のところ問題でてませんが。。。

お試しのターゲット回路

今回お試しは「3名様の多数決」回路です。3人のうち2人以上が賛成したら、賛成という信号が出る回路です。簡単な組み合わせ回路。そのうち時系列信号のタイミングを変えてサンプリングした値に対して多数決を取る予定なのですが、今回は単純、同一タイミングでの処理です。

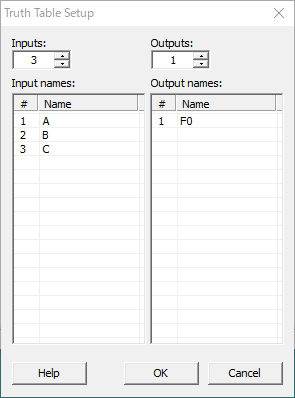

3入力1出力の組み合わせ回路となるので、真理値表で定義してみます。真理値表の設定はこんな感じ。

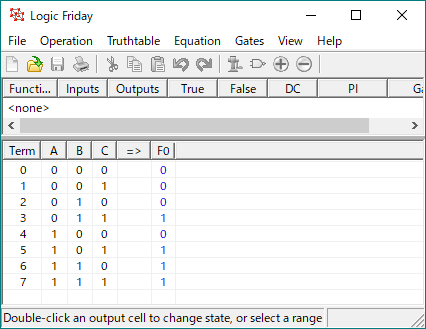

全てのケースを列挙したケースが以下に。ま、入力は簡単。

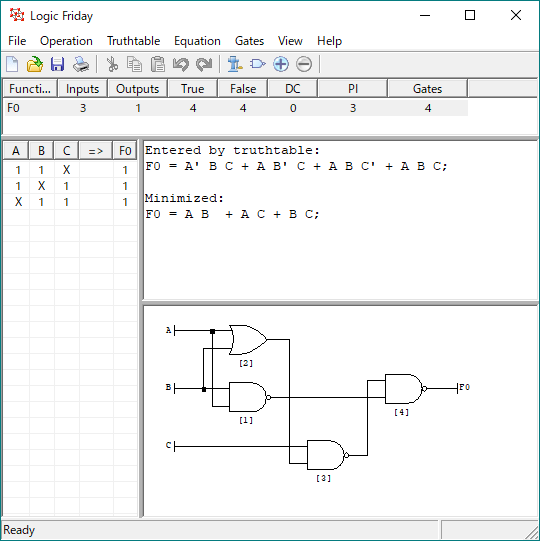

上記のテーブルに対して論理圧縮(Espresso)とゲートマッピング(misII)をかけたものが以下に。標準ロジックIC向けのマッピングとか選択肢があるのですが、今回は「ウエハ面積最小」向けとしてみました。ホントか?

ゲートレベルの回路が出来たので、これをLogicSimに持っていけばゲートレベルでシミュレーションできるはず。しかし、今回は前回の余勢をかってVerilogで「検証」してみることにいたしました。たかが4ゲートだぞ!

Verilogでのゲートレベルモデル

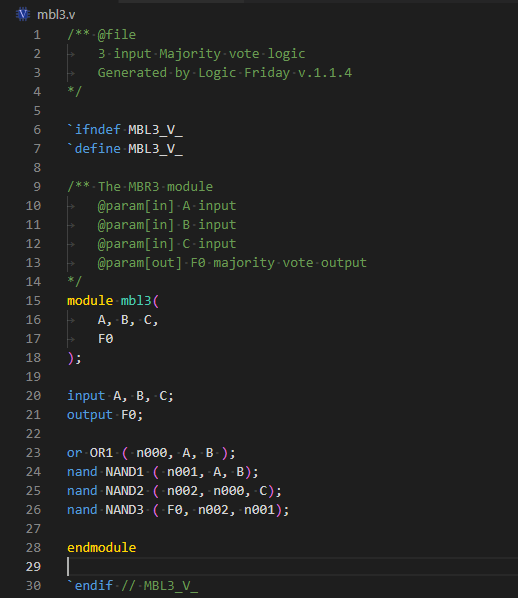

上記で生成された3人多数決回路を「ゲートレベル」でVerilog化したものが以下に。

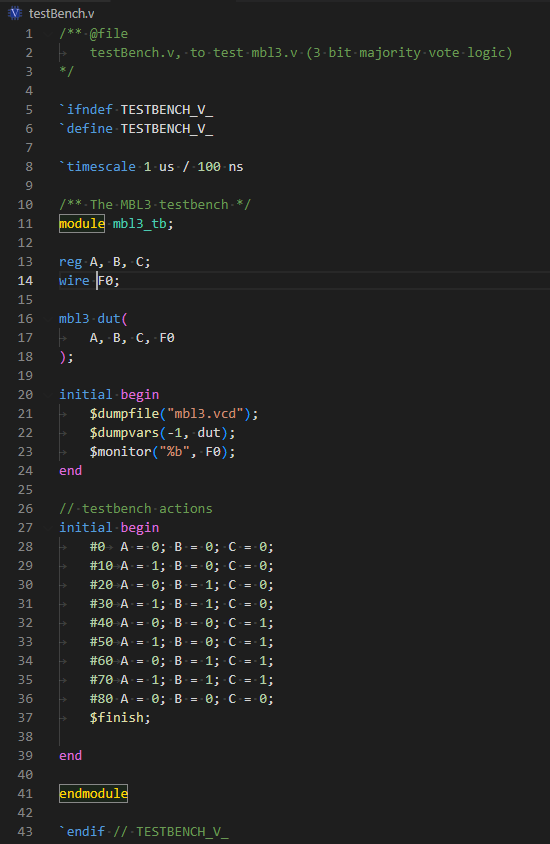

上記の回路を動かしてみるテストベンチが以下に。

動作検証

上記2ファイルを用意したら、フリーのIcarus Verilog と、これまたフリーのVCDビューワー gtkwaveで動作を確認いたします。

$ iverilog -o tb.out testBench.v mbl3.v $ vvp tb.out $ gtkwave mbl3.vcd

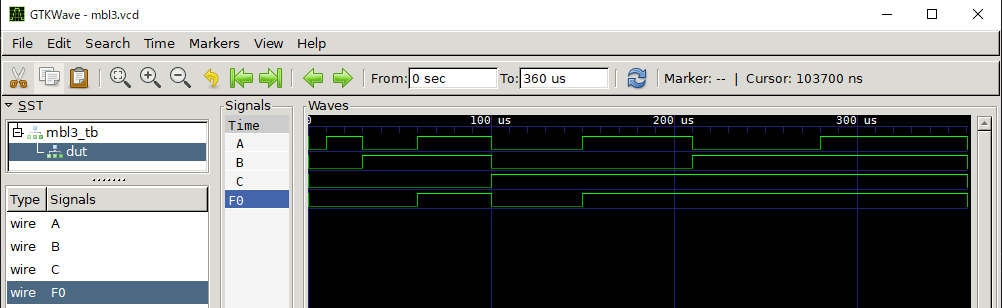

gtkwaveの表示する波形はこんな感じ。

多数決は大丈夫だけれども、gtkwaveの表示する時間ステップがなんか変な感じがしないでもない。調べないと。