前回Verilogで古の8080用2相ノンオーバラップクロック生成をシミュレーション。シミュレーションできたからにはFPGA上に実装せずにはいられませぬ。手元にあるFPGAボードは「お求めやすかった」けれども「既に販売されていない」某国製品です。新規購入と思いつつ、大したロジック作るわけじゃないと思うと手が出ませぬ。

※かえらざるMOS回路 投稿順 INDEX

『Tang Dynasty』の復活

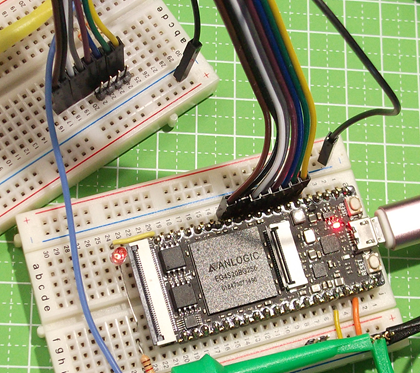

FPGA用の開発ボードというと数万円くらいはお求めやすい方、数十万円くらいはフツー、という中で、手元にありましたのは以下の別件記事で使っておりましたANLOGIC社のFPGA搭載のもの。数千円台も下の方でした。

3年くらいホコリを被っていたのは他でもありません、ちょっと何か調べようとすると中国語(簡体字の方ね)に向き合わないとならなかったためです。まあ、Google翻訳等が使えるとは言え、辛い。

とりあえずVerilog書いたものをFPGAに焼いて動作させるくらい簡単だろ~と。まあ操作そのものは簡単ではあったですがいろいろ問題もあり。

-

- 3年前は秋月殿で販売されていたが既に終了

残念なことに既に販売終了していました。理由は不明。

-

- Windows11PCに開発環境 Tang Dynastyをインストールしようとしたが問題あり

3年前とは常用のパソコンが変わっているので、開発環境を新しい方のPCにインストールしようとしたら問題ありました。開発環境のダウンロード自体はできた(ただし3年前とバージョン変わってないです。メーカも力が入ってない感じ。。。)のですが、ソフトが MSVCR100.dll 依存で現環境では立ち上がりませぬ。何時の時代のソフトだ。DLLをインストールすることも考えましたが、あんまりやりたくないです。3年前に開発環境インストールしたパソコンは今も補助機として働いているので、そちらを使用することにいたしました。

やはり入手性が良く、ドキュメントも整っている米国製FPGA製品を仕入れるってもんだな。でも予算は無いし。。。

-

- ライセンスファイルは配布されていた

開発環境 Tang Dynastyですが、CADツールではよくある「一定期間毎に」ライセンスファイル(無料)をダウンロードして更新しないと動作しないようになってます。配布は続いているのか?メーカサイトへ行ったところ来年3月までのファイルをGET。やったね。でもいつまで続くのか?既にソフト本体の更新止まってるし。。。

ということで旧PC上でFPGA用のビットファイルを生成してダウンロード。

書き込んだファイル

折角、前回Verilogシミュレーションしたというのに、実際にFPGAに書き込んだファイルはチンマリした別ファイルになってしまいました。PC2台の間でファイルを転送してシミュレーションしてまた戻してというような手数がメンドかったのよ。。。マシンを分けた弊害が如実。

実際に使ったVerilogソースが以下に。前回のシミュレーションの時よりも2相の「隙間」時間を空けるように調整してます。これは実機で動作させてみていかにも隙間が空いているように見せたかったがためであります。

module count12

(

input wire CLK_IN,

input wire RST_N,

output wire P1,

output wire P2

);

reg [3:0] count;

reg phase1;

reg phase2;

initial

begin

count=4'b0;

phase1=0;

phase2=0;

end

always @(posedge CLK_IN)begin

if(RST_N==0)begin

count <= 4'b0;

end

if(count == 4'b0001)

phase1<= 1;

if(count == 4'b0101)

phase1<= 0;

if(count == 4'b0111)

phase2<= 1;

if(count == 4'b1011)

begin

count<= 4'd0;

phase2<= 0;

end

else

count <= count + 1'b1;

end

assign P1 = phase1;

assign P2 = phase2;

endmodule

なお、遅延の制約等は一切かけておらず、成り行きのままの実装です。お気楽。制約ファイルはIO端子の設定のみ。

set_pin_assignment {CLK_IN} { LOCATION = K14; } ##24MHZ

set_pin_assignment {RST_N} { LOCATION = K16; } ##USER_KEY

## CLOCK OUT

set_pin_assignment {P1} { LOCATION = E16; }

set_pin_assignment {P2} { LOCATION = F16; }

実機実験結果

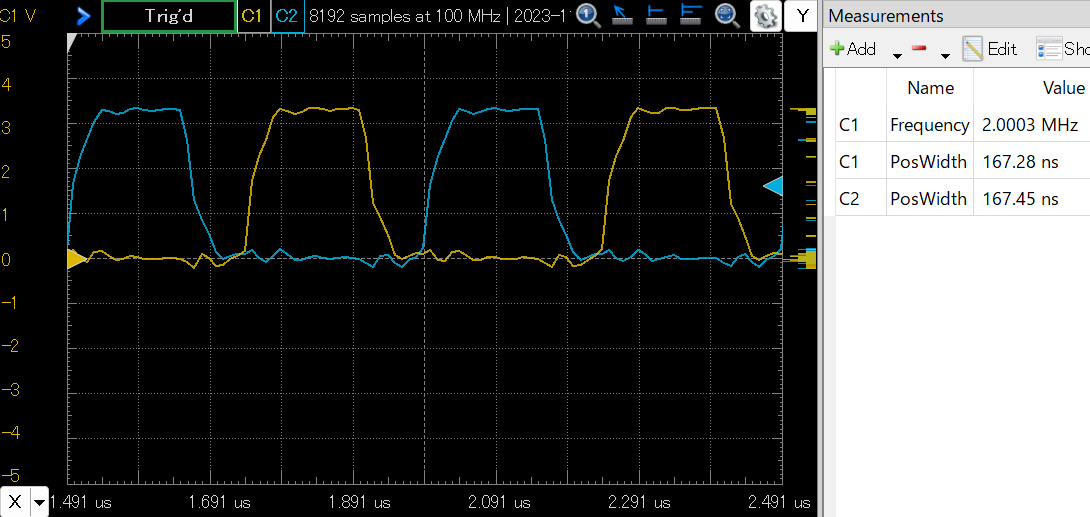

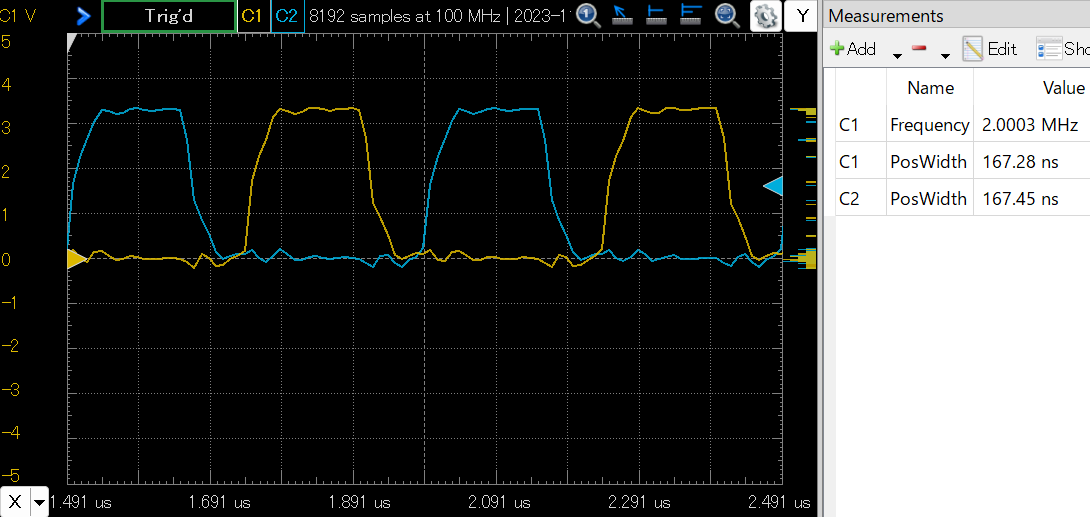

ボードにビットファイルを書き込んで動作させているところが以下に。

写真ではワイヤに隠れていますが、P1、P2出力の先に330Ωの抵抗を介してAnalog Discovery2のオシロ端子に接続して波形を観察してます。

「ことさらに隙間」が空いて2相ノンオーバラップクロックっぽい波形にできました。周波数も2MHz。でもちょっとハイ期間が短いのでないかい。8080のスペックだとP1、P2は非対称。P1は最小60nsでもよいけれど、P2は最小220nsみたい。。。パルス幅の調整が必要だな。