前回「パルス幅の調整が必要だな。」などと書きながら、メンドくなってそのまま投げてました。先へ進めるまえに前回の後始末をしておくべし、と。今回は8080のクロック仕様に合致させるつもりで回路を微調整するだけであります。現場合わせ、成り行き感。。。良いのかそんなことで。

※かえらざるMOS回路 投稿順 INDEX

「お求めやすい」けれども肝心なところが簡体字中国語でよく分からないANLOGIC社のFPGAとその開発ツール『Tang Dynasty』(唐王朝ということでありましょう)に「時々思い出したように」取り組んでおります。今回は前回のチョイなおし、ホント、数字をチョイ変えるだけ。

前回の問題点

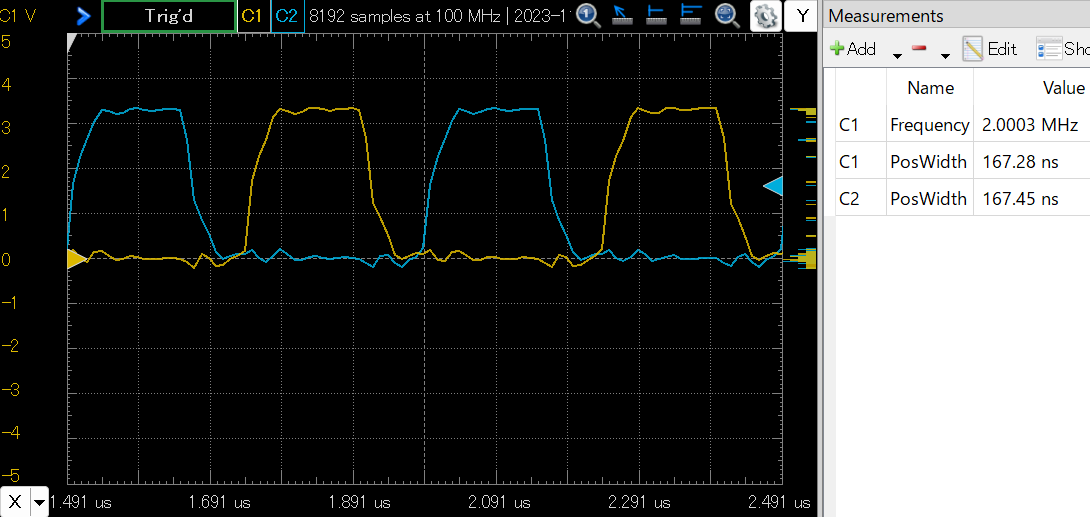

前回、古代のベストセラーチップ、8080に与える2相ノンオーバラップクロックを生成してみました。「ノンオーバラップ」部分はしっかり隙間を確保できていたんでありますが、アクティブ期間に問題があったのであります。前回波形はこんな感じ。

問題点は、右のPosWidthのうちP2(上記では青色C2波形)です。8080のスペック的には「最小220ns」みたい。C2の幅をもっと広げないと。でも、そんなことをすると隙間が無くなるのでは?「ノンオーバラップ」の隙間は隙間で上記の幅は維持したいし。それがご無体な要求でないのは、もう一方のクロックP1(上記では黄色C1波形)のパルス幅、最小60nsでいいみたい。C2の幅をバッサリ削って、その分をP2へ回せば一件落着の筈。

修正したVerilogコード

修正というほどの修正でもないのですが、短いのでそのまま全文載せておきます。こんな感じ。

module count12

(

input wire CLK_IN,

input wire RST_N,

output wire P1,

output wire P2

);

reg [3:0] count;

reg phase1;

reg phase2;

initial

begin

count=4'b0;

phase1=0;

phase2=0;

end

always @(posedge CLK_IN)begin

if(RST_N==0)begin

count <= 4'b0;

end

if(count == 4'b0001)

phase1<= 1;

if(count == 4'b0011)

phase1<= 0;

if(count == 4'b0101)

phase2<= 1;

if(count == 4'b1011)

begin

count<= 4'b0;

phase2<= 0;

end

else

count <= count + 1'b1;

end

assign P1 = phase1;

assign P2 = phase2;

endmodule

実機確認

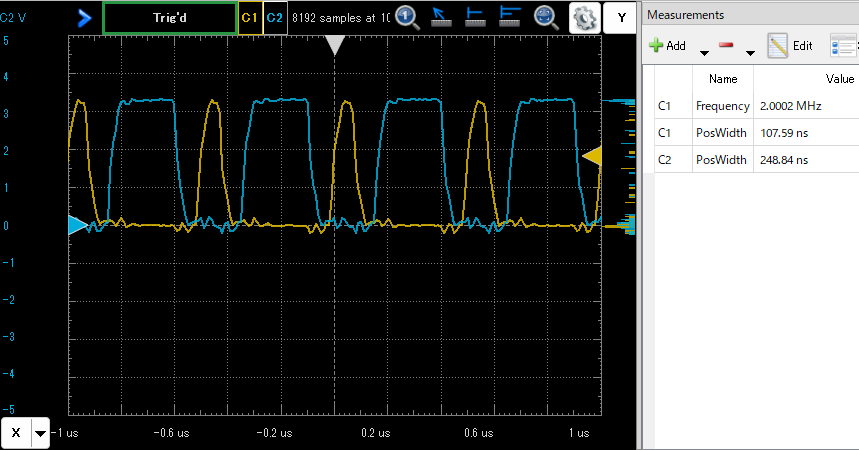

上記のソースを「エラボレート」してFPGAに書き込み、観察したP1、P2の波形が以下に。

P1が細くなり、P2が太くなりました。P1の幅は100ns超えているし、C2の幅は250ns近くあります。スペックは満たせた?といって手元に8080ないので動かしてみることは出来んけど。