超小型FPGA開発ボードDigilent CMOD S7導入。本流FPGA開発ツールAMD Vivadoを使って何度か練習するうちに「設計できるかも」的根拠のない自信?が忘却力の年寄にも芽生えております。今回はついにCPU‐IPなどを搭載、ハード、ソフトの複合プロジェクトに挑戦?チュートリアル通りだけれども。

※かえらざるMOS回路 投稿順 INDEX

※Digilent CMOD S7のマニュアルは以下のページにあります。

なお、CMOD S7搭載のFPGAは「多分、お求めやすい」XC7S25-1CSGA225Cです。

※実習には AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

プロセッサコアIPの搭載設計

CMOD S7ボードは普及価格帯の比較的小規模なFPGA搭載とは言え、プロセッサIPを使うことができるみたいです(ただしハードウエアのArmコアなどは搭載しないのでソフトコアだけね。)Xilinx社が提供してくれているソフトコアはMicroBlazeというコアです。お楽しみだね。

さてFPGA開発ツールVivadoはMicroBlazeコアを使った設計にも対応しておるのですが、できたハードウエア上に書き込んで走らせるソフトウエア開発についてはVitisというツールを使うみたいです。年寄の勝手な理解では以下のような開発ステップみたい。

-

- 先にVivadoでハード設計をする

- 続いてVitisでソフト設計をする

- 2つ合わせてFPGAに書き込む

Digilent社はプロセッサIPを使った場合についてもチュートリアルを準備してくれています(MicroBlazeだけでなくArmコアにも対応。)

Using the Simulator Getting Started with Vivado and Vitis for Baremetal Software Projects

上記にそって実習していけば、Lチカ的なことをMicroBlazeコアのシステム+Cソースのソフトで出来るハズ。まあ先は長そうなので、今回はVivadoでハードを設計してそれがバリデーションを通るところまで。

ハードの設計?ステップ・バイ・ステップ

ハードの設計と言ってもチュートリアルの通りにやってみているだけ。ソースを書くこともほぼ無で「ブロック・ダイアグラム」ベースで設計が出来ていきます。

まずは普通にVivadoでCreaste Projectして、「ほぼ空」のプロジェクトを作ります。以前の回で何度かやっている通りですが、何もソースファイル等は加えず。ただしターゲットボードをCMOD S7にすることだけは忘れずに。

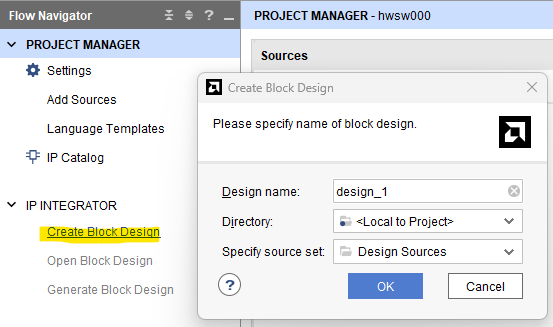

続いて IP INTEGRATORのところから Create Block Disignをいたします。こんな感じ。

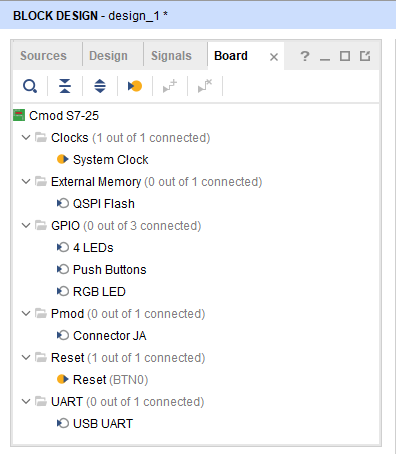

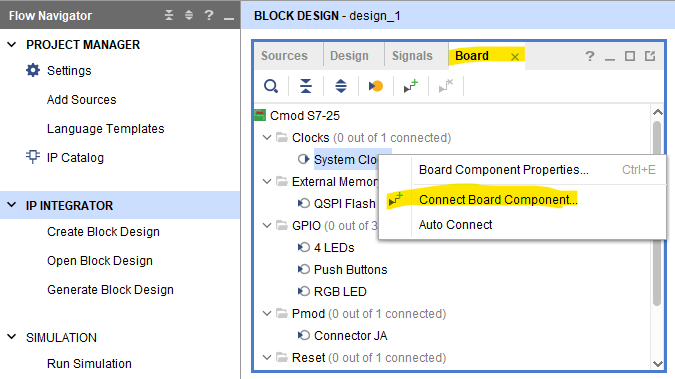

上記で生成したBLOCK DESIGNの中に「ブロック」を配置していくのですが、最初はシステム・クロックからです。BLOCK DESIGNの中の「Board」という名のタブを開くと CMOD S7に固有のハードウエアが自動で拾われて既にリストされていることが分かります。その中のSystem Clockを右クリックしてConnect Board Componentというコマンドを走らせてみます。

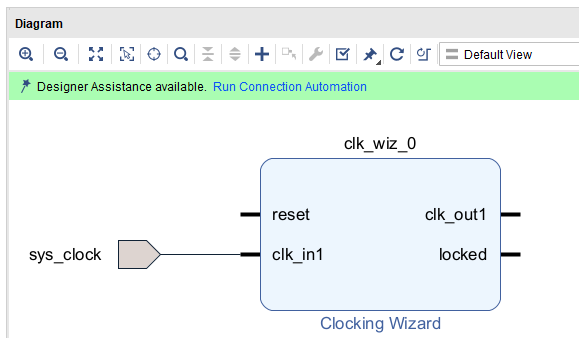

Diagramウインドウの中に以下のようなブロックが忽然と現れます。

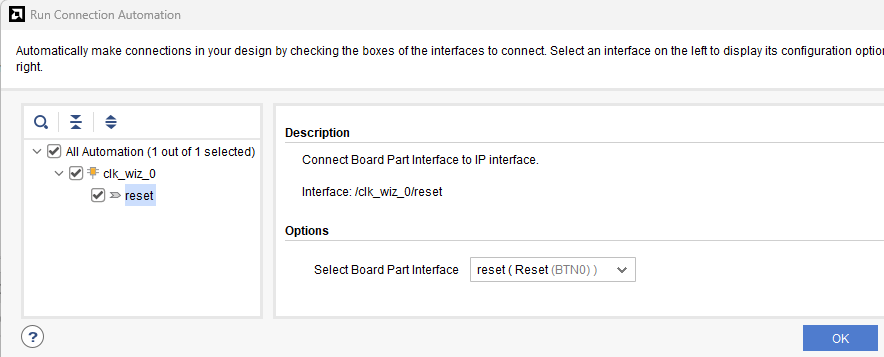

上記の画面の上の方に「緑の帯」でRun Connection Atumationというものが見えます。どうもこれを走らせると「未結線の信号」をよきに計らって接続してくれるようです。この状態で走らせてみます。すると reset端子にボード上のBTN0を接続しようとしてくれているみたい。

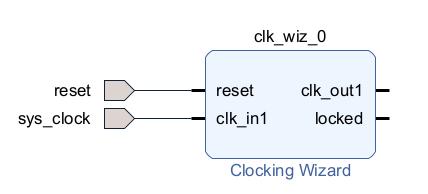

「お任せ」注文すると、以下のようになりました。繋がっている?

念のためこの時点のBoardタブの様子をみると以下のようです。接続済のボードハードウエアにはオレンジ色のマークが入ってます。

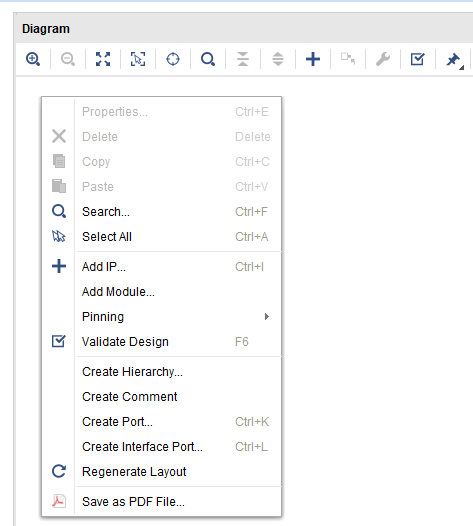

さていよいよ MicroBlazeコアを配置せよ、との思し召しです。Diagramウインドウ上で右クリックすると現れるメニューから Add IPしてみます。こんな感じ。

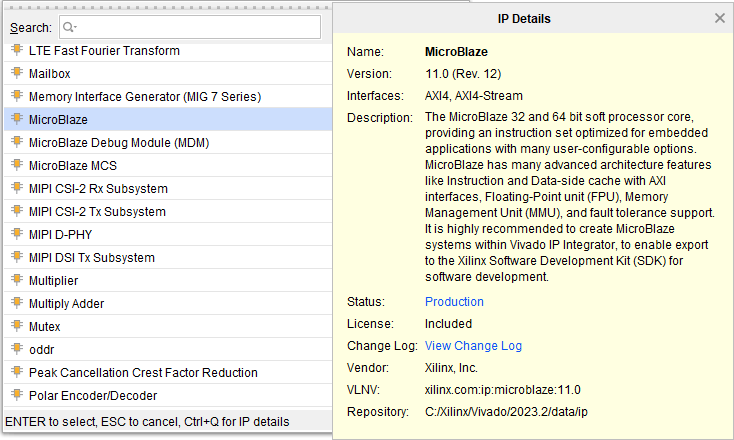

するとIPの一覧がこれでもかと現れます。選択してCTRL-Qすれば以下の黄色背景の画面のように各IPの説明も読むことができます。

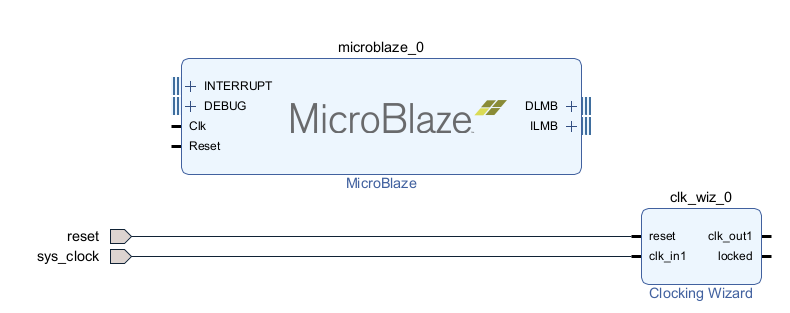

MicroBlazeコアを選択したところDiagram内に忽然とMicroBlazeコアが現れましたぞ。

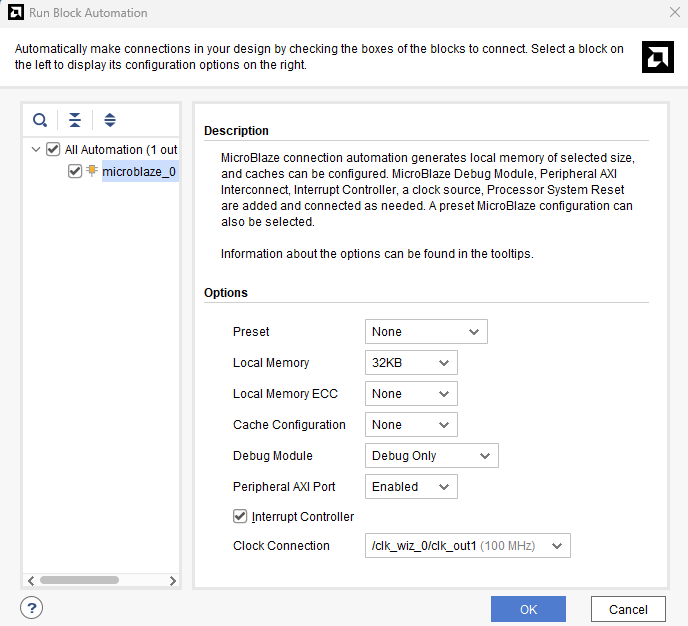

ここで再び Run Block Automation すると以下のような設定画面が現れました。

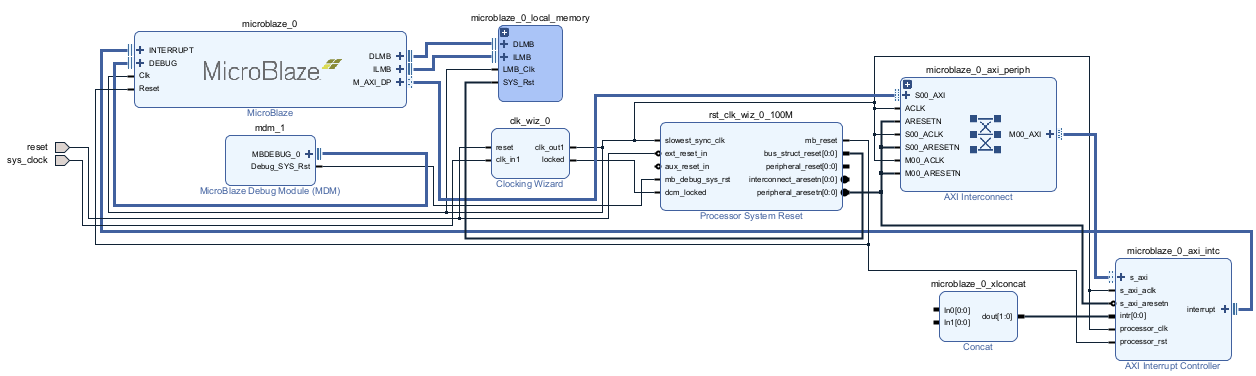

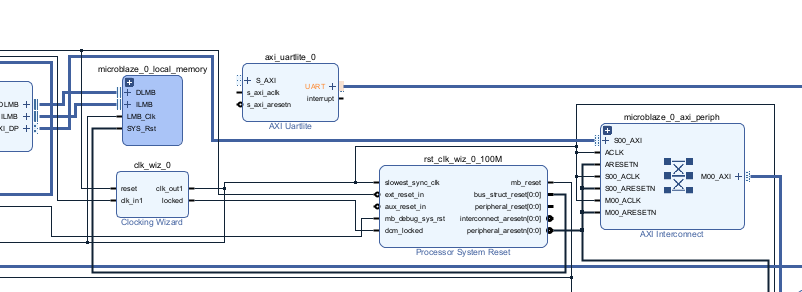

上記のように設定して、OKを押すと、ほれこのように急に賑やかになりました。

メモリやら何やら各種のブロックが一気に登場。

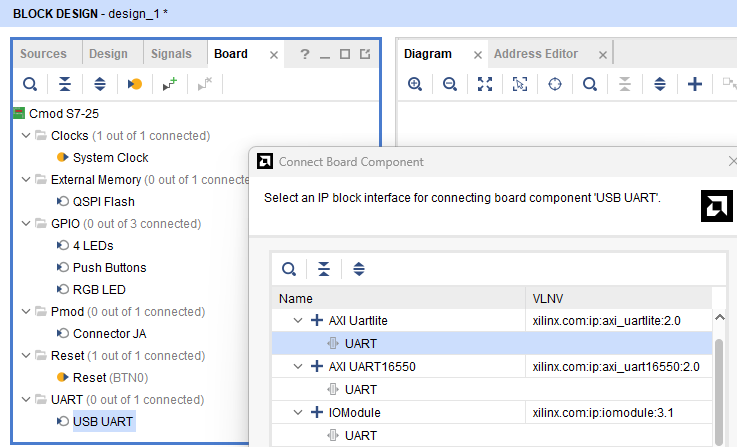

さらにUSB UARTをここへ加えよ、との思し召しあり。USB UARTは先ほどのボード・タブ上にリストされているのでここから接続します。UARTとしては複数のIPが使用可能みたいですが、チュートリアルの説明どおりAXI Uarliteというタイプを選択。

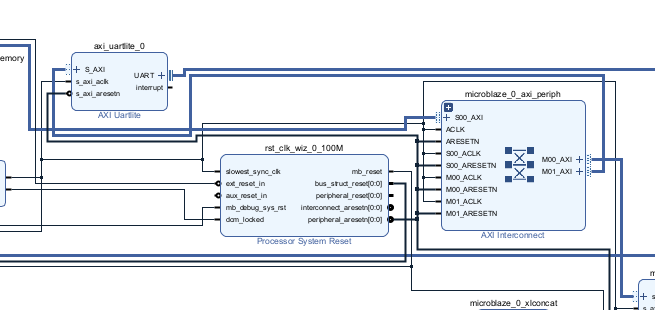

以下のようにUartliteブロックが登場しました。行先はボードハードウエアの端子に自動接続接続されているみたいですが、まだAXIバスとは未接続みたい。

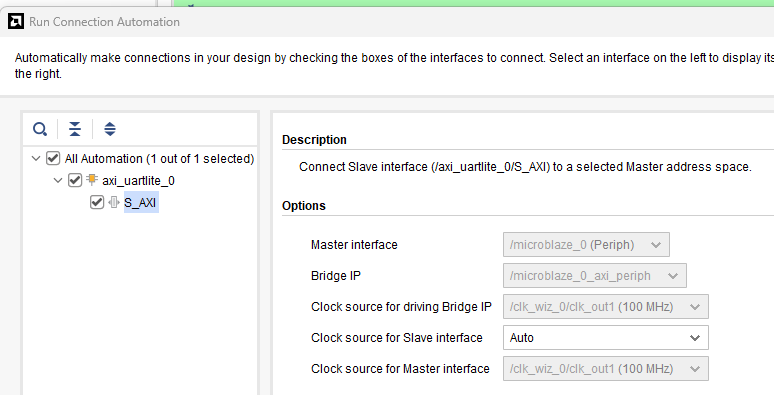

例によって Run Connection Automationを使うと「よきにはからって」くれます。

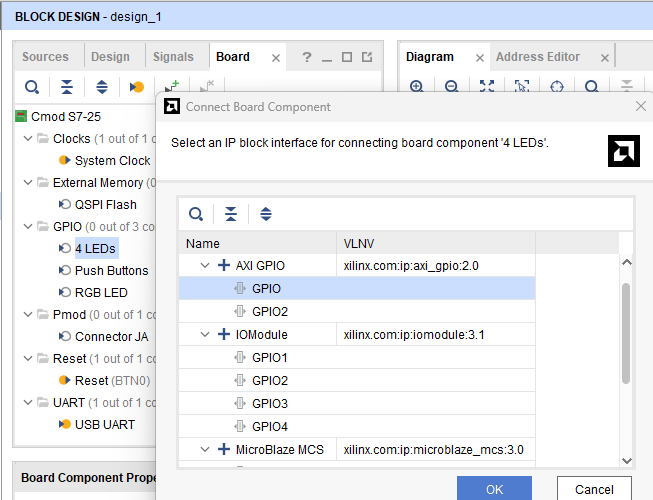

もひとつ、「Lチカ」の出力に使うのであろう、LEDに接続するGPIOブロックを加えねばなりません。LEDもBoardタブにリストされているので、同様に「お任せ」接続が可能。

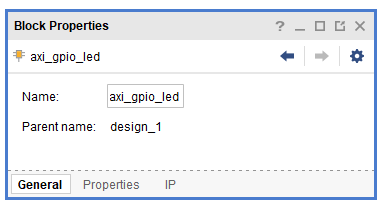

チュートリアルによると、以下のようにブロック・プロパティからNameは「分かり易い」お名前に変更しておけ、とのレコメンデーションあり。後でVitisを使ってソフトを記述するときに、このお名前を参照する必要があるからみたいです。知らんけど。

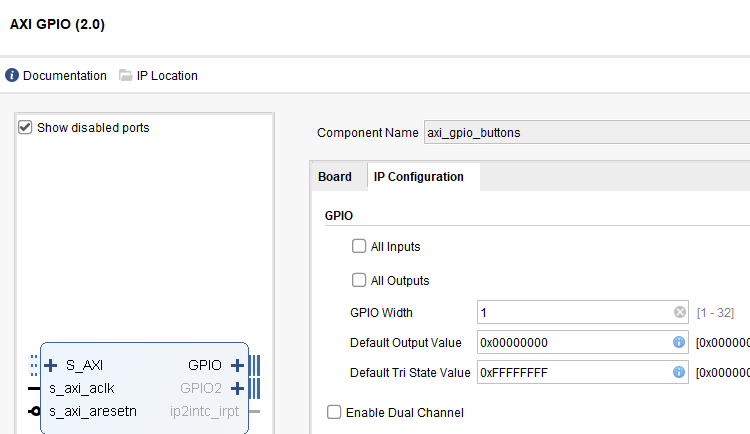

さらに、チュートリアルではBoardタブを使わず、ブロックを追加してハード接続する方法もお教えくださってます。題材はもう一個のボタン(1個目のボタンはResetに使ってしまっている模様。)Add IPし、Nameも変更したところが以下に。

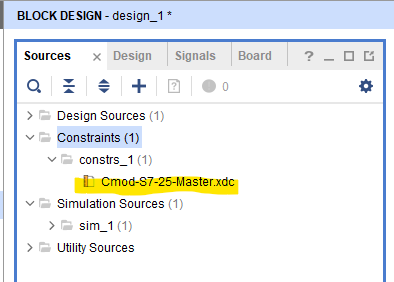

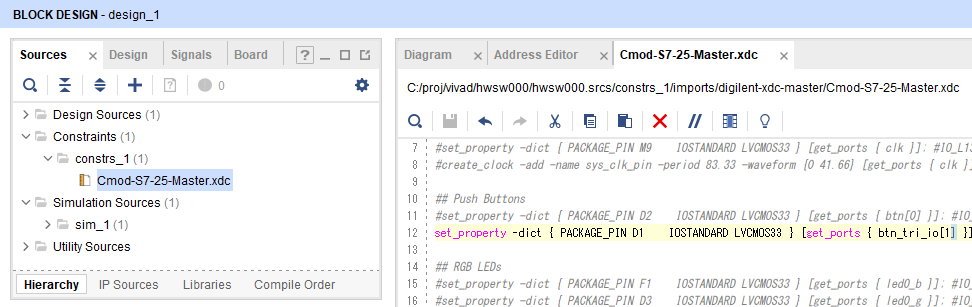

ここで、前回まで毎度やってきた制約ファイル(Constraints)をAdd Sourceで追加します。以下はDigilent供給の制約ファイルをCOPYでとりこんだところ。

制約ファイルの内容のうち、BTN1に接続部分のコメントを外し、またお名前も変更してみました。BTN0がRESETに使われているので、btn[1]の方だけをお名前変更してみてます。でも「1」だし。この部分、良く分かってないデス。ちゃんと動くか心配。まあ実際に上手く動かないようなら戻ってきて修正する予定。

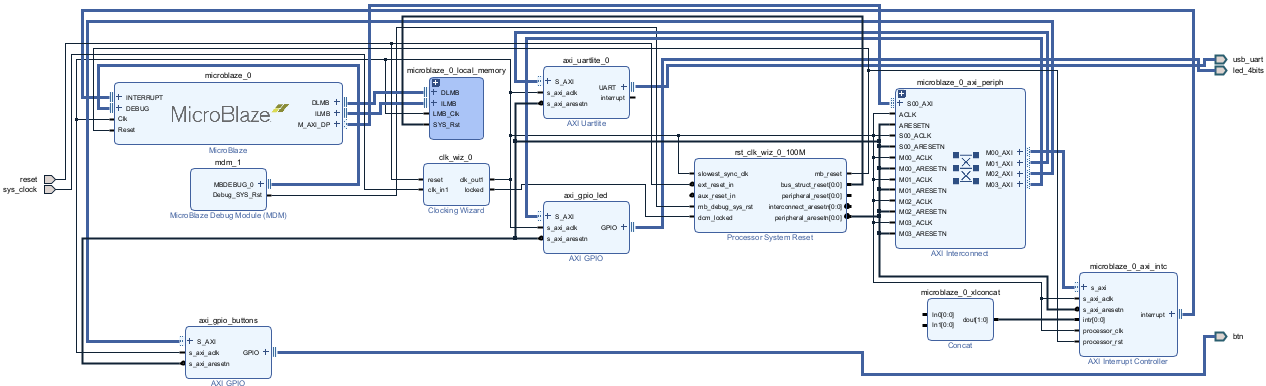

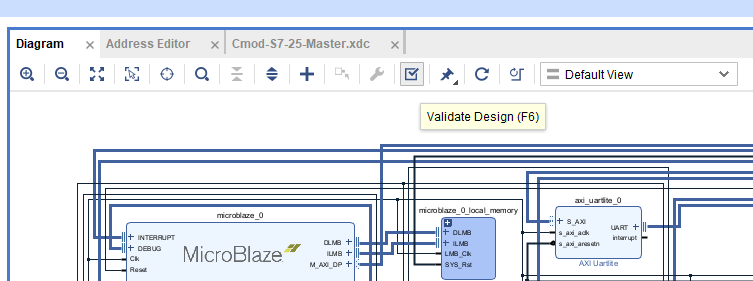

ここまで全てを結線した後の様子が以下に。GUIをクリクリしているだけで結構なブロックダイアグラムが出来てしまうっと。

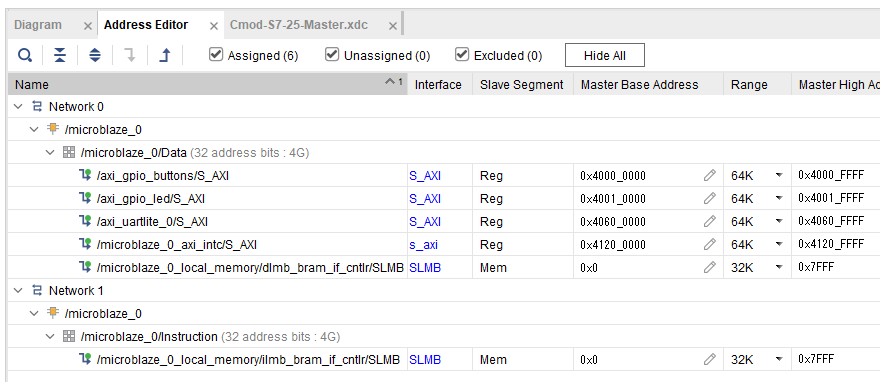

続いて「アドレスマップ」の指定。Digilent社のチュートリアルを読むと、自動設定してくれないので手動で設定すべし、と書いてあるのですが、Address Editorタブを開くと以下のようにアドレスは全て設定済でした。最近のバージョンアップで自動設定されるようになったんじゃろうか?

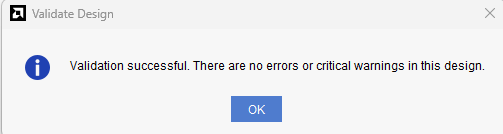

さて、ようやくハードウエアを一通りならべたので、ダイアグラムの上の方にあるValidate Designボタンを押してみます。ドキドキ(不整脈か?)

以下のように、Validate Design通ったようです。

次回は、ハードウエア・デザインをVitis側にお伝えして、Lチカのソースを書くところだね。