前回「調査」から、Vivado内蔵IPの実地トレーニングは空プロジェクトを作って、そこに対象のIPを配置し、シミュレーションして、FPGAに書き込んでというプロセスを地道にやっていくことにいたしました。まずは「簡単そうな奴」からということで選んだのがBinary Counterです。これならFPGA素人老人にもできる?

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい?Spartan-7搭載の超小型開発ボードです。

Binary Counter

以前にもバイナリカウンタを練習した気がしてますが、今回のはVivado内蔵のIPの利用です。Create projectで空のプロジェクト(ターゲットボードはDigilent Cmod S7)を作り、Create Block DesignでIPを配置できる「土俵」を開きました。そこで右クリックからAdd IPすると配置できるIP群が大量に列挙されます。IPを選択し、CTRL-Qすると説明が現れます。こんな感じ。

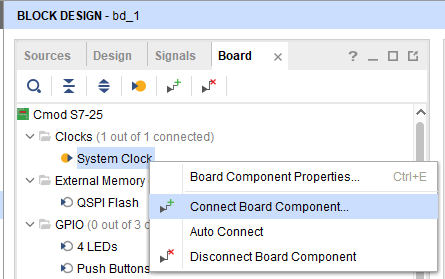

沢山列挙されているIPの中で、一番簡単そうなIPがこれでした。まずは、空のブロックダイアグラム画面にBinary Counterを配置、つづいて流石にクロックを接続しないとカウンタ動かんだろ~ということでBoardタブからオンボード搭載のSystem Clockを接続するようにお願いしてみます。こんな感じ。

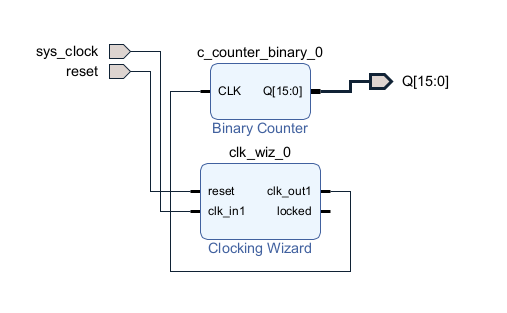

お任せでSystem Clockを接続したら Clocking Wizard というIPも自動で取り込まれてました。そこにはreset端子もあったので、これまたボードタブからreset信号もお任せ接続。お任せの自動接続で生成されたブロックダイアグラムの出力線Q[15:0]だけ手動でお名前をつけたものが以下に。

こんなもんだが。。。

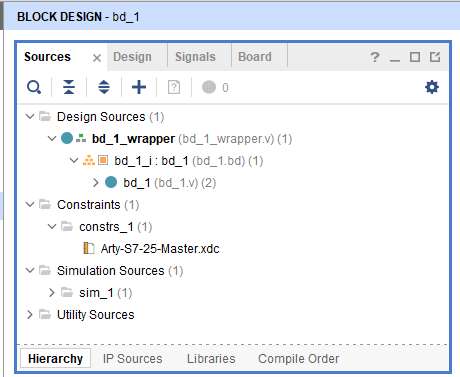

ラッパを自動生成

ブロックダイアグラムができたので、「ブロックデザインのオレンジ色アイコン」を右クリックして現れるメニューからCreate HDL wrapperしてみます。するとオレンジ色アイコンの上下にHDLソースが生成されました。以前もやったな。

ビットストリーム生成

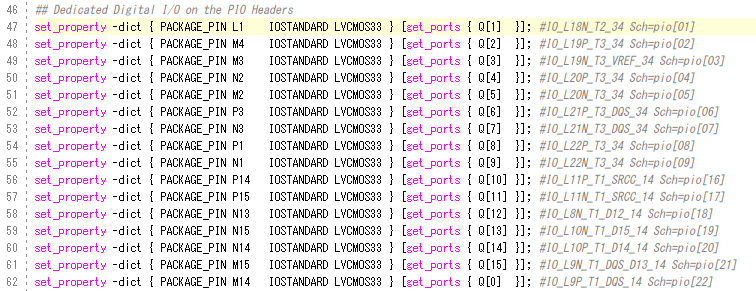

上記の状態でシンセシスとインプリメンテーションまでは出来ますが、ビットストリームの生成は出来ません。出力信号Q[15:0]の行先が決まってないからです。そこで、Cmod-S7の制約ファイルを取り込み(COPY)し、端子にQの各信号を割り当てました。こんな感じ。

これで行先も確定、ビットストリーム・ファイルもできました。

これで実際にFPGAに書き込めるはずですが、まずは論理シミュレーション(ビヘイビア)して、動作を確認しないと。

シミュレーション

論理シミュレーション用のテストベンチファイルを作ってみました。こんな感じ。

module bd_1_tb(

);

reg clk;

reg rst;

wire [15:0] b_out;

bd_1_wrapper dut (

.Q(b_out),

.reset(rst),

.sys_clock(clk)

);

always #50 clk = ~clk;

initial begin

clk = 0; rst = 1;

#200; rst = 0;

#3300000; $finish;

end

endmodule

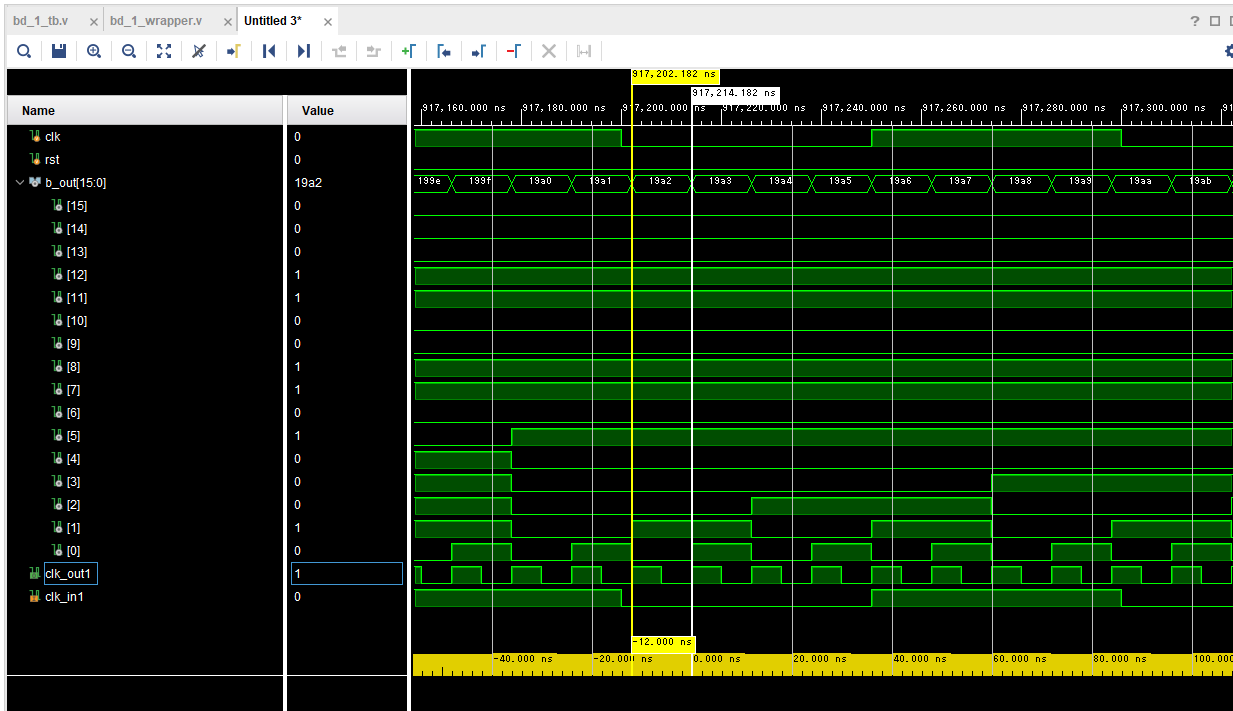

おやおや、バイナリカウンタに入力されているクロック、クロックウイザード・ブロックのclk_out1信号、入力のCLK(テストベンチ的には10MHz設定)よりもずっと早い(約86MHz)のでないかい。。。

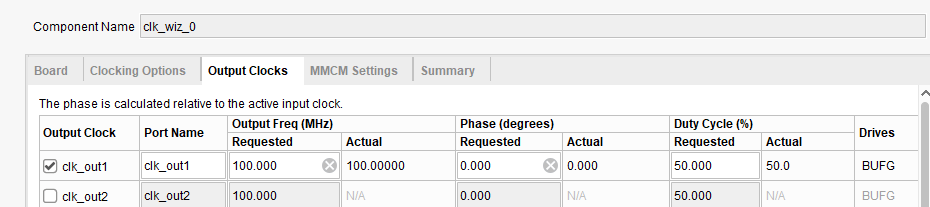

あれあれということで自動生成された Clocking WizardというIPの内部設定を見てみました。こんな感じ。

ボード上で準備されている system_clockは12MHzであり、その12MHzが入力されたときに100MHz(約8倍)が出力されるような逓倍機能が働いているみたいです。テストベンチでは計算がメンドイのでクロックを10MHzになるようにしてしまったので、結果的八十数MHzといったクロックで動作しているように見えたみたい。Binary Counterだけの練習のつもりが、逓倍回路も体験してしまった?

まあこのやり方でIP舐めていったらFPGAも分かってくるかいのう?