アナデバ社(ADI社)のWeb記事『StudentZone』の2024年3月号(和文版)実習2回目。アナログ素人の老人は全く気付いておりませなんだ。前回実習の「ディスクリート同調アンプ」チョイ変にて周波数逓倍回路となります。ミソは高調波が多く含まれる入力波形の選択。さすれば共振周波数の正弦波が出力されておじゃると。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

※学生でもないのに勝手に実習をさせていただいておりますアナデバ様の記事が以下です。アナデバ様的にはアナデバ製ADALM2000ツールを使って実習せよ、との記事ですが、当方持ち合わせなく、Digilent製Analog Discovery2利用であります。

今回は上記3月号の実習二回目。「周波数逓倍器」と見出しがついているセクションです。

以前に実習の逓倍回路

以前にも周波数逓倍器は練習してみてますが、PLL(フェーズ・ロックド・ループ)利用でした。以下は個別要素部品を組み合わせて16逓倍したケースです。

お手軽ツールで今更学ぶアナログ(145) 前回回路を改造、16逓倍PLLじゃ、ホントか?

また、以下の別シリーズではクラッシックで定番なPLL-IC CD4046 を使ってPLLしてます。

定番回路のたしなみ(19) CD4046でPLL(フェーズロックドループ)その1

どちらも高い周波数はVCO(電圧制御発振器)を利用して発振させておいて、入力クロックとフェーズ・ロックさせることで所望の逓倍数を得る回路でした。

今回の周波数3逓倍器

今回の回路で高い周波数を得る方法は異なります。前回実習のLC共振器をつかった同調アンプに対して「高調波を含んだ低い周波数の入力波形」を入力し、高調波の中から共振周波数に合致した周波数だけを選択的に増幅して高い周波数を取り出すものらしいっす。言われてみれば、という感じだけども、アナログ素人のお惚け老人はよう考え付かんなあ。

今回はとりあえず3逓倍を実験してみましたが、アナデバ様の記事を読むと5逓倍とかくらいまで出来そうな。。。

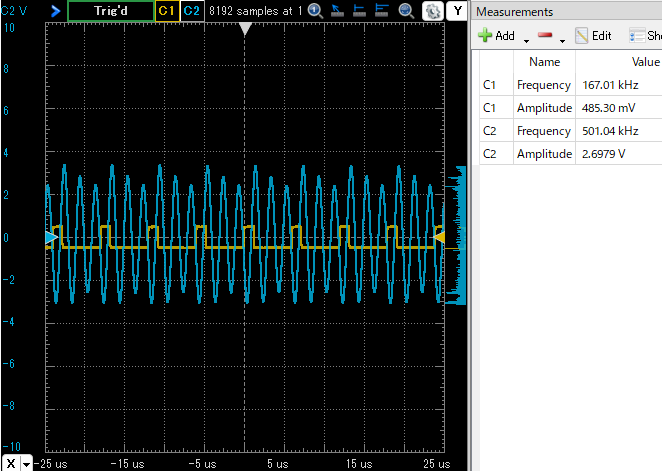

まずは実機で観察した波形を御覧じろ。黄色C1が入力の周波数167kHz、オフセット0V、振幅500mVの矩形波です。青色C2が出力の波形です。

出力波形をみると周波数は約500kHz。予定どおり3逓倍されているみたいっす。

回路とLTspice

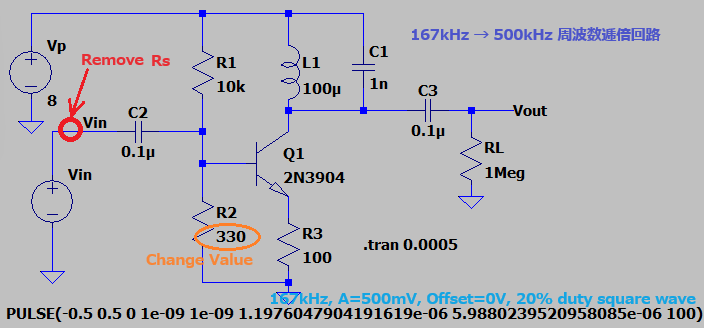

前回使用した回路と「ほぼ同じ」ですが、差分のところにコメントを書き入れてあります。

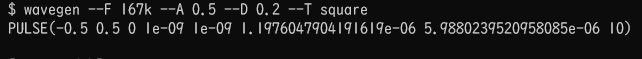

まず入力VinのところにあったRsを取り外してます。手加減することないためみたいです。R2の値は勝手に330Ωとしてみました。記事によると入力信号が無いときにQ1のIcをほぼほぼ0mAになるようにせよ、ということだったのでR2をテキトーに小さくすれば流れなくなるだろうという大雑把です。記事的にはちゃんとR1とR2を計算せよ、ってことみたいですが。そして最後に入力波形を「逓倍しやすい」波形に変更してます。妙に細かい倍精度数字で規定しているのは、いつものお手製ツール waveGen.py 使っているためです(本サイト内を検索していただければPythonのソースが見つかるハズ。)

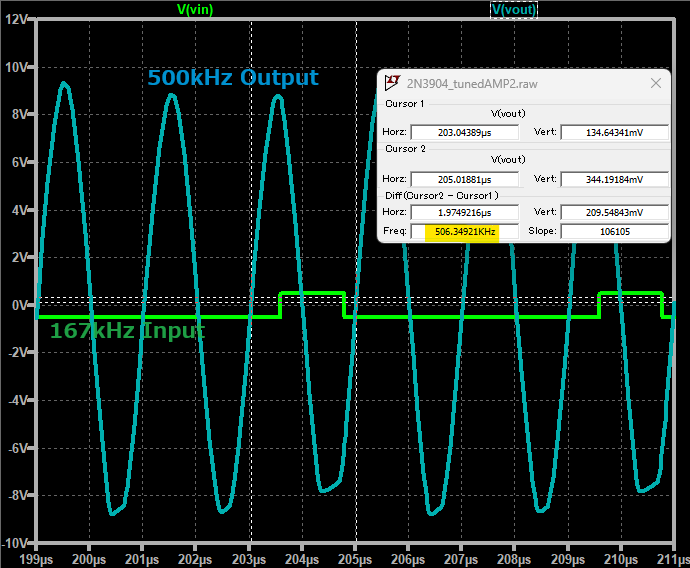

折角LTspiceで回路図描いたので、シミュレーションもしてみました。こんな感じ。

だいたい似たような感じ?シミュレーションの方がマイナスのピーク付近で歪んでいる感じ。実機だと結構綺麗な正弦波に見えますが。知らんけど。