前回まで「制約」constraints の設定のお勉強にはまり込み、しばらくFPGA実機を動作させていませんでした。忘却力の年寄はFPGAへの書き込みの仕方とか既に怪しいです。そういえば制約の件にハマり込む前に練習していたバイナリカウンタのIPの件、実機に書き込んでなかった気がする。そいつでリハビリ?

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

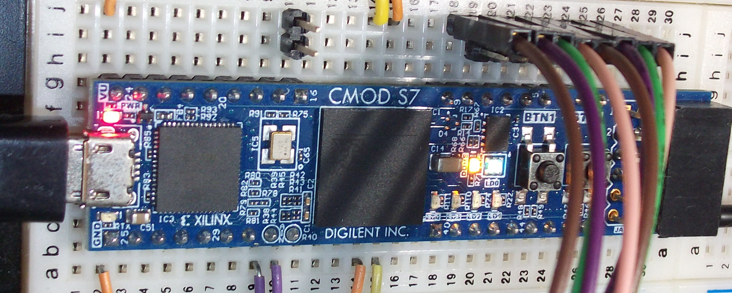

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい?Spartan-7搭載の超小型開発ボードです。

実機用にClocking Wizard設定を変更

シミュレーションまでやっておいて実機CMOD-S7ボードに実際に書き込んで動作確認していなかった件は以下です。

帰らざるMOS回路(56) Xilinx Vivado、クロッキングとバイナリカウンタ

Vivadoが内蔵するXilinx製のIPの中でも多分一番簡単じゃないかと予想した「バイナリカウンタIP」をぽろりんと1個置いて動かしてみようとした1件。Vivadoは多数のIPを内蔵しているので、これが動作したら後は芋ずる式に各種IPをずるずると引きずりだして使ってみようという遠大な計画の第1歩であります。

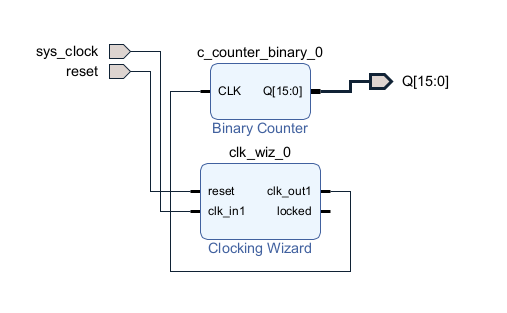

しかし、バイナリカウンタIPを一つポロリンとおいたならば、その横にClocking WizardというIPも漏れなくついてきてしまいました。こんな感じ。

前回、上記のIPのVerilogラッパを作製してシミュレーションしたところ、デフォルトでClocking Wizardは、実機上12MHzのクロック源に接続されているsys_clockから100MHzのクロックを生成しているらしいことを発見。

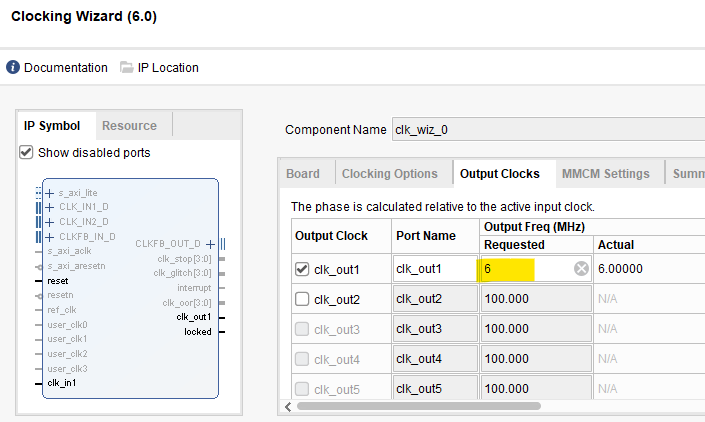

当方、手元のDigilent製Analog Discovery2(AD2)で観察を目論んでいるのですが、AD2のサンプリングクロックは100MHzです。上記の設定そのままだとバイナリカウンタの下のビットは観察できそうにありません。そこでFPGA実機に書きこむ前に動作周波数を落とすことにいたしました。こんな感じ。

前回設定は12MHzから100MHzを生成するという逓倍でしたが、今回のは6MHzに2分周で落とすと。これでどうよ。

上記のように設定を変更し、シンセサイズ、インプリメンテーション、ビットストリーム生成とノーエラーです。OKね。

FPGA実機で動作確認

久しぶりにCMOD-S7ボードを取り出し、FPGAにビットストリームを書き込みました。

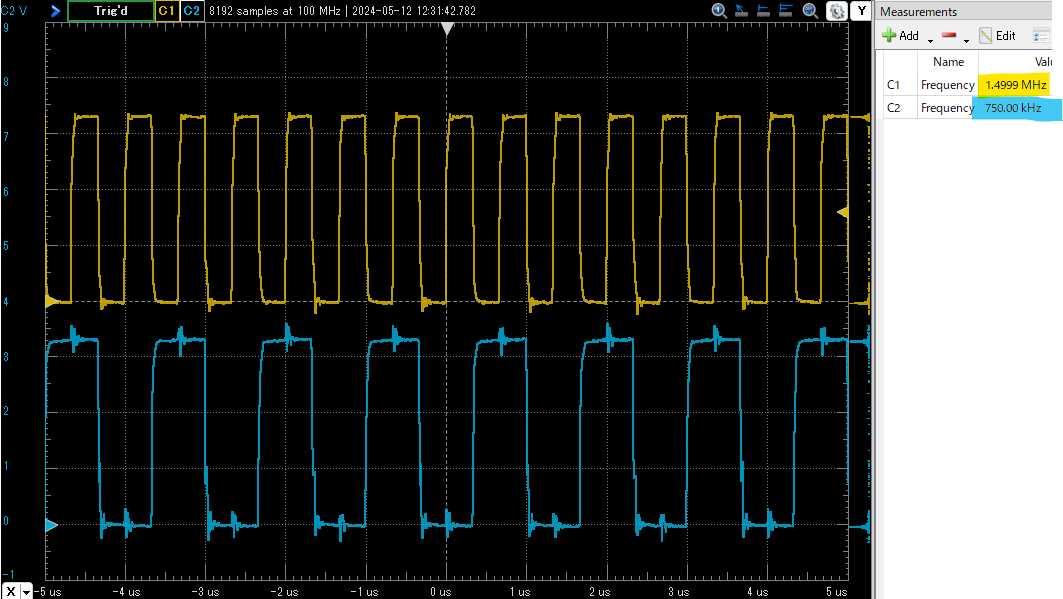

まずはバイナリカウンタのビット1とビット2の様子をオシロで見てみます(ビット0は離れたピンに割り当ててしまったので1と2です。)バイナリカウンタには6MHzが入力しているので、ビット0は3MHz、ビット1は1.5MHz、ビット2は750kHzが観察できる筈。どうよ。

黄色C1がビット1,青色C2がビット2です。約1.5MHzと750kHz、予定通りだね。

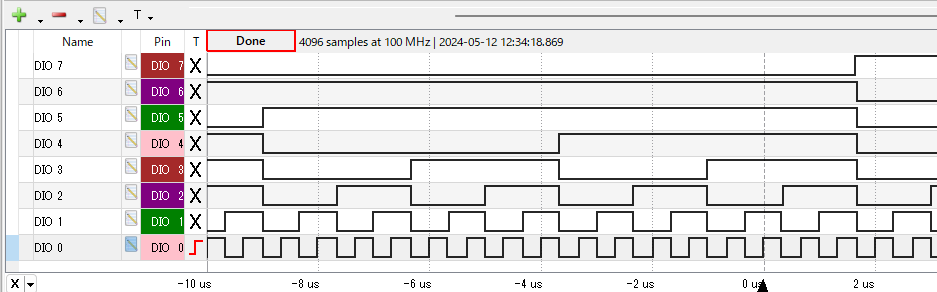

続いてロジアナモードに切り替えて、ビット1(以下図ではDIO0)からビット8(DIO7)までを観察してみました。こんな感じ。

バイナリカウンタしてますな。当たり前か。

一応、これでリハビリは完了。次回は何のIP?