前回、Vivadoに「バンドル」されているIPのリストを眺めることができたので、今回から「練習」していきたいと思います。「代表的なところ」からと思いつつ、何が「代表的」なのかサッパリなので目についたところからです。今回はその名もRAM-Based Shift Registerです。FIFOみたいなものかね。知らんけど。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい?Spartan-7搭載の超小型開発ボードです。

RAM-Based Shift Register

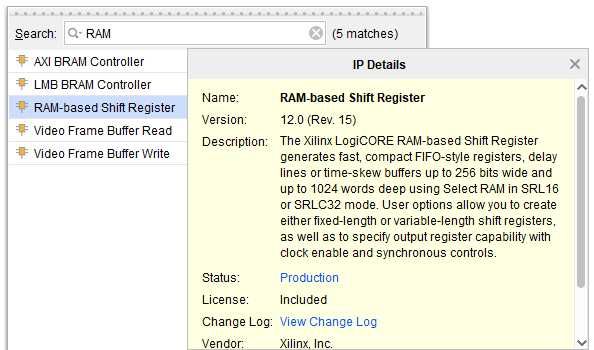

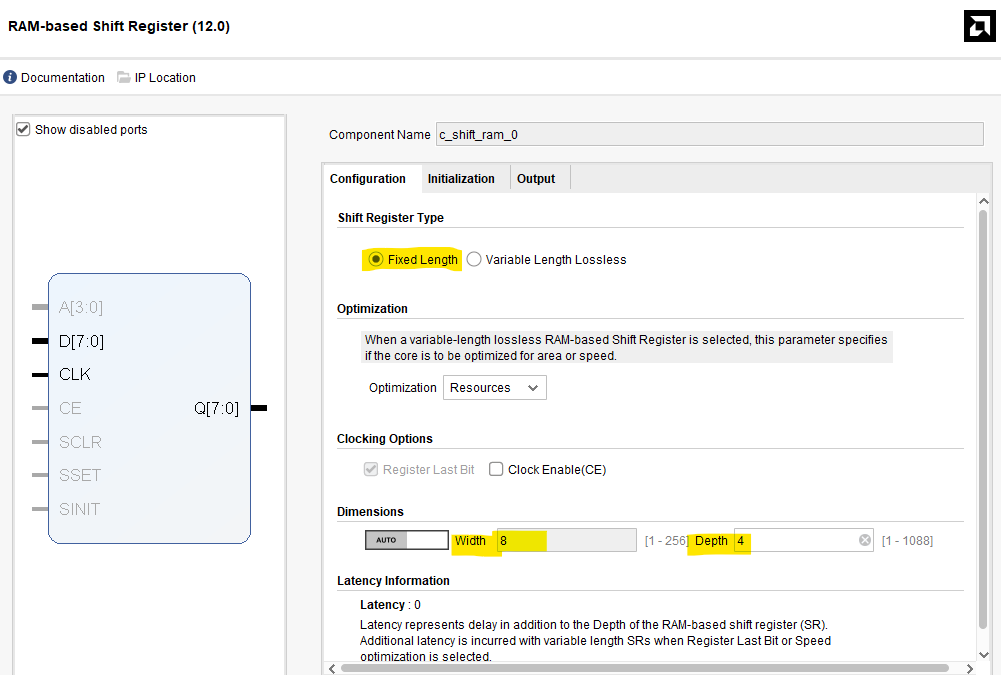

RAM-Basedとあるので、内蔵のBRAMを使っているのかと思えば、調べてみたらslice、LUTを使って「パラレルな」シフトレジスタを作り出してくれるものみたいです。ビット幅も深さもかなりデカいものまで設定可能です(当然LUTを食いつぶすケド。)今回はちんまりと8ビット幅で4段のFIFO構成で使ってみました。ビット幅がデカくて深いとシミュレーションがメンドーなので自主規制しただけです。IPの解説を表示しているところが以下に。

PlaseしたIPブロックを右クリックして以下のメニューから詳細なドキュメントを読むことも可能です。

IP Documentation > View Product Guide

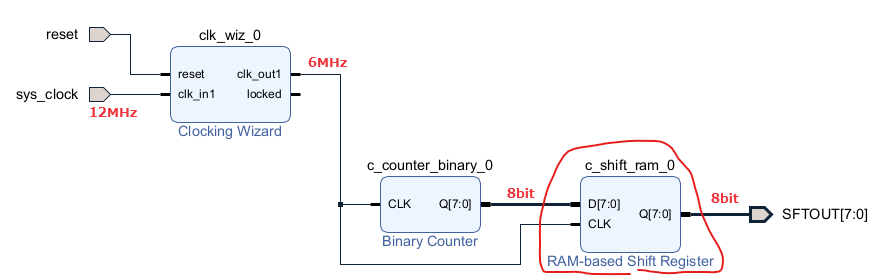

今回、練習に使った回路

左にある Clocking Wizardと、Binary Counterは以前の回で既に練習してみたものです。Cmod S7ボードにはオンボードで12MHzのクロック源が乗っているのでそれをsys_clockに使うつもりで接続してあります。そして後の回で実機上の出力を観察することを考慮して、2分周した6MHzクロックで動作させてみてます。遅ければ観察がお楽。お楽に流れる自分。

そして以前もつかったBinary Counterを今回は8ビット幅で使い、これを使って「FIFOに書き込むテストデータ列」を生成してます。さて、肝心のRAM-based Shift Registerの設定は以下のようにしました。

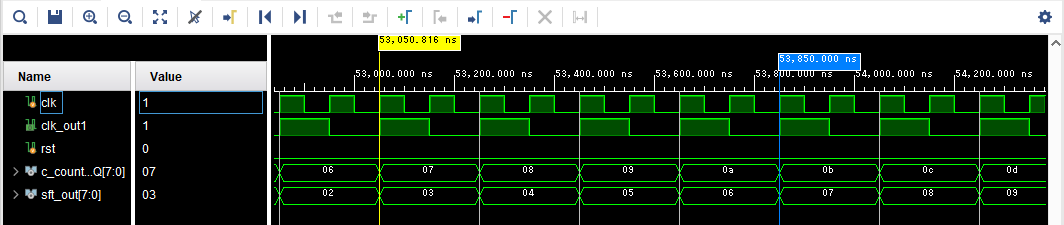

幅8ビット、深さ4段、固定長です。CLKの立ち上がりでDから8ビットの数を4個まで内部に記憶していき、その次のCLKからは「ところてん式」に先の方のデータから押し出されてでてくるハズ。いろいろオプショナルな制御もあるのですが、今回の構成が一番シンプルでないかと。なお、初期状態の「レジスタの」中身は今回設定ではゼロ詰めですが、ファイルから読み込むなどという技も使えるみたいです。

シミュレーション

上記のブロック・デザインから、Create HDL wrapperコマンドでブロック部分に被せるVerilogソースを作りました。これで他のVerilogファイルから「ブロック部分」を呼び出せるハズ。

今回はただピクピク動かしてみるだけ。以下の簡単なシミュレーションソースから、ラッパを呼び出すようにしてみました。

`timescale 1ns / 1ps

module sft_1_tb(

);

reg clk;

reg rst;

wire [7:0] sft_out;

sft_1_wrapper dut (

.SFTOUT(sft_out),

.reset(rst),

.sys_clock(clk)

);

always #50 clk = ~clk;

initial begin

clk = 0; rst = 1;

#200; rst = 0;

#200000; $finish;

end

endmodule

ぜんぜんCLKの速度の設定とかいい加減なんだけど。。。テキトー。

黄色のマーカのところでDに入力した0x07が、内部クロック(2分周)の4つ後のところ、青色のマーカのところでSFTOUTに出てきてます。予定通りの動作じゃね。