前回、RISC-V(MicroBlaze V MCS)の最小システム?を構成、Vivado上でのハード生成はOK。ソフトウエア開発環境であるVitisへ「輸出」も成功。しかしここまで。Vitisの使い方がそもそも分かっておらんことが発覚。ここで立ち往生とな。今回は心を入れ替えてVitisの使い方から学ぶっと。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

前回のまとめ

前回はVivado 2024.1から公式サポートになったAMD(Xilinx)のRISC-Vソフトコア(MicroBlaze V)のマイクロコントローラ構成のIPをVivado上に配置、手足をCmod S7ボードの端子に合わせて接続してみました。シンセシス、インプリメンテーション、ビットストリームまで生成OK。早速 XSAファイルを作製してソフトウエア開発環境?である、Vitisに輸出、読み込みして何やら分からんプラットフォーム化にも成功したみたいです。

しかし、あきまへん。ある筈のドキュメントPG-440が不在。「読んどけ」とご指示のあったドキュメントがないとFPGA素人老人は途方にくれたところで終わってました。

さて今回は、気をとりなおしてVitisの使い方から勉強(それにしては大急ぎすぎる気もするが)、RISC-V上のソフトウエアのビルドに向けて再挑戦っと。

Vitisのチュートリアル

文書充実のXilinx様なので当然チュートリアルは存在します。調べたところでは、2024年版の最新のやつはまだ日本語には対応してません。現状日本語対応している最新は以下のバージョンみたいです。

2023.2

内容的には同じものみたいですが、フォーマットの異なる2つの文書が存在してます。以下は amd.comドメイン内の「公式」文書だと思います。

こちらは英文版の最新版も含め、各種バージョンを選択可能なもの。「いつもの」形式です。

一方以下は、github.io側に設置された日本語ドキュメントのURLです。

ざっとみたところ同一の内容っぽいですが、フォーマットが異なります。

素人には「込み入った」文書だよ(個人の感想です)

FPGA素人のお惚け老人には、チュートリアルとは言え込み入った文書です。勝手ながら込み入る理由を考えると

-

- 複数の目的と複数の環境が併記されている

ことが大きいです。今回、お惚け老人はミニマムの「コア一つ、OSなど無しでFPGAに書き込んだRISC-V上でLチカのコードが走ったら嬉しい」ということで取り組んでおりますが、Vitisがカバーしている範囲は広くて深いです。

-

- データセンタのマシンに組み込まれるFPGAアクセラレータからお惚け老人のようなケースまでハードのレベルは段違い

- FPGAハード内のメモリで走る「ソフト」も、FPGAを接続したホスト上で走る「ソフト」もあり

- FPGAハード内のメモリで走る「ソフト」といっても、LinuxなどのOSありのレベルから、お惚け老人のような standaloneもあり。あるいはAIなど使う奴らもあり、落差が大きい。

- 開発のビルドマシンOSと運用のホストOSが異なることもありえる

- FPGA上で実際に実行されるオブジェクトと、開発機上でエミュレーション(CPUはx86系)される場合もある

- Vitisの名をいただくツールには、ソフトウエアだけでなくハードウエアの高位合成設計に使えるもの(Vitis HLS)もある。

そしてさらにいうと、現在はVitis Classicと呼ばれている、古いEclipseベース?のツールから、Vitis Unified IDE(Visual Studio Codeベース?)の新しい環境への端境期?で、環境の移行とか、どちらかの環境に依存する記述とかも混在しているので、忘却力の老人はついていくのが辛い。。。

さらに言うと環境の変更に伴って、

従来「ホストアプリケーション」と呼んでいた用語が「アプリケーションコンポーネント」に変わった

とか用語の改定まであります。コレハトテモツライ。

気を取り直して「アプリのビルド」に挑む

前回は、main.c にあたる部分、どこにどうやって書いたらよいの?というところで途方に暮れて終わってました。しかし、Vitisには充実のExampleがあります。まずは真似っこから始めるっと。

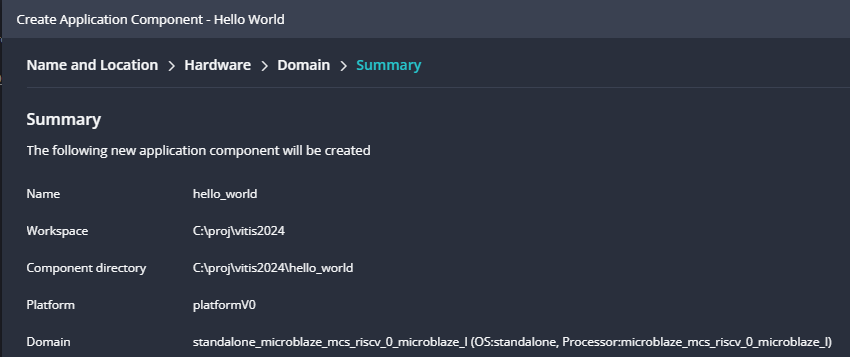

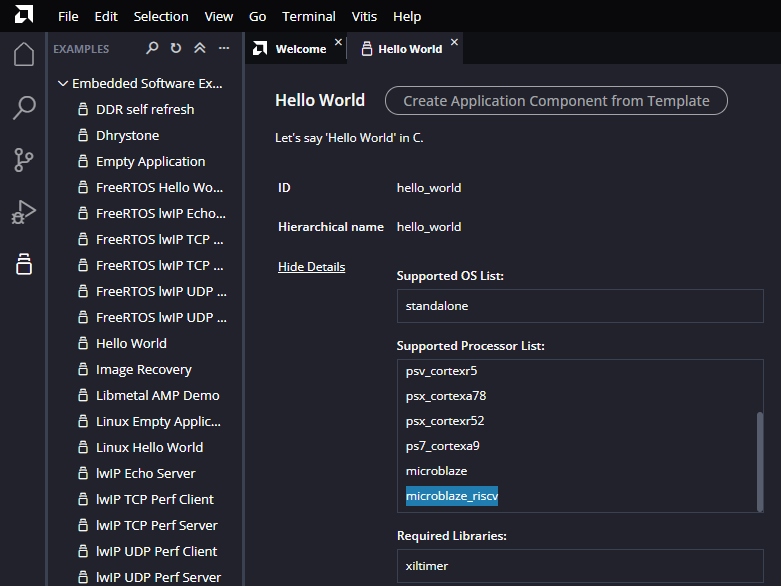

Exampleを開いてみると Hello Worldがありました。それをクリクリすると上記のようにメニューがでて、standaloneでmicroblase_riscvも選択可能でした。これを使えば、前回引っかかったところが乗り越えられるんじゃ。

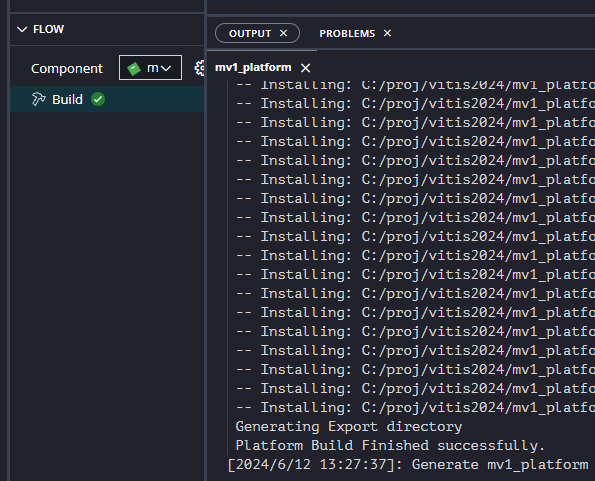

ただしやってみて判明したのは、既に「プラットフォーム」が準備済の時にHello Worldのような「アプリケーション」を構成できるということです。前回はVitisにハード情報を読み込んだだけで、そのハードの上でのライブラリのようなものはビルドしてません。プラットフォーム側で先にそいつをビルド。

なあんだ、やれば出来るじゃん。Vivadoから XSAファイルを輸入したら、プラットフォームのビルドをしておくのが良かったのね。同じXSAを参照し、前回と今回と2つ同等なプラットフォームを作ってしまったな。

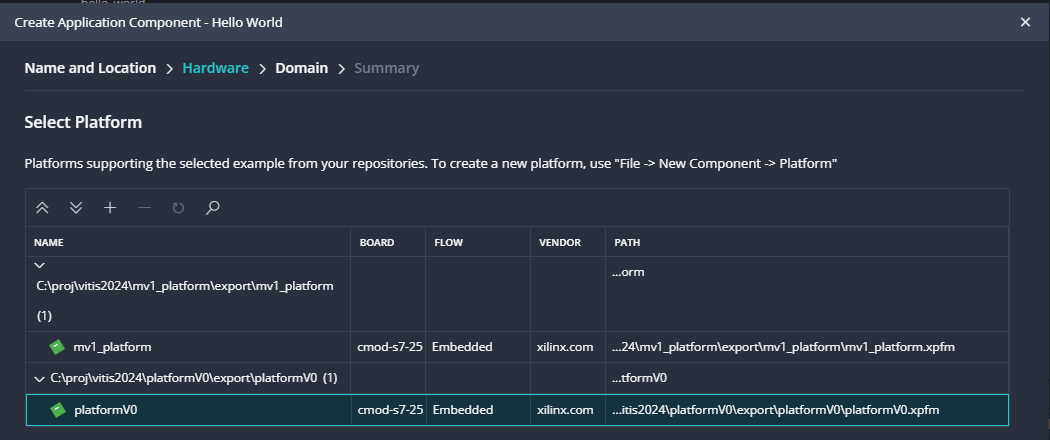

さてExampleに戻ってHello worldして~ということでボタンを押すと以下のように「プラットフォーム」を聞かれます。待ってたよ、今回は準備済。

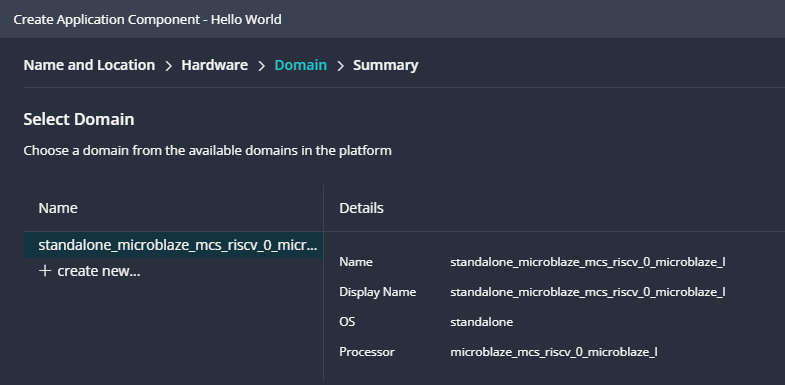

今回新たに追加した方を指定。するとお次は「ドメイン」聞かれます。もし、RISC-Vとそれ以外のコアとか登載していたらドメインは複数ってことみたい。でも今回は一つだけなので一択。

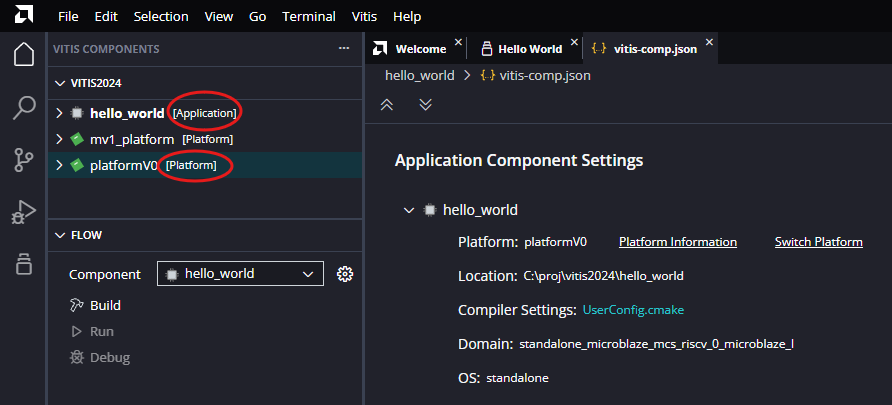

その結果生成された Hello Worldのプロジェクトが以下に。

赤丸しておきましたが、Hello WorldはApplicationで、輸入したXSAから生成した方はPlatformです。この辺の区別も分からんまま、前回は突っ込んでました。途方に暮れて当たり前か。

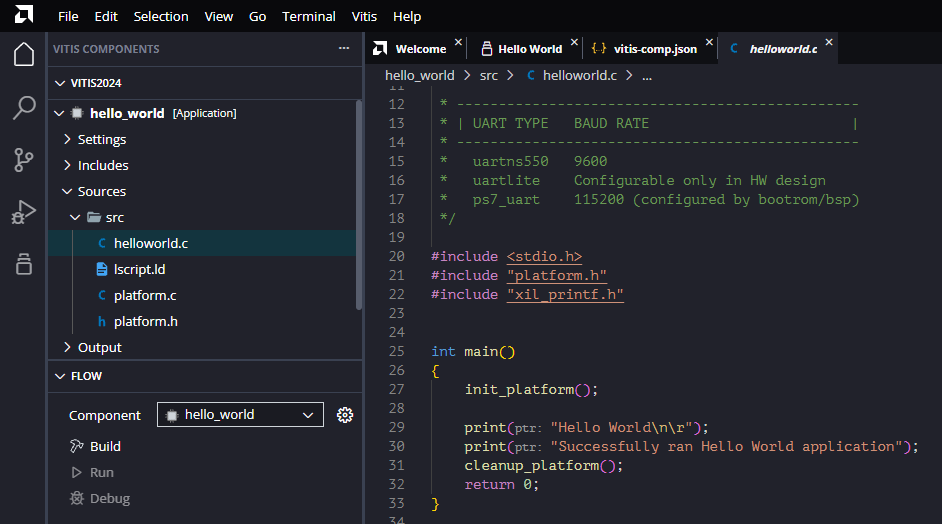

さて、Hello worldプロジェクトを開けば、慣れ親しんだCのソースが存在しておりますぞ。

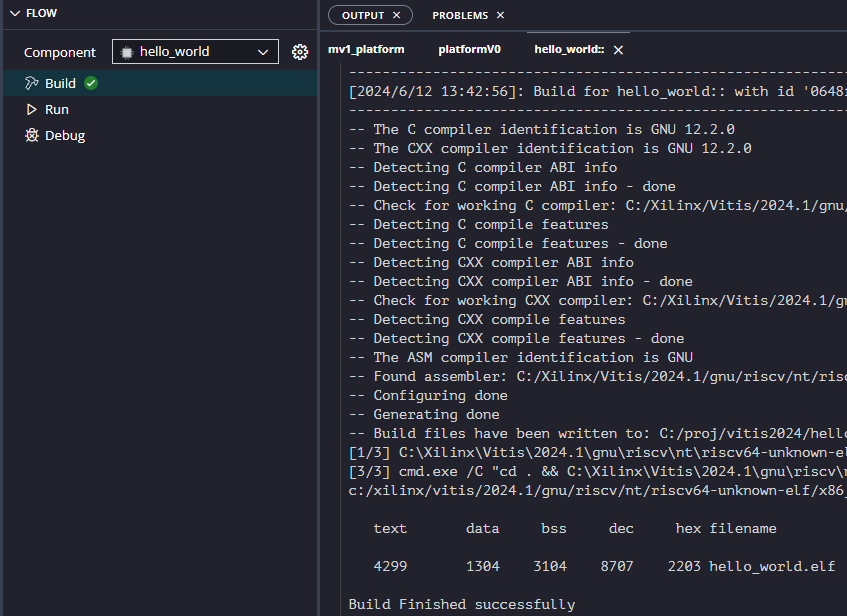

Build Finished successfully とな。やったね。ちゃんとRISC-Vのコンパイラが起動されて走っているみたい。elfどころか、ビットストリーム・ファイルまで出来てますがな。

やったね、調子に乗ってCmod-S7ボードを接続してビットストリームの書き込みを試みましたが、これはダメでした。ボードの認識でトラぶっている?まだまだだな。