前回、チップ上のRAMにビルドしたオブジェクトがロードできんのが問題ということを理解。IP内部にメモリを含んでいるMCSではなく、単体CPUのIP+単体メモリIPであれば動作するだろうと。なんたって以前に動作OKになっているし。そこでRISC-V単体コアIPでやってみました。ようやくHello World成功。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

どうもMCSのメモリへのロードで失敗している

Vitis IDEからの生成したオブジェクトのロード失敗は、マイクロコントローラ構成のMCSのメモリへのロードに何か問題がありそう、ということにようやく気付きました。長かったな。そこで、以下の設定で再挑戦することに。

-

- MicroBlaze-V 単体IPに、単体ローカルメモリを接続してシステムを構成する

- ハードウエアは上記を中心にUARTとLEDへの出力ポートのみ接続したもの

- Vitisでオブジェクトを生成するソフトはとりあえず伝統の「Hello World」(USB UARTへ出力)

ぶちゃけ、第46回から第48回で、フツーのMicroBlazeコアでの実習のサブセット版という感じです。コマケー話は上記の回に書いたので、以下は結論部分。

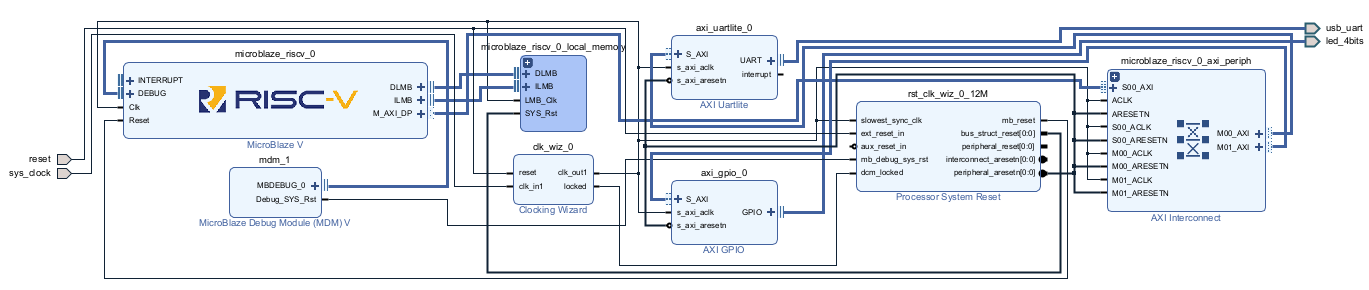

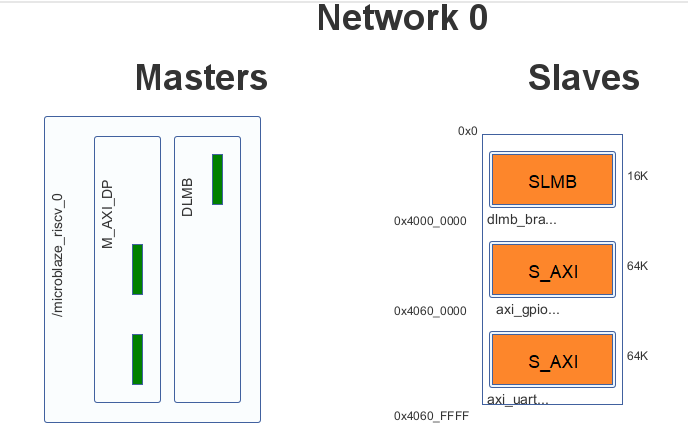

作製したブロックダイアグラム

単体RISC-Vコアを中心に作成したブロックダイアグラムが以下に。

左上に燦然と輝くRISC-Vマークが単体のコアです。その横の「濃い」色のブロックがローカルメモリです。ここにVitisでビルドしたオブジェクトファイルをロードできれば事はなった、と。ホントか?

なお、上記には沢山のブロックが並んでますが、例によって「オート・コネクション」機能を駆使?すると、Vivadoがよきに計らってくれた結果です。お惚け老人はほとんど何も考えてません。

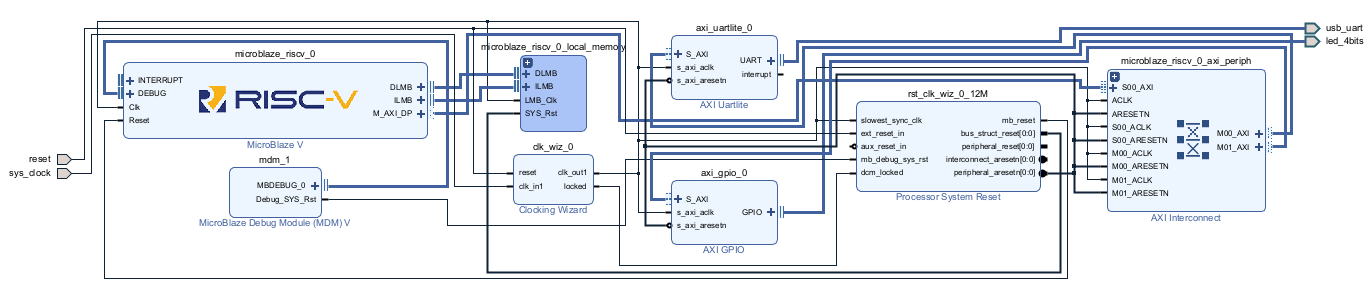

さて肝心のローカルメモリのメモリマップを覗いてみるとこんな感じ。

右上の、SLMB、16Kバイトのところにオブジェクト・プログラムを配置したいのよ。

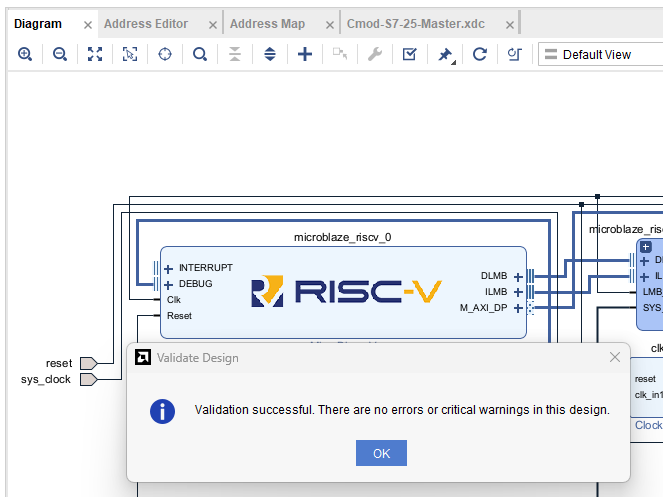

バリデーションOKそしてビットストリーム作成など

上記のブロックダイアグラムがバリデーションOKになったところが以下に。

まあ、自動接続に頼っているから、OKにならんハズが無いのだけれども。

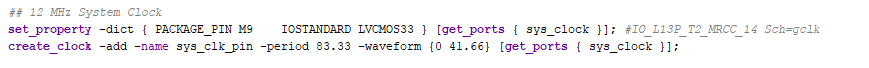

なお、sys_clockだけは、制約ファイルの方で端子を定義しています。以下のところね。

また、sys_clock=RISC-Vなどに与えるClkと一致させたので12MHz動作です。何も言わずにVivadoに任せきると、逓倍して100MHzクロックを配ろうとするので、今回はその部分は「押しとどめて」ます。ともかくHello Worldしてくれれば御の字。

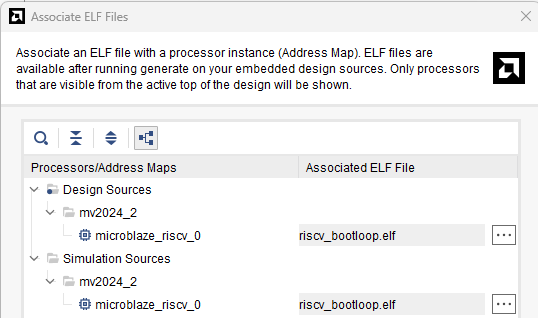

シンセシス、インプリメンテーション、AssociateELFしてビットストリーム作成、そしてXSAファイルのExportと一気です。

なお、AssociateELFのところで気づいたのだけれども、ここでブート時の無限ループなオブジェクトに「仮に紐づけ」しているみたい。

Vitis2024.1でGo

過去回でMicroBlazeしたときには、Vitis 2023のClassic使ったのですが、試行錯誤のお陰で、Vitis2024.1でもいける気がしてきました。

-

- VivadoからExportしたXSAファイル(ビットストリーム入り)を指定して「プラットフォーム」プロジェクトを作ってビルド

- 上で作ったプラットフォームの上で動作するアプリケーションプロジェクトを作ってビルド。今回のアプリケーションはHello Worldのサンプルプロジェクトとする。

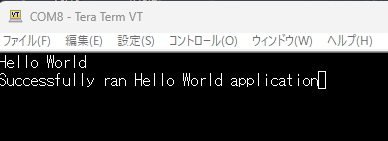

この辺なんども繰り返してきたので慣れました。出来たところでボードへ書き込み。仮想端末ソフト(伝統のTeraterm Pro)をUSBシリアルに接続してみます。

おお、ここまで長い道のりだったな。。。おっちょこちょいなだけか?