前回は、FPGA上のRISC-Vコアで走るソフトウエアでHello Worldできました。ようやくだったな。となれば今回はハードウエアでは吉例な「Lチカ」です。FPGAに書き込むビットストリームにはGPIOを搭載済です。Vitis IDEでHello Worldソースをチョイ直したらLチカできるハズ。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

GPIO制御の実体

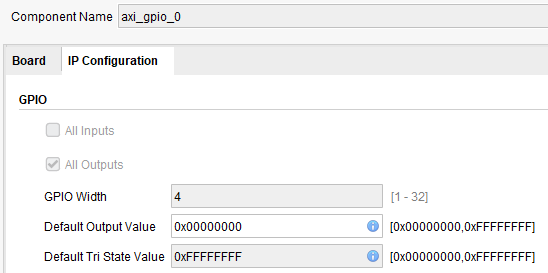

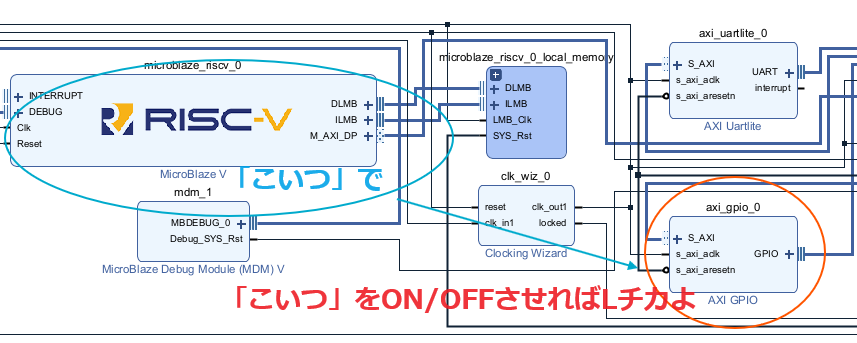

GPIO制御の実体は、前回ハードを組み立てたときにこっそり忍び込ませてあったAXI_GPIOというお名前のIPブロックです。左上の青丸のRISC-Vコアがソフトを実行し、バスを通じて右下のaxi_gpio_0を制御できれば出力端子はボード上のLED端子に接続してあるので、Lチカできるハズです。

LEDは4個あり、その4個に上記IPの出力のビット0から3が接続されている筈。

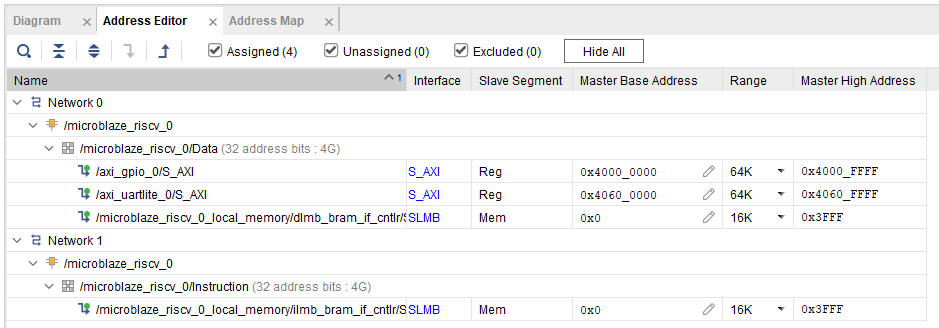

なお、RISC-Vコアからみたaxi_gpio_0のレジスタのアドレスは以下に見えるハズ キリもよい 0x4000_0000番地ですじゃ。

キリもよい 0x4000_0000番地ですじゃ。

Vitis2024.1、GPIO制御コードを追加

さて、上記のハード設定を行ったXSAファイルでVitis上でプラットフォームを作製してビルドまで実施済です。よってLチカを実施するために必要なのは、アプリケーション側のソースに手を入れてビルドしなおすだけであります。

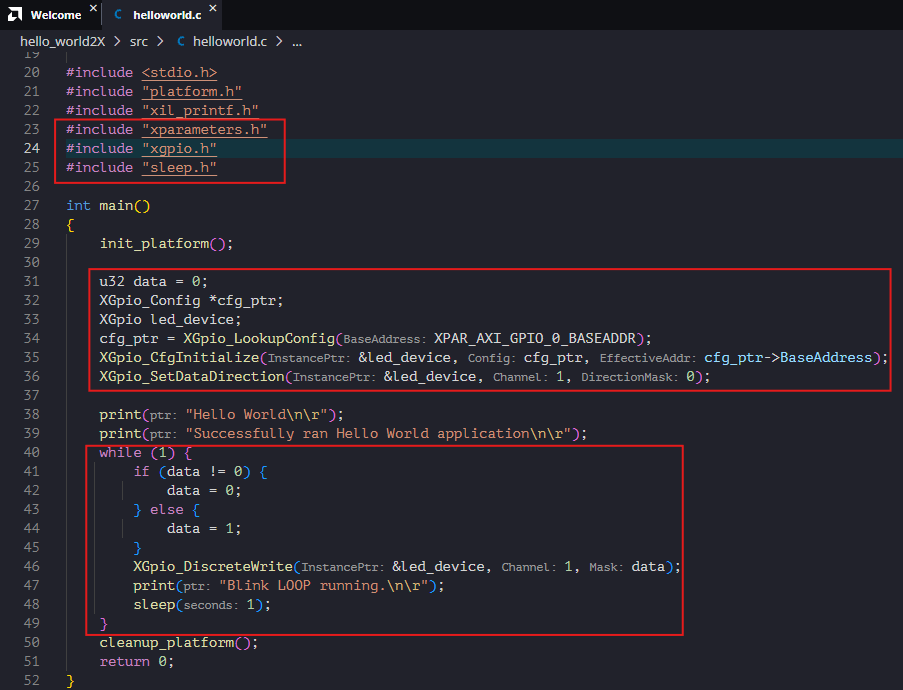

プラットフォーム側は既にできており、includeディレクトリを見ればヘッダファイルなども並んでます。この中にGPIO制御に必要なものを選んで並べていけばLチカできるハズ。Hello Worldのソースに対して、Lチカ用に書き加えた部分を赤四角で囲いましてございまする。

上の四角内でGPIOと「待ち」に使うヘッダをインクルードしておいて、真ん中四角内でGPIOとそれを制御するための変数を初期化。そして下の四角内でLチカの無限ループであります。1秒おきにビット0のLEDを点滅させるとともに、USB UARTの接続先の仮想端末にもメッセージを送り続けます。

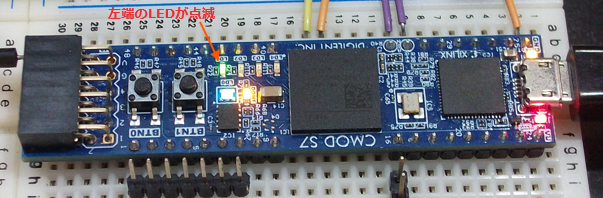

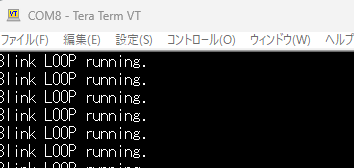

実際にRUNさせて、メッセージが表示されている様子が以下に。

これでRISC-Vコアを使役して、いろいろFPGAのIP動かしてみるのは思いのまま。ホントか?