前回、Vitis IDEから「ソフトウエア・デバッガ」を使いました。使いやすいじゃん。しかし「プラットフォーム」のRISC-V(MicroBlaze-V)コアの設定がデバッガのことを無視した設定になっていたので、デバッガの機能を十分に引き出すことができませんでした。そこでハードを作り直しね。こういうときFPGAはお楽。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

今回の修正方針

今後、RISC-Vコアに加えてVivado内蔵のIPや、自前のVerilogコードなどを「練習」するときにも使えるように以下のような方針としました。

-

- Vitisでソフトウエア開発したときに、Vitisのデバッガの諸機能を使えるようにしておく(当然デバッグハードウエアは増加)

- しかし後から加えるIPや自前のVerilog回路分のリソースの領域をなるべく残すためにRISC-Vコアは面積優先して小さく作る

- オンボードのLEDはハードウエアでも使いたいので、RISC-Vコアがソフトで制御できるのは1灯のカラーLEDのみとし、単色4灯のLEDはハードウエア側に割り当てる

- 上記の単色LEDのうち1灯をハードウエアの「ハートビート」信号に割り当て、CPUコアがどうであれ、ハードが生きていれば点滅するようにハードウエアで制御する。

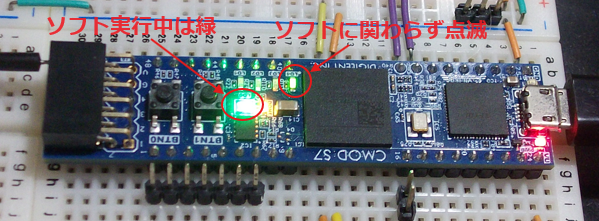

- CPU側で制御するカラーLEDは、ソフト実行中は緑、終了したら赤のようにソフトウエアの実行状況を観察できるようにする。

- USB-UARTおよびAXI-TIMERは搭載。printfでホスト端末に報告可能。タイマにより実行時間の計測可能。

MicroBlaze Vのコンフィグ

問題のDebug設定は前回にくらべると大幅拡充。それでも最低線だが、0よりはマシ?

そして肝心のローカルメモリは64KB。前回につづき、キャッシュレス。

ラッパのソースも改造

上記のブロックダイアグラムに「被せる」ラッパのソースは、前回までは「Vivadoに管理お任せ」でしたが、今回は「自分で手を入れる(自分で管理するぞよ)」に設定変更。そこで以下のように手を入れてます。led3という端子は、オンボードの単色LEDの写真右端のLEDに接続されるように指定してあります。

25ビットのカウンタで、12MHzのsys_clockをカウントして点滅させているので、速すぎず、また遅すぎずの「良い感じ」でLチカしてくれるハズ。

VitisでDhrystoneプロジェクト使って動作確認

勝手にDhrystoneのソースに書き加えたコードが以下に。GPIOの初期化とそれを使ったカラーLEDの色変制御。

#include "xparameters.h"

#include "xgpio.h"

//~中略~

XGpio_Config *cfg_ptr;

XGpio led_device;

cfg_ptr = XGpio_LookupConfig(XPAR_AXI_GPIO_0_BASEADDR);

XGpio_CfgInitialize(&led_device, cfg_ptr, cfg_ptr->BaseAddress);

XGpio_SetDataDirection(&led_device, 1, 0);

XGpio_DiscreteWrite(&led_device, 1, 7); //消灯

//~中略~

XGpio_DiscreteWrite(&led_device, 1, 5); //緑点灯

start_time();

//~中略~

XGpio_DiscreteWrite(&led_device, 1, 3); //赤点灯

現物写真が以下に。まずはDhrystone実行中。

そして測定終了したところ。

そして測定終了したところ。

なお、今回修正でデバッガからブレークポイントだけでなくウオッチポイントも使用可能となりました。

ただね、プロファイラの「起動」はできるようになったのだけれど、使い方が分かりませぬ。これはまた「そのうちの」宿題ぞなもし。