「アナデバ社(ADI社)のWeb記事『StudentZone』を初回からすべて読む」の2022年12月号の実習2回目です。前回不足していた部品もそろったのでPLL(Phase Locked Loop)動作を実習して行きたいと思います。といって今回のは前回でもやればできた部分なのだけれども。まあお楽が一番てか。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

アナデバ様のStudentZone 2022年12月号記事(日本語版)へのリンクは以下です。

アナデバ製ADALP2000学習用部品キット所蔵のVFC(Voltage-to-Frequency Converter、電圧周波数変換器)-IC、AD654 をVCO(Voltage Controlled Oscillator、電圧制御発振器)として使ってPLLを構成する回です。

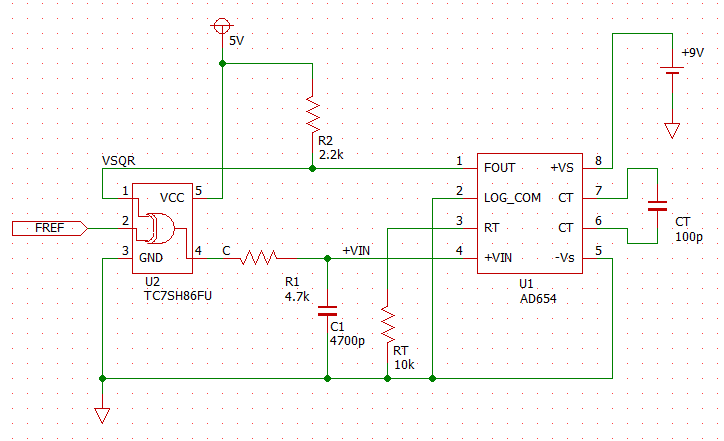

今回実験の回路

手元に分周器につかえる手ごろなカウンタICの在庫がなかったので発注、その際、東芝ワンゲートロジックの排他的論理和IC、TC7SH86FUも密に購入しておりました。TC7SH86FUのSIP化についてはこちら。アナデバ様の記事では、PLLの位相検出器として、「万能のCMOSデバイス」CD4007とディスクリートのMOSFET2個を使って排他的論理和を構成することになっとります。確かにCD4007は何にでもなる偉大な石ですが、XOR1個に配線面倒すぎるでないかい。ということでTC7SH86FUにお出ましいただいたです。ワンパッケージに1ゲートしか入っていない「ワンゲートロジック」です。今回これを位相比較器として使ってPLL回路を組み立てました。こんな感じ。

分周器はどうしたんだ?といって、そいつはまた次回っと。今回は1:1のガチの周波数でフェーズロックを掛けてみるの回であります。

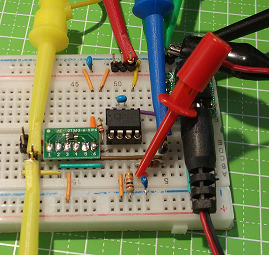

ブレッドボード上に組み立てた現物が以下に。ほぼ中央の8ピンDIPがAD654、そして左側のSIP化ボードに載っている小さいパッケージがTC7SH86FUです。

実験結果

前回の実験から、上記のブレッドボード上に組み立てたAD654の場合、2.5Vの入力を与えると230kHzで発振することが分かってます。

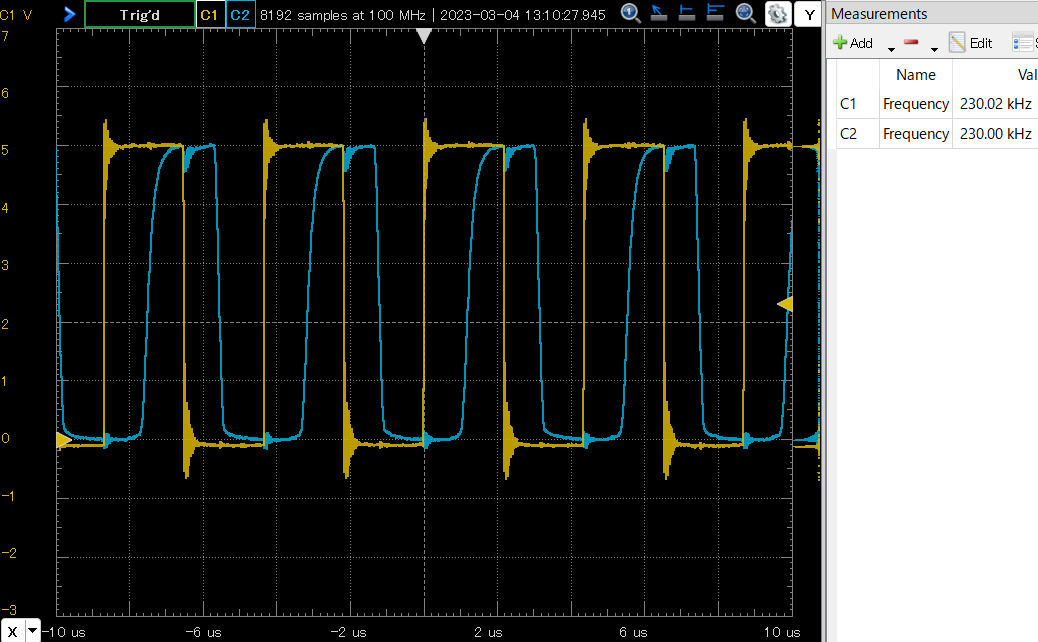

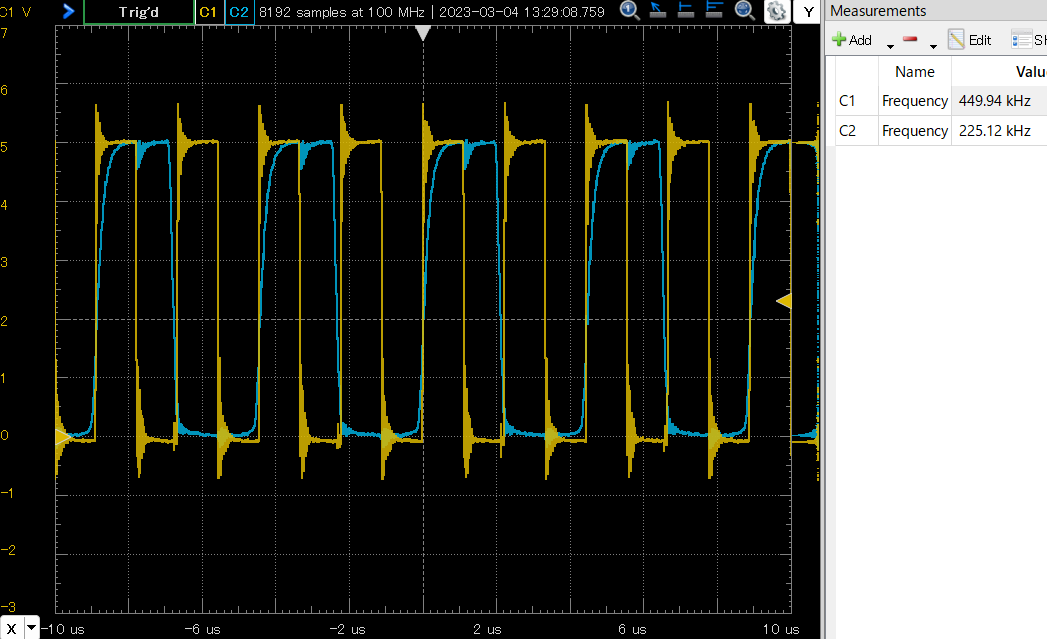

そこで、今回はFREF波形に230kHzの矩形波(オフセット2.5V、振幅2.5V)を与えて、PLLが「ロック」していることをまず確認いたしました。波形が以下に。黄色C1がAWGで与えているFREF波形です。青色C2が回路図のVSQR点で観察したPLL出力。ほぼほぼデューティ50%点でロックしておる感じです。

このときの+VIN点(LPFの出力点、AD654への入力電圧)のDC電圧が以下に。2.485Vとな。予定の2.5Vとほぼほぼ一致。

さて、このロックされている状態から上下どのくらいの周波数までPLL動作が可能なのかFREF周波数を変化させてみていきます。

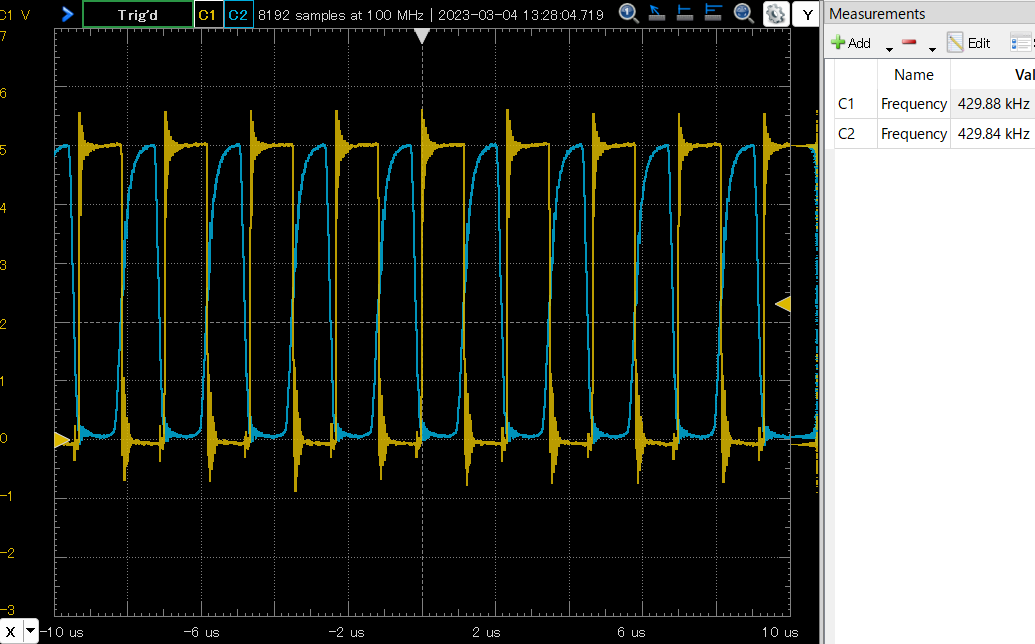

やってみると明らかなのは、周波数を大きく変化させちゃうとロックが外れてしまう、ということであります。230kHzから突然300kHzとかに上げてしまうとロック外れてしまいました。ゆっくり(20kHzステップくらい)徐々に上げていくと300kHzどころかもっと上までロック可能でした。以下を御覧じろ。

上記の430kHzでもロックかかっています。そのときの+Vin点の電圧は4.7V付近です。上記の波形をみると黄色と青がほぼほぼ逆相でもはや「オーバラップの余地」も無さそう。5V電源で動作させているので入力電圧自体もほぼ限界に見えます。ということはこれ以上の周波数調整は無理?

ここより周波数を上げると突然ロックが外れ、+Vin点の電圧が2.5V付近まで一気に落ちます。こんな感じ。

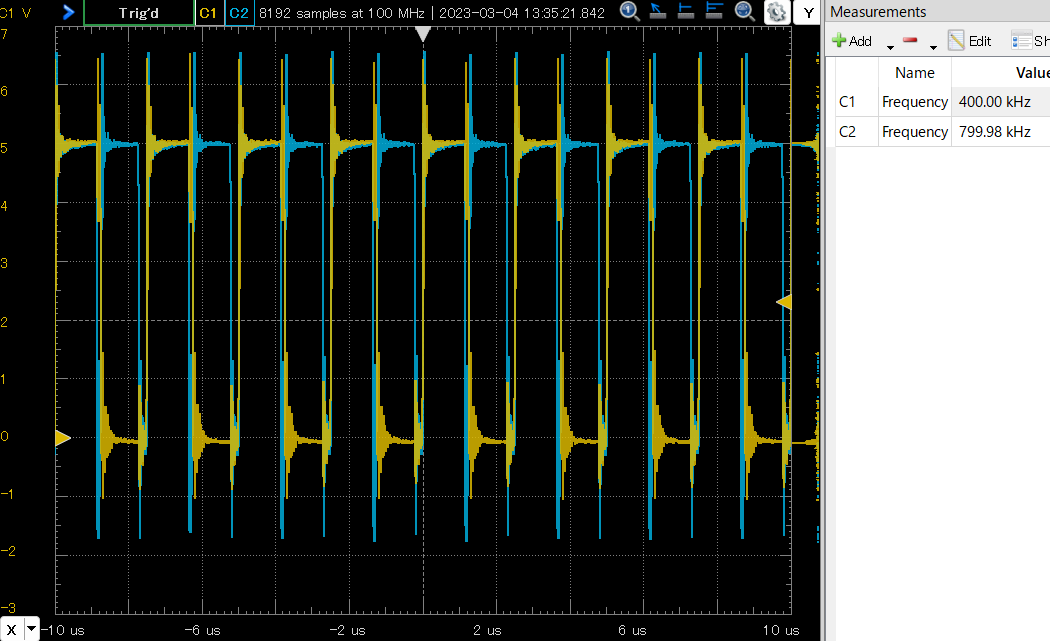

なお、XOR出力のC点の波形も観察せよとあるので、青のC2でC点を見たところが以下に。このときの入力周波数は400kHzでした。かなり限界に近いけれど、C点はXOR出力なので入力波形の2倍の周波数が見えてます。片方はFREFの黄色に隠れてほとんどわからんですけれども。

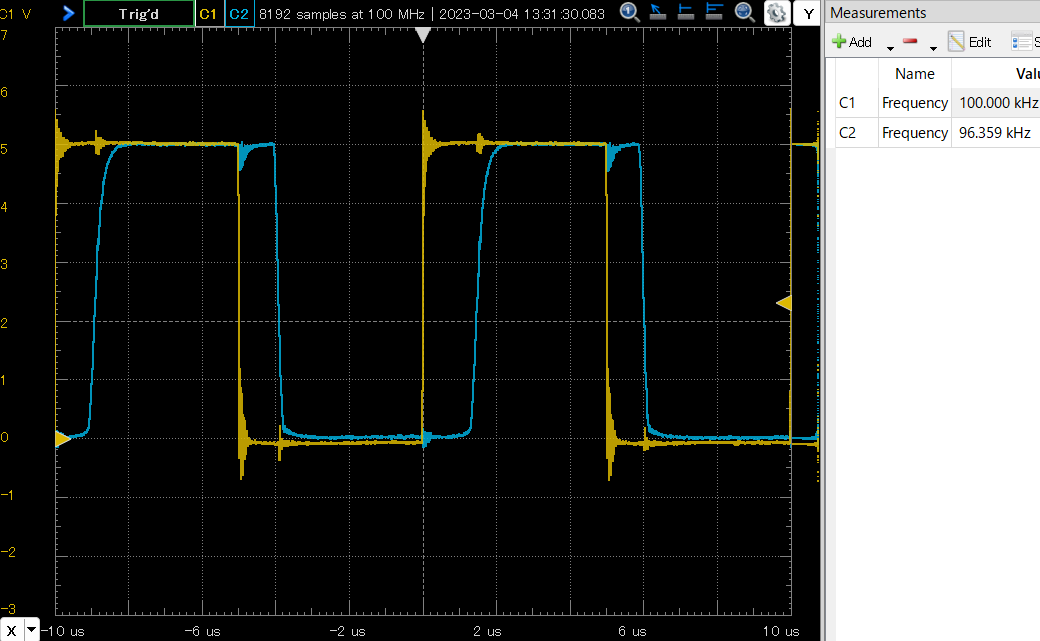

低い方も徐々に落としていくと100kHzくらいまではロックがかかりました。以下は100kHzの場合です。

このときの+Vin点の電圧1.1V。こちらも限界か。これ以下になると出力波形が不安定になっていき、ロックが外れます。

PLLのロックするあたりは分かった。ホントか?次は分周器を突っ込んで逓倍だな。大丈夫か?