「アナデバ社(ADI社)のWeb記事『StudentZone』を初回からすべて読む」の2022年12月号の実習3回目です。前回PLL回路が動作しました。今回は、分周器を挿入して16逓倍のPLLとしてみます。本当は4逓倍か8逓倍くらいが良かったのですが、購入した部品の都合で16逓倍とな。よく考えて部品買えよな、自分。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

アナデバ様のStudentZone 2022年12月号記事(日本語版)へのリンクは以下です。

また、今回は巻末問題への解答編もあります。

December 2022 StudentZone Quiz Solution

16逓倍PLL

前回は、外部から与えるリファレンス周波数とPLL内部のVCOで生成する周波数の周波数比が 1:1 のPLL動作を確かめてみました。このVCOで生成する周波数を分周してからリファレンス周波数と比較するようにすれば、リファレンス周波数の分周倍の周波数がVCOで生成されることになります。

今回、分周器として購入したのは以下の別シリーズ記事にて動作確認した東芝製TC74HC4020APです。4000シリーズのピン配(機能)で、74HCシリーズの特性ってか。

部品屋根性(86) TC74HC4020AP、14Stage binary counter

でもね、今回のPLL回路に使うには、4020でなく「兄弟チップ」の4040の方が良かったかもです。今頃反省しても遅いけど。4020は16ピンパッケージに14段の分周器を詰め込んでいるので、分周器の下の方の2ビットは当然存在するのですが、出力ピンがありません。つまり、2分周の後、4,8分周の出力を飛ばして16分周出力です。今回、2逓倍ではちょっと物足らないし、16逓倍はやりすぎな気がしないでもないです。ホントは4逓倍か、8逓倍くらいが良かった。4040であれば分周器は12段だけれども全ビット出力があるので4分周、8分周もとりだせたのです。トホホ。

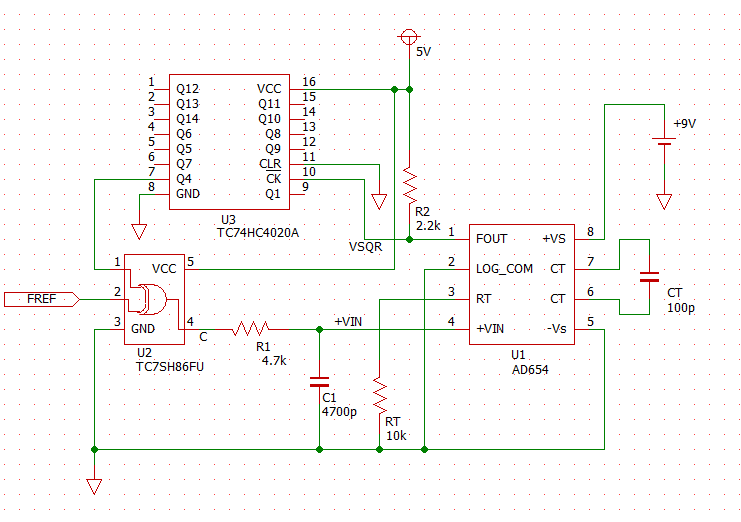

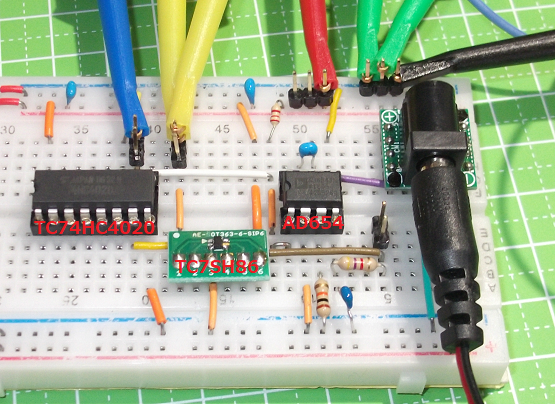

ブレッドボード上に組み立てた実機は以下のようです。以下の3チップでPLLループとな。

-

- AD654、VFC(VCO

- TC74HC4020、分周器

- TC7SH86、XOR(位相比較器)

右にある電源ソケットは006P電池から+9Vを供給するためのものです。お手軽ツール(当方ではDigilent Analog Discovery 2使用、アナデバ様の思し召しはアナデバ製ADALM2000だけれども)は±5Vまでの任意電圧を供給できるのですが、5Vは超えられないのでその対処っす。

動作結果

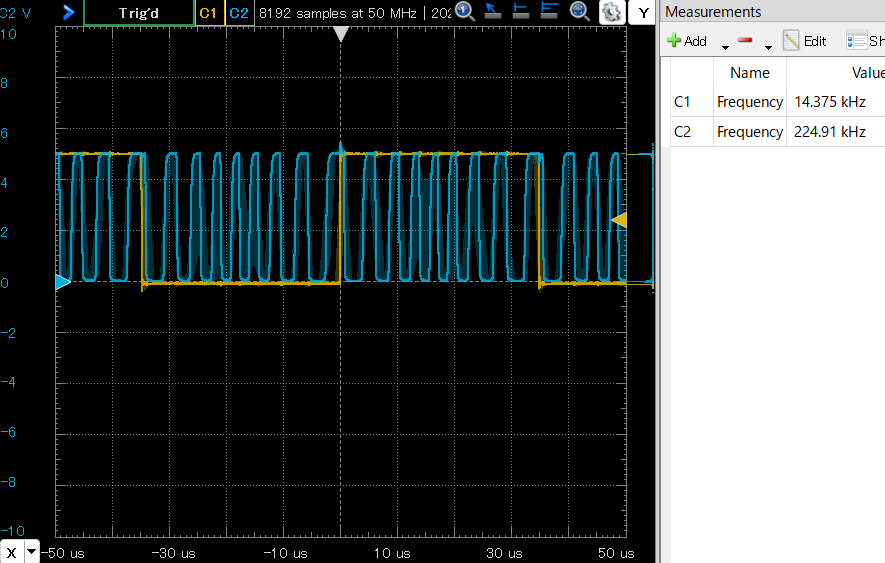

上記回路の動作結果の波形が以下に。黄色のC1が、FREF端子に与えた14.375kHzの矩形波です。これがリファレンス周波数。それに対して青色C2が、VSQR点の分周前のVCO出力波形です。

上記のMeasurementsでは、微妙にVCO出力の波形の「伸びチジミ」があるのでピタリの計測数字になっていませんが、

14.375kHz * 16 = 230kHz

です。上記の波形そのものは極めて安定している感じがします。も少し本格的なPLLもやってみたいですが。