前回に続きいよいよ制約 constraints の設定の練習に入りたいと思います。ついては何かチュートリアルなどないのか?AMD(Xilinx)様に無いわけないっと。「UG945 – Vivado Design Suite チュートリアル: 制約の使用」です。英語読む気力が薄れたお惚け老人にも優しい日本語版であります。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社(Xilinx) Vivado 2023.2 を使用させていただいております。

UG945チュートリアル

前回「TCLを制するものが制約を制す」などと分かったようなことを書きました。制約ファイルの実体がTCLコマンドを並べたファイルだからです。しかし、テキストエディタでTCLコマンドをチマチマ書いていくのかと思えばさにあらず。GUIをクリクリやっていけば設定が出来てしまいます。ほとんどのことはGUIで出来てしまうみたい。誰が言った?「TCLを制するものが制約を制す」などと、自分か?

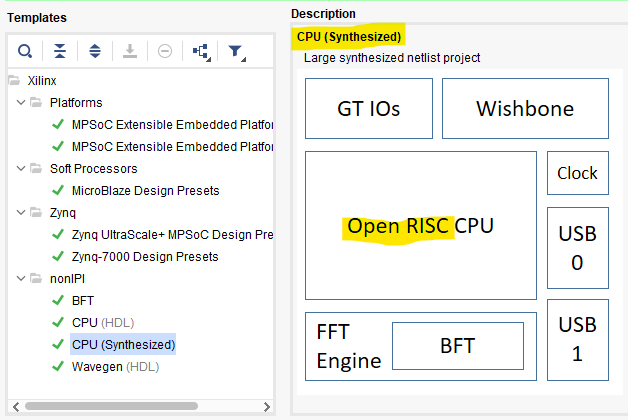

さてチュートリアルではサンプル・プロジェクトを使って制約ファイルをあらたに定義する演習をやってます。そこで使われるサンプル・プロジェクトは以下の過去回でちょっと「動かしてみた」ものです。

帰らざるMOS回路(55) Xilinx Vivado、Example Project

上記の中の CPU(Synthesized) というサンプルプロジェクトです。OpenRISC(OP1200)使用のExampleプロジェクトで、既にシンセサイズ済のOP1200などのIPコアをネットリストで読み込んで使用するものです。選択画面が以下に。

さて、UG945チュートリアルでは、サンプルデザインに含まれる制約セットを使用せず、新に定義しなおす演習をするようになっています。演習はおおきく

-

- タイミング制約

- 物理制約

の2段階にわかれています。今回は前半のタイミング制約部分を「なぞって」みたいと思います。ただし、既に一度動作させているプロジェクトを再度開いているので「いろいろ残っている」ものがあるみたい。CLEANにしてやってないので(残っている方が入力省けてお楽なのだよね)雰囲気だけね。

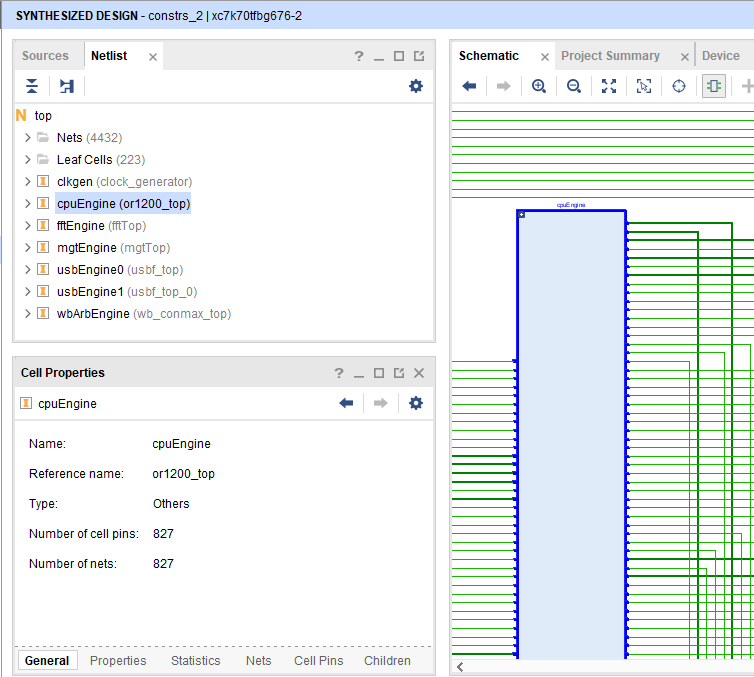

まずはプロジェクトを再度開いてネットリストを回路図表示しているところから。

AMD Vivado(TM) Timing Constraints ウィザード

さて、タイミング制約のXDCファイル(TCLコマンドをずらずらと並べたテキストファイル)を作るのに、手動で入力しても「原理的」には良いのだけれども、空のファイルを出発点にするのはとても辛そうです。そのため、この目的にも「ウイザード」が用意されとります。魔法使いの召喚は以下のとおり。

-

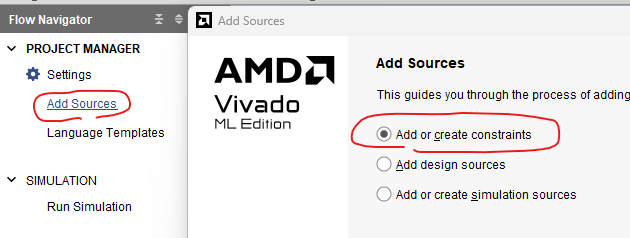

- フツーにconstraintsのAddを始める。

-

- まずはconstraintsファイルどもを入れる Constraint Set というもの(複数作成すること可。どれか一つをActiveとする)を新設。お名前もつけときます。

-

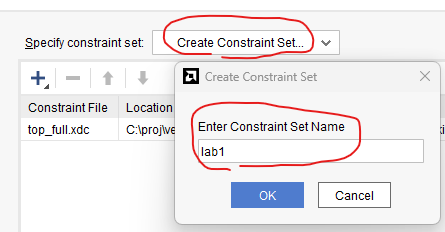

- Flow Navigatorの以下のところからConstraints Wizard発動

上記の魔法使いは、「合成済デザインのネットリストを解析」し、不足している制約を自動検出してくれるみたいです。その指摘に従って、クリクリやって(具体的な数字を入力もする)いけば制約が生成されるみたいです。

さすがに多数項目あり、その度にウインドウが出てくるのですが、大雑把に言うと以下の3カテゴリになるみたいです。

-

- Clocks、タイミングの基準となるクロックについての制約を入力

- Ports、入出力端子のセットアップ、ホールド時間などの制約を入力

- Clock Domain、ざっくりそれ以外のメンドクセー奴らを制約

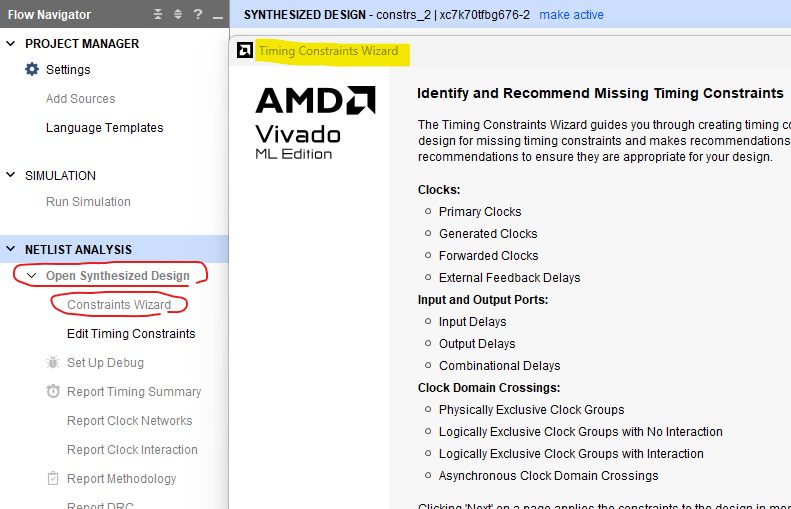

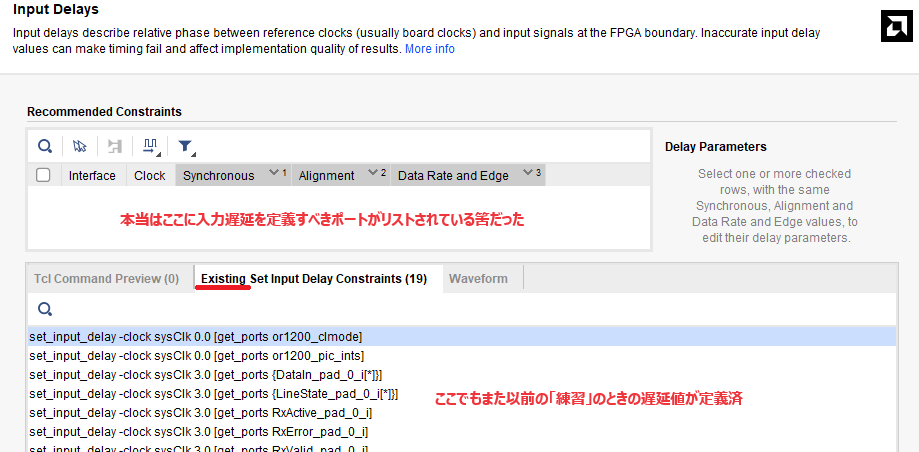

本当は、Reccommended Constraints欄に自動検出された信号名がズラズラと列挙され、それに対して周期など入力できるようになっている筈が、既に1度動かしているためか、メモリ上には「Existing」な制約(TCLコマンド)が存在してます。まあ、その値を入力した「テイ」にて次へNext

これまた既にメモリ上にExistingなので、入力した「テイ」にて次へNext

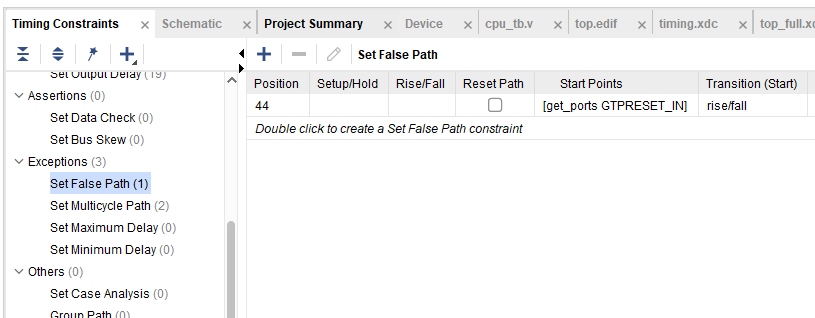

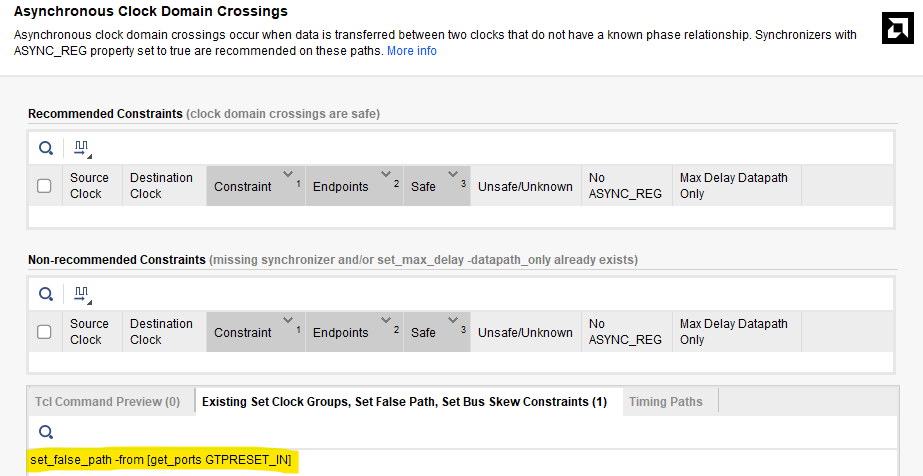

当然、出力端子などの設定ウインドウが次々と現れてまいります。すべて入力した「テイ」にて次へNextしていくと以下のところでチュートリアルでは不在な項目が現れました。

上記の false_path の設定は、このウイザード内ではなく、制約エディタのウインドウにて追加で手動設定すべき部分でした。過去回で既に実施済のプロジェクトだったのでメモリには存在しておったと。

制約エディタでコマケーところを手動設定

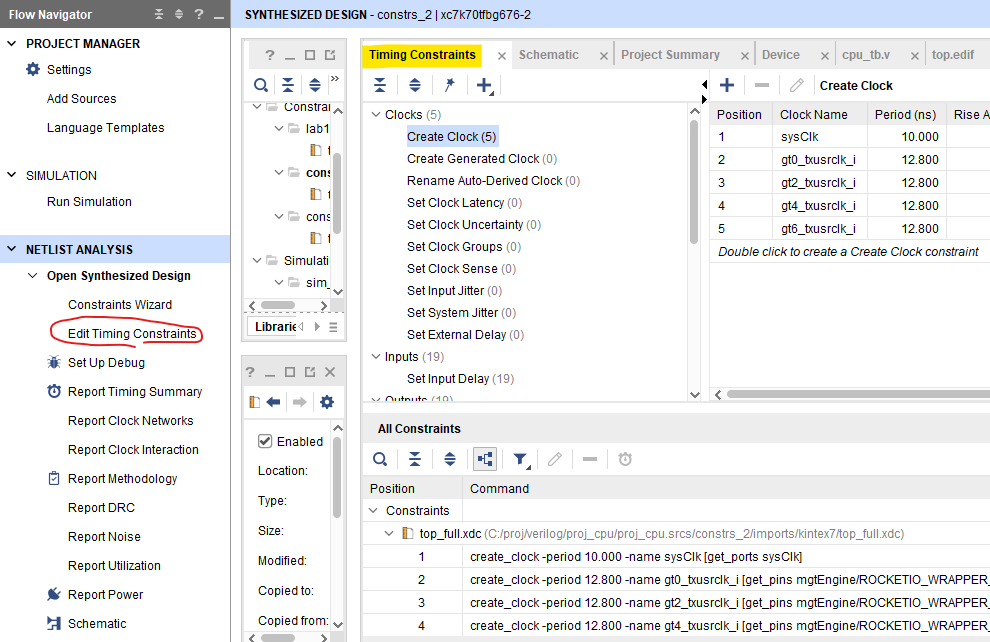

Costraints Wizardの下のEdit Timing Constraintsというところから、制約ファイルを開いてGUI使って編集することが可能です。

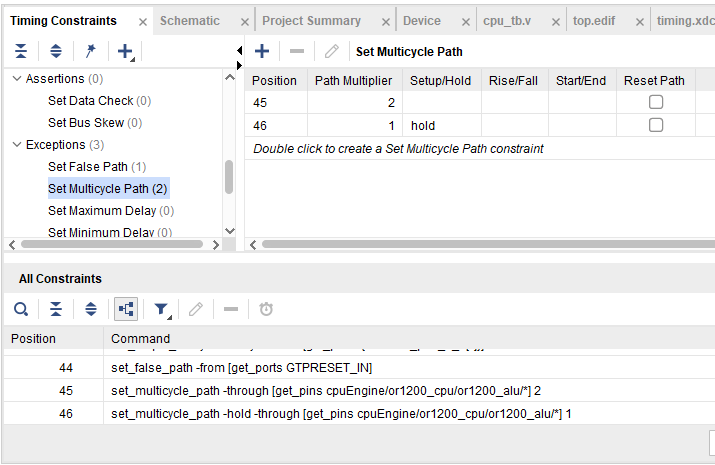

その次の Multicycle Pathの設定のところが以下に。

入力したタイミング制約の確認

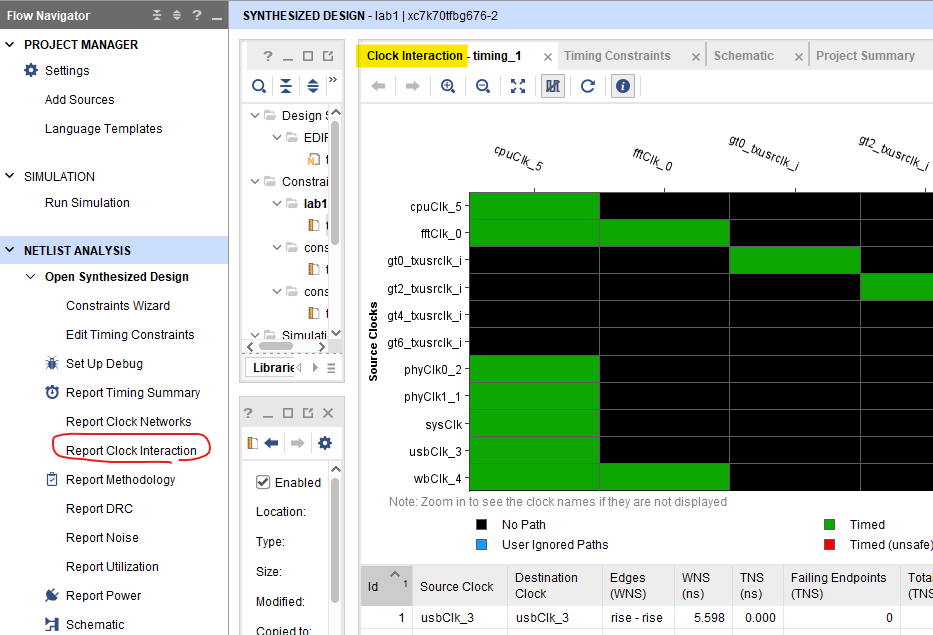

レポート機能を使って入力したタイミング制約の確認をとれます。まずは Report Clock Interactionから。緑の欄は「タイミングがOKという意味ではなく」、「タイミングを検証可能」ってことみたいです。

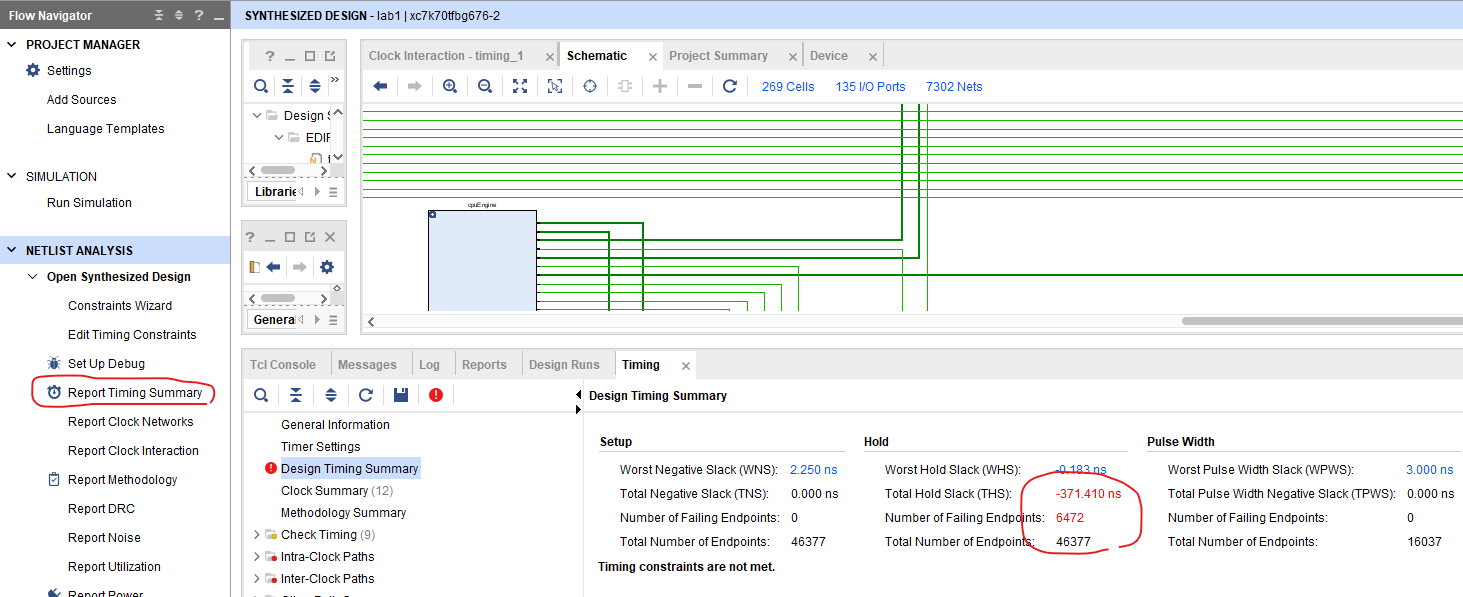

そしてサマリが以下に。Report Timing Summaryです。ちょいとフェイントなのが、上のReport Clock Interactionの結果は上のウインドウの中で賑々しいGUIのタブで現れるのに、Summaryは下のウインドウ中にひっそり文字表示されることです。こんな感じ。

上のウインドウばかり見ていて、ボタン押したのに「結果が見えない」と早合点したお惚け老人は焦りましたぞ。そして上の赤丸のところ、ホールドタイムが制約条件割れているみたいです。しかし、チュートルから一か所引用させていただきます。

フローのこの段階では多少のホールド違反が発生するのは普通で、配線段階で修正されます。

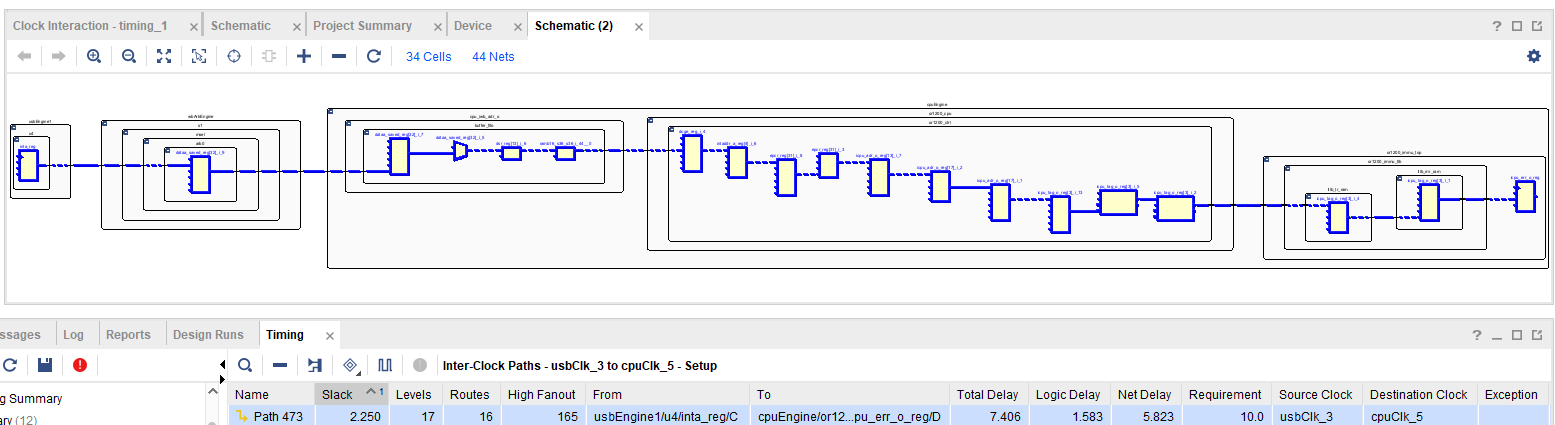

とのこと。ルーティングを待てということかい。なお、悪かったところ(ワースイトちょめちょめ)を一つ一つ取り出してその様子を観察することも出来るみたい。

いや~、ムツカシー設計だと、こういうところを「詰めてく」ところ根性要りそうな。お惚け老人には気力ないっす。次回は物理制約じゃな。