前回、RISC-V(MicroBlaze-V)コアのタイミングエラー問題が解決(よく分かってないけど)したみたい。そこで今回からコアの横に「自前の回路」を並べていきたいと思います。自前の回路はRTL(とりあえずVerilogね)記述としましたが、これをRISC-Vコアのお隣に置くのはどうしたらよかですか?やってみます。

※かえらざるMOS回路 投稿順 INDEX

※実習にはWindows11上の AMD社 (Xilinx) Vivado 2024.1 および Viris 2024.1 を使用させていただいております。

※ターゲットボードは、Digilent製 Cmod S7ボードです。お求めやすい? Spartan-7搭載の超小型開発ボードです。

自前のRTLコードをどこに置く?

過去回では、RISC-Vコアを含むブロックデザインの「ラッパ」のソースに手動で手を入れて自前のRTL記述を突っ込んだりしてました。それでも回路は構成可能ですが、自動生成されるラッパのソースに手をいれるので、以降のラッパの自動生成はできなくなるはず。あまり座りごごちの良いもんじゃござんせん。

どちらかと言えば、ブロックデザインの内部に「自前のブロック」を配置してその中に自前のRTLコードが入る形の方が良い感じです。さてこのようにするにはどしたら良いの?充実のXilinx社のドキュメントなので、探せばすぐにお答えが見つかります。日本語ドキュメントへのリンクが以下です。

Vivado Design Suite ユーザー ガイド: IP インテグレーターを使用した IP サブシステムの設計 (UG994)

上記の文書の中に、「ブロック デザインへの RTL モジュールの追加」について述べている部分があります。文書を読めば「簡単そう」ではあるのだけれども大丈夫か?

とりあえず組み込んでみる「自前の」RTLコード

なるべく簡単なもの、ということで用意したのが以下です。8ビットデータについて奇数パリティを計算するだけのもの。実質たったの1行、バリバリの組み合わせ回路っす。

module odd_parity(

input [7:0] DIN,

output ODD

);

assign ODD = ^DIN;

endmodule

一応論理シミュレーション(ビヘイビア)

既存のブロックデザインの横にRTLソースを並べておきました。普通にシミュレーションしようとするとブロックデザインの方がトップモジュールに見えてしまうので、以下のような小手先のインスタンス化で「今回着目の」パリティ生成回路の方が見やすくなるようにしてみました。シミュレーション用のテスト・ベンチのソースが以下に。

module odd_parity_tb(

);

reg clk;

reg rst;

reg [7:0] data_in;

wire parity;

odd_parity dut (

.DIN(data_in),

.ODD(parity)

);

mv5_CLK100_1_wrapper dut2 (

.reset(rst),

.sys_clock(clk)

);

always #5 clk = ~clk;

initial begin

clk = 0; rst = 0; data_in = 8'b00000000;

#10; data_in = 8'b00000001;

#10; data_in = 8'b00000101;

#10; data_in = 8'b11111110;

#10; data_in = 8'b11111111;

#10; data_in = 8'b01010010;

$finish;

end

endmodule

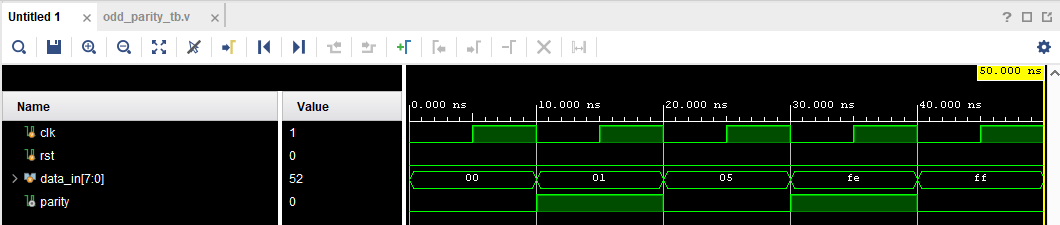

上記の手抜きなシミュレーションの結果が以下に。一応、入力値が奇数の時だけparity信号がハイになっているみたい。ここは予定通りっと。

自前の「RTLソース」をブロックデザインに取り込む

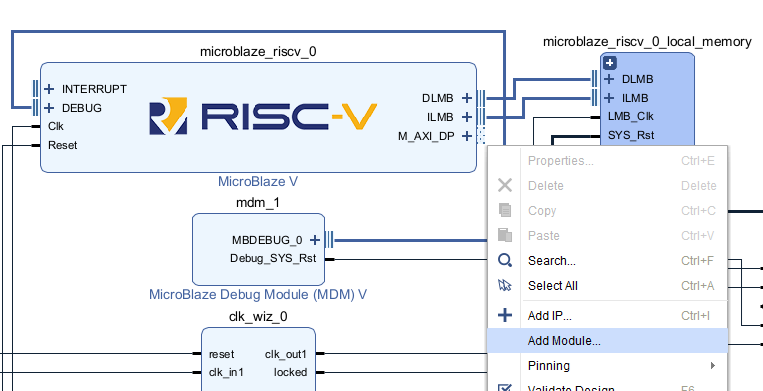

方法は簡単、まずはブロックデザインを開いて、どこか隙間で右クリックすると「いつもの」メニューがでてきます。各種のIPを配置するときは「Add IP」でしたがその下に「Add Module」というメニューあり。今回はそれです。

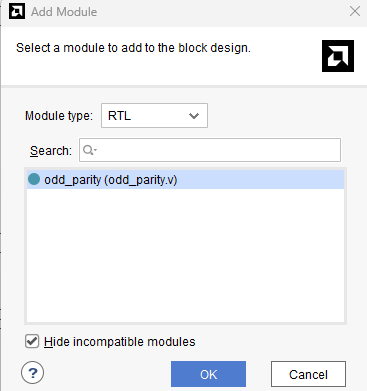

「Add Module」を押すと現れるウインドウが以下に。プロジェクト内に多数のRTLソースが定義されていれば、沢山リストされるのでしょうが、今回は一つしか作ってありませぬ。こんな感じね。

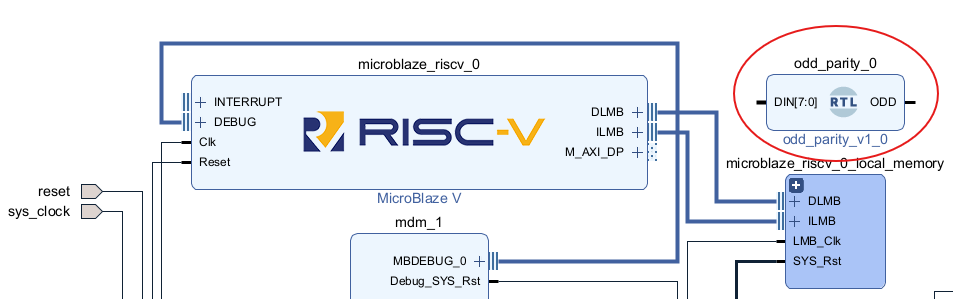

上記の odd_parity.v を選択してOKすれば、ほれこのように。

赤丸のところにodd_parity_0という「インスタンス」が現れました。その中央には燦然と「RTL」というマークが。やったね。簡単。

でもな~、このままじゃコアと接続する方法が。。。それはまた次回ってか。