中華FPGAの星?Anlogic社の廉価版FPGAの件、2回投稿したところで先が長くなりそうなので、シリーズ分けることにいたしました。まず、初回としては「極小の新規プロジェクト」をまっさらな状態から始めたいと思います。「極小のロジック」ということで信号反転、インバータ1個相当からであります。

まずは、本投稿に先行する2件へのリンクを貼っておきます。

部品屋根性(17) AN Logic、Tang Dynasty、Google翻訳に頼る

上の方はボードの導入編、ぶっちゃけ「ライセンスファイルを忘れずに」の回、下の方は、開発ツールである Tang Dynasty(唐王朝?)というソフトウエアのユーザーズマニュアル(簡体字中国語)、Google翻訳駆使すればOKの回でした。

今回から、実地に自分でプロジェクトを作成し、このFPGAにて何を今更ロジックを学んで行きたいと思います。初回の課題は、ぶっちゃけ、

インバータ1個相当

です。とりあえずこれが実装できれば、後は量が増えるだけだ(?)

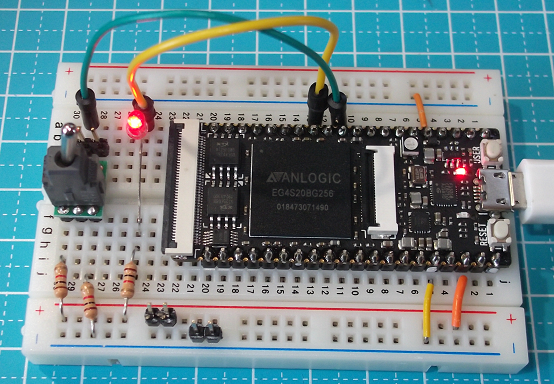

実際に外部回路を実装して確認するのは例によってブレッドボード使うのですが、その前に要確認事項がありました。Tang PRiMER(メーカの綴り)ボードの端子配列です。以下のSipeed社のページを見ると

NewとOldという2種類のボードのPinoutsが掲載されているのです。それも、

- Newの方は裏面

- Oldの方は表面

上下が入れ替わり対応関係がとりずらいですが端子配列異なります。決定的なのが新ではGNDになっているあたりが旧では入出力端子になっています。新旧取り違えるとヤバイ感じです。

手元のボードの裏面を見る限り、Newとして掲載されているボード裏面のシルク印刷とは明らかに異なります。するとOldの方なのかと思って裏面に印刷されている端子名をみると New と同様でした。中央の「商標」的なものに騙されてはいけないようです。端子名を確認すべしと。なお、以下にPIN配のシートがあるのですが「新」の配置でした。

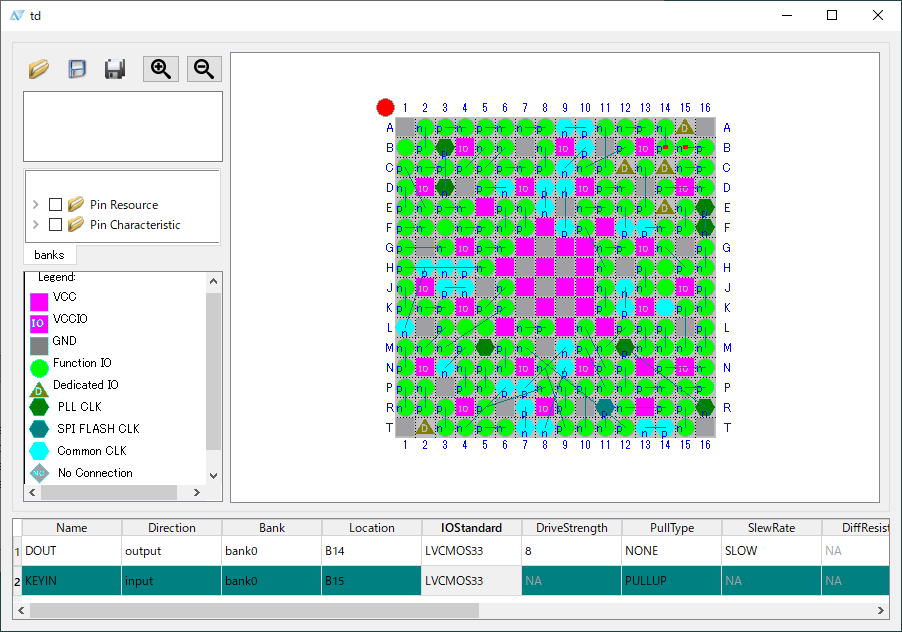

今回実装は、以下のようにいたしました。

- B15ピンを入力信号 KEYIN

- B14ピンを出力信号 DOUT

KEYINにスイッチを接続し、0/1入力すれば、DOUTに反転された信号が出るようにいたします。DOUTが0のときにLEDが光るように外部回路を作れば、KEYIN=1のときにLEDが輝き、KEYIN=0ときにLEDが消灯するという意図であります。超簡単。

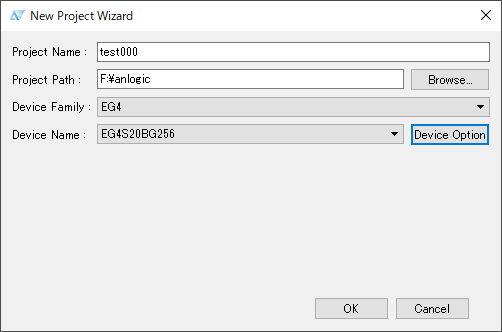

さて最初は、新規プロジェクトの作成です。Tang Dynasty(以下TDと略します)を起動、ProjectメニューからNew Projectを選べば以下のウインドウが開きます。ここに必要事項を書き込みます。

なお、Device Optionボタンを使用すると、デバイス毎に定義されている「キメウチ」の端子機能などを変更できるようですが、今回はそういうことはいたしませぬ。

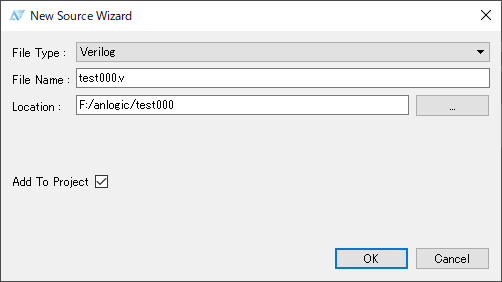

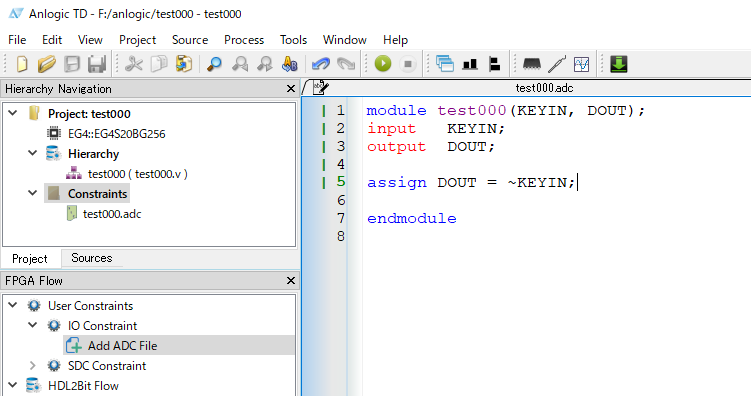

次は、実装するロジックをVerilog(またはVHDL)で書くなり既存ファイルを取り込むところ。今回は新規なので、SourceメニューからNew Sourceで作成しました。マニュアルにも書いてありますが、Add To Projectに忘れずにチェックを入れないとなりません(デフォルトではチエックされていない!)

今回はインバータ1個相当なので、assign文一つの極小ソースです。こんな感じ。

module test000(KEYIN, DOUT); input KEYIN; output DOUT; assign DOUT = ~KEYIN; endmodule

本来であれば、前回やったように、シミュレーションしてデバッグしてといった作業(外部ツールによる)があるのですが、今回はパス。

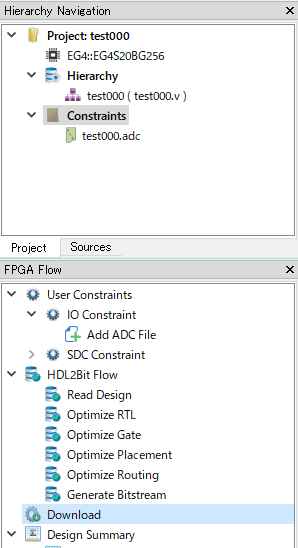

次にピンと信号の定義です。 “.adc”という拡張子のファイル(Anlogic Design Constraint)で定義するのですが、ファイルの作成の最初は、単なるテキストファイルとして作成するようです。FileメニューからNewしても良いし、外部のエディタで作ってもよいのだとおもいます。そして、.adcという拡張子でセーブしてから、以下のような感じで、Add ADC Fileして、作成したプロジェクトに取り込みました。

最初に .adcファイルを作成したときには、信号名とPINの対応関係を書き連ねただけなのですが、次にツールメニューから、IO Constraintツールを実行することで、諸設定が付加されます。こんな感じ。

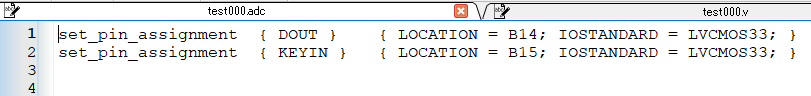

デフォルトがLVCMOS2.5Vになっていたので、今回は3.3Vに変更してみました。結局、上の画面で弄った結果は、先ほどのADCファイルに書き込まれるので、変更後のファイル内容は以下のようになりました。

結局、上のツールがつけ足してくれたのはIOSTANDARD=LVCMOS33の部分だけで、他は手動で書いた通りです。

ここまで書けば(といって何行も書いてませんが)、論理合成してビットストリームが作れるので、やってみます。前々回のように Run 一発ではなく、今回は、ビットストリームを作るためのフロー順に、マウスでクリクリやって各ステップを動かしてみました。

FPGA Flow面のHDL2Bit Flowの下の各ステップの頭のアイコンをクリクリしてやると、各ステップが実行されて、コンソール画面にいろいろメッセージが出力され、問題なければ緑のチェックマークがついて行きます。

インバータ1個なので、ほとんど待つ時間もなく、クリクリ>チェックOKという感じです。

実行後は、Design Summary配下の色々な情報も見れる筈ですが、インバータ1個です。今回はパス。

また、実際に合成語のゲートレベルの回路図やら、FPGA上の配置配線などもチェックできるツールが含まれていますが、これらも皆パス。

インバータ1個だし。

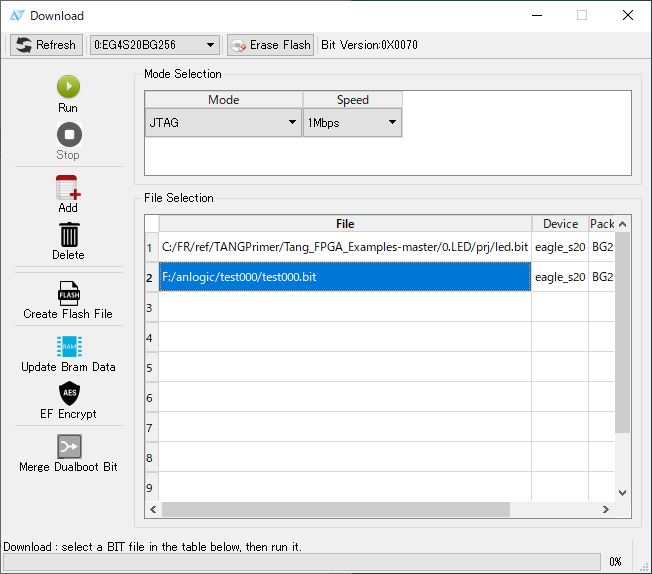

さてビットストリーム(TD的にはBit Flow?)も出来たので後は書き込むだけです。前々回、USBでボードを接続すれば認識されるようになっているので、ボードを接続してから、Downloadをクリクリやってウインドウを開きます。

イマイチだな、と思ったのが、作ったばかりの bit ファルがダウンローダーのFile Selectionには登録されていないことです。左側のAddボタンで、ファイル選択が必要です。Selectionに現れたらそれをクリックしてやると、Runボタンが使えるようになっているので、Runするとダウンロードされます。

ダウンロード成功すれば、インバータ1個、ちゃんと動いてました。アイキャッチ画像に掲げましたとおり、スイッチをハイ側に倒せばLEDが光り、ロウ側にすれば消灯。

また次回。