「アナデバ社(ADI社)のWeb記事『StudentZone』を初回からすべて読む」の2021年5月号の2回目です。前回、LTspiceのシミュレーションで「雰囲気」は分かった、ということで今回は実機で確認してみます。正直、既に分かった(どこまでわかってるんだか?)回路の動作を確認するだけ。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

毎度のお約束では、「確認するだけ」と言いつつ何か問題勃発し、その対処に翻弄されるのですが、今回は違います。極めて平板、盛り上がりもなし。まあ、敢えて問題勃発しそうなところを避けている形跡もあり、と。GWだし(そればかり理由にしてるな、自分。)

原理回路の動作確認

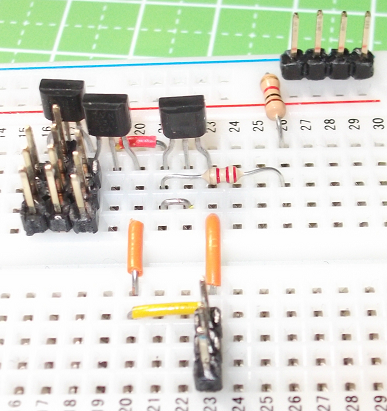

以下黄色C1が入力信号(前回のシミュレーションでは黄緑)、青色C2が出力信号(シミュレーションでも青)です。入力波形の条件は同じ、1V振幅、オフセット0V、1kHzの正弦波です。

「予定どおり」入力波形とほぼ同様な出力波形が得られており、Peak2Peakの測定値から判断するに、微妙に1より小さいゲインです。これまた予定どおり。唯一出力波形が現れる位置がシミュレーションより1V近くも低くなってます。本当はこの辺考察するべきなのだけれど、今回の「流す」方針にて見て見ぬふり。そんなんで学ぶと言えるのか、自分。

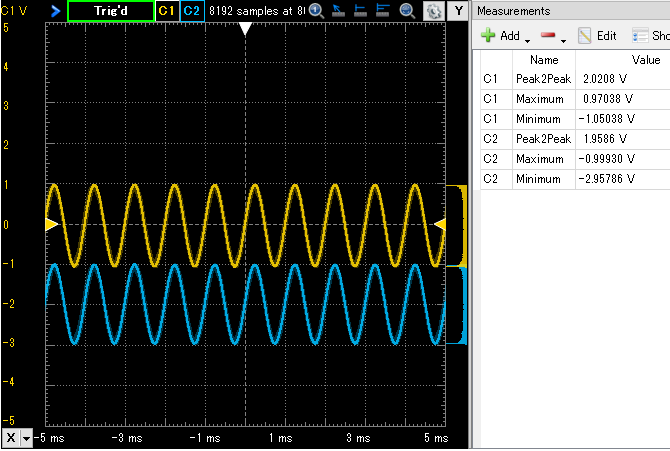

ま、肝心なところは、入出力の間の電位差がぶれている確認の方であります。CH2を出力信号の波形観察から、入出力間の電位差に変更してみたところがこちら。約65mVも「ぶらぶら」しております。シミュレーションでは赤の波形で見ていたところ。

改良型のソースフォロワ回路

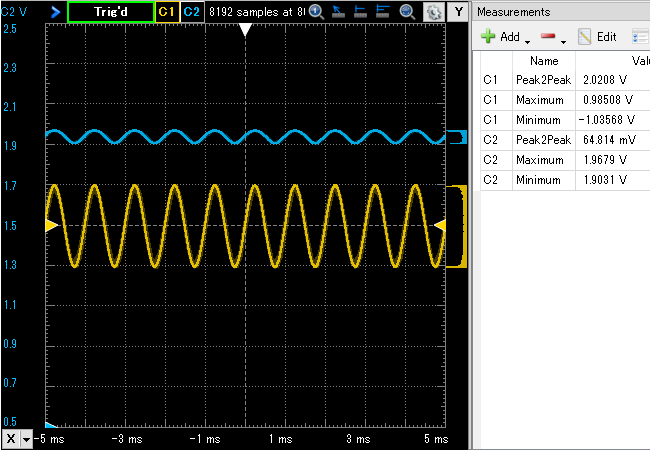

さて改良型のソースフォロワ回路の観察が以下に。シミュレーションとの相違点が1点あり、

カレントミラー部分に使っているMOSFET2個はZVN3310

です。シミュレーションでは、全部ZVN2110Aでしたが、前にも述べたとおりアナデバ製学習部品キットADALP2000にZVN2110Aは1個しか入ってません。同じNMOS-FETが2個入っているのはZVN3110なので、そちらで代用しました。

改良型だけあって、ゲインは限りなく1に近づいている感じ。

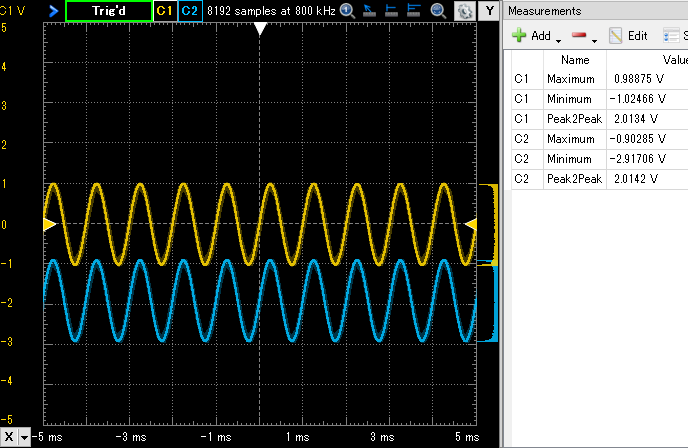

さて入出力間の電位差の「ブレ」の方が以下に。上の原理回路の測定では縦方向は200mV目盛りとしていましたが、こちらでは20mVとしています。それでも波形の変動はわずか。3mVほど(原理回路は65mVでした)にとどまっています。

予定どおりカレントミラー回路の効果が発揮されました。

無理に作った平穏無事感だが。次回はもすこしガチで行きたいデス。