前回、入力信号が3V振幅ならば、綺麗に線形な結果が得られる筈のXYグラフが折れ曲がっておりました。何故に?そこでちょっと実機回路を勝手改変して「線形な結果」が得られるようにしてみました。得られたのは良いけれども、なぜSPICEの結果と実機の結果がこうも違うのか?SPICEあるある?SPICEの闇?違うか。

※「お手軽ツールで今更学ぶアナログ」投稿順 indexはこちら

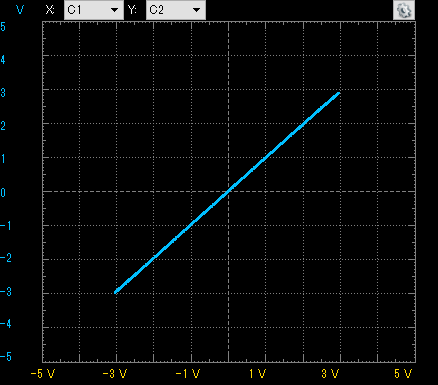

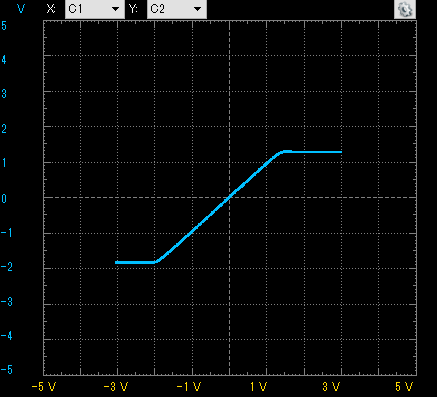

まず、前回の「折れ曲がった」XYグラフを再掲載させていただきます。期待としては、冒頭のアイキャッチ画像に掲げたように、-3Vから原点とおって+3Vまで一直線と行きたいところですが上下が平。上がりきらない、下がりきらない。

ただ胸に手を当てて振り返るに、ちょっとヤマシイところがあり。

-

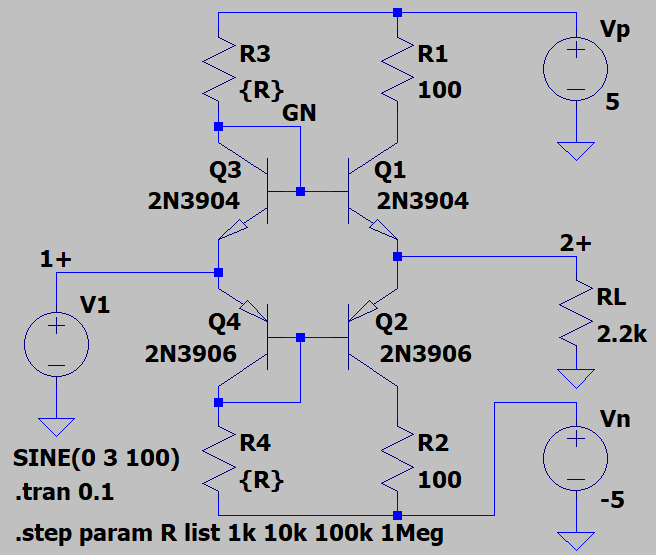

- アナデバ様の記事ではNPNはSSM2212、PNPはSSM2220(どちらもワンパッケージに2トランジスタ入ったVBEマッチしていると思われるペアトランジスタ品)を使えという御指定にもかかわらず、ディスクリート単体の2N3904(NPN)、2N3906(PNP)で実機回路を組んでおります。

- さらに言えば、各ペアはVBEのそろったものを使えとのことですが、特にデバイスのスクリーニングなどしておらず、成り行き、部品箱から取り出した順で使ってます。

でもねえ、多少バラツいていてもそこまで影響ある?と思ったんであります。どうなんだろ。

意図通りの「線形なXYグラフ」にするのに直ぐに思いついたのは、以下LTspice用回路図のR3およびR4の抵抗値を「少し」小さくしてみるという「対処療法」です。以下図でGNと書いたQ3、Q1のゲートのところの電圧が上がらないので出力が頭うちになるんであろうと(逆にQ2、Q4の電圧が下がらないので出力も下がりきらないのであろうと)

アナデバ様のオリジナルの回路図では、上記回路図のR3、R4(アナデバ様のオリジナル回路図ではR1、R2です)は10kΩですが、今回エイヤーで両方とも1kΩとしてみました。

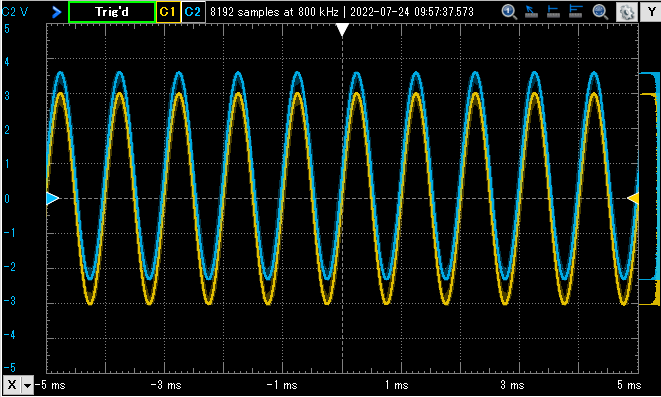

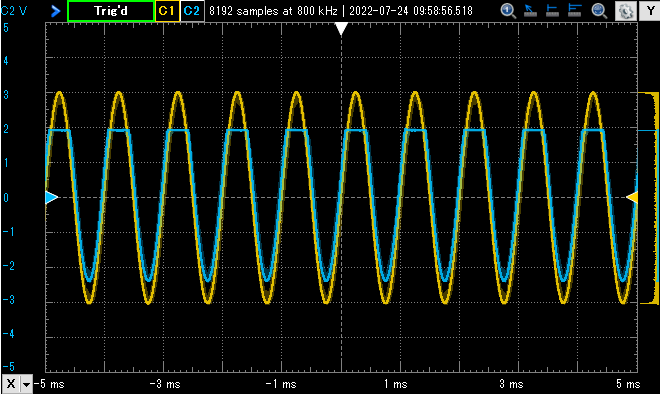

以下は1kΩにしたときの実機上での入力信号C1(黄色)と、GNの電位C2(青色)です。青色は黄色よりダイオードの電圧降下分だけ高い電圧にいると。予定どおりでないかい。

このときのXYグラフを観察すると以下です。原点とおってプラマイ3V範囲で一直線。これだね、見たかったのは。

なにも考えない対処療法にて問題は表面的には解決。

なお、抵抗値を10kΩに戻して実機上でGNの波形(以下の青色)みると、「ちゃんと」頭打ちになっておりますぞ。

LTspiceでは

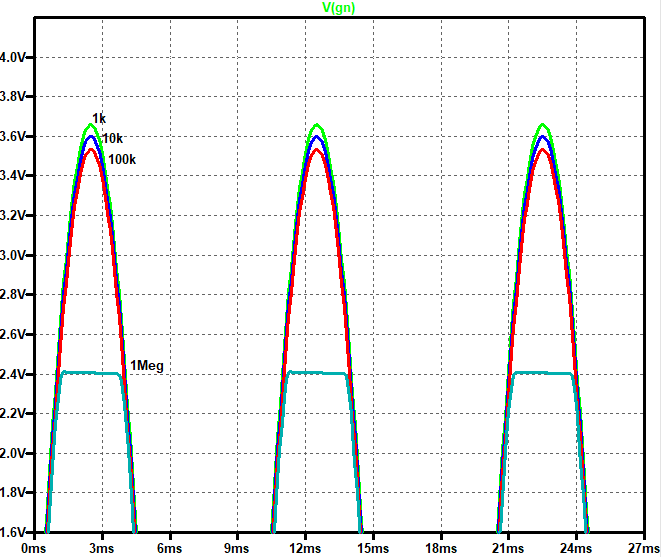

前回も書いたとおり、LTspice上では抵抗値10kΩのときもOKな波形だったのです。さきほどのLTspice用の回路図を見ていただければお気づきのとおり、今回、抵抗値をパラメータ化して.STEP実行できるようにしてあります。シミュレーションしてGNノードのグラフの一部を拡大したものが以下に。

上記のように、10kどころか100kにしたって、1kのときとそれほど変わらないのです、流石に1MΩとするとまさに実機で(10kΩ)のときと似た波形が得られます。

SPICEの結果と実機の結果の違いを考察せよ、という感じですかね。アナログ分かっている人には何のこともないのだろうけれど、アナログ素人はSPICEの闇というか、SPICEの沼というかにハマるのが恐ろしげです。そのうちやらないとね。そのうちって何時だ?