別シリーズにて30年前のSPICEのマクロモデル/ビヘイビアモデル作成の教科書を発掘。これを手がかりにSPICEのマクロモデル作成への進出をたくらみました。アナログ素人のクセに。でも今時テキストベースのモデルでもなし、だいたいLTspiceで階層設計ってどうやるのだっけ?そんなことも知らないでよくやる気になったな自分。

※「SPICEの小瓶」投稿順インデックスはこちら

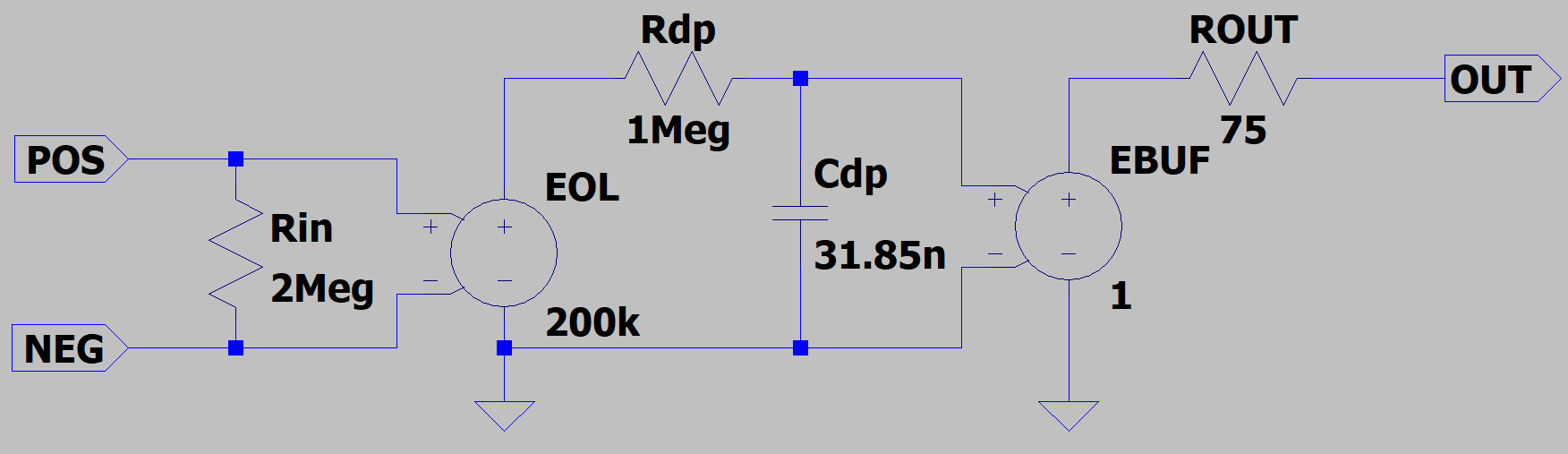

教科書図1.1のOPアンプのマクロモデル

教科書は30年前の御本なので、SPICEの回路記述はテキストベースです。0はグラウンド、その他のノードは、1,2,3と数字で記述、MOSFETはMで始まるし、抵抗はRで始まる。忘却力の年寄も遥かな太古の時代に覚えたことは忘れておらぬのです。

しかし、このご時世、SPICEシミュレータも多くは回路図入力が主体です。衣の下にテキストベースのSPICEネットリストは隠されております(ときどき見えるけれども。)

近代的なLTspiceも例外ではありません。マクロモデルを作るのにも回路図入力可能であります。今回は発掘した教科書「J.A.コネリー/P. チェイ著、青木訳『SPICEによる回路設計(ディスク付)』トッパン, 1994」の図1.1のOPアンプのマクロモデル(テキスト)をそのままLTspiceの回路図ベースに落とし込んでみました。これが動けば、後はマクロモデルを作り放題。ホントか。ちなみに付属のディスク、3.5inch 2HDの昔はよく見かけたアレですが、現在手元にはこれを読めるマシンがございません。残念。

テキストを回路に置き換えたものが以下に。マクロにつけられたお名前から察するに、当時既に古典のオペアンプであったuA741のマクロモデル(真偽はしらず)ではないかと思われます。

LTspiceの階層化については多数の解説ページが存在しますが、今回は横浜のマクニカ殿の以下のページを参照させていただきました。あざーす。

上記の回路など描ければその階層化など「一撃」であったのです。が、実は一回失敗してます。

LTspiceの階層化、端子の属性必須

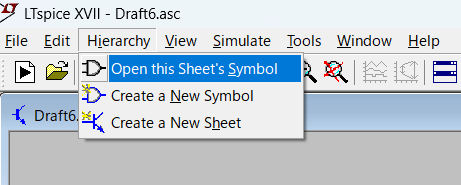

LTspiceの場合階層化自体はメニューから一撃でできます。こんな感じ。

回路図を描いておいて、上記のメニューを選択します。すると以下のような確認ウインドウが現れます。これに「はい」と答えれば生成されるはず。

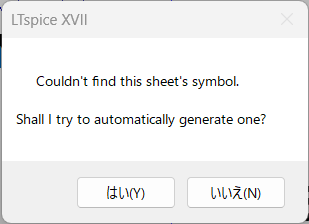

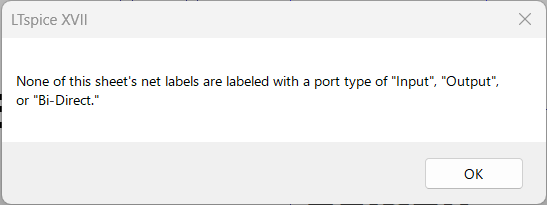

しかし「はい」しても、初回はこんな感じ、そうは問屋が卸してくれません。

しかし「はい」しても、初回はこんな感じ、そうは問屋が卸してくれません。

いつもLTspiceのネットにラベルを付加するときは、none属性にしてます。まあ階層構造の無いSPICEシミュレーションで、内部ノードがインだのアウトだの言ってもしかたがないので。上記の回路のラベルも最初はnoneにしてました。しかし上記をみるとnoneはゆるされず、Input、 Output、 Bi-Directとちゃんと属性を付加しておかないと階層設計にはしてくれないようです。

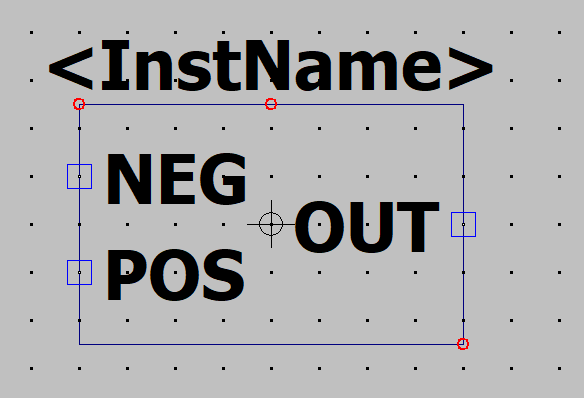

慌てて回路図ラベルに属性をつけました。これでOK。以下のようなシンボルが生成されております。

勿論、シンボルエディタを使えば素っ気ない四角いシンボルでなく、カッコイイシンボルにすることもできます。メンドウなのは嫌いなので四角のままでいきまっす。

それより大事なのは、最初に作成したマクロモデルの回路図(.asc)や、作成したシンボル(.asy)の格納場所です。セーブするときに所望の場所に格納しておかないと混乱のもとかと。

作ったマクロモデルを使ってみる

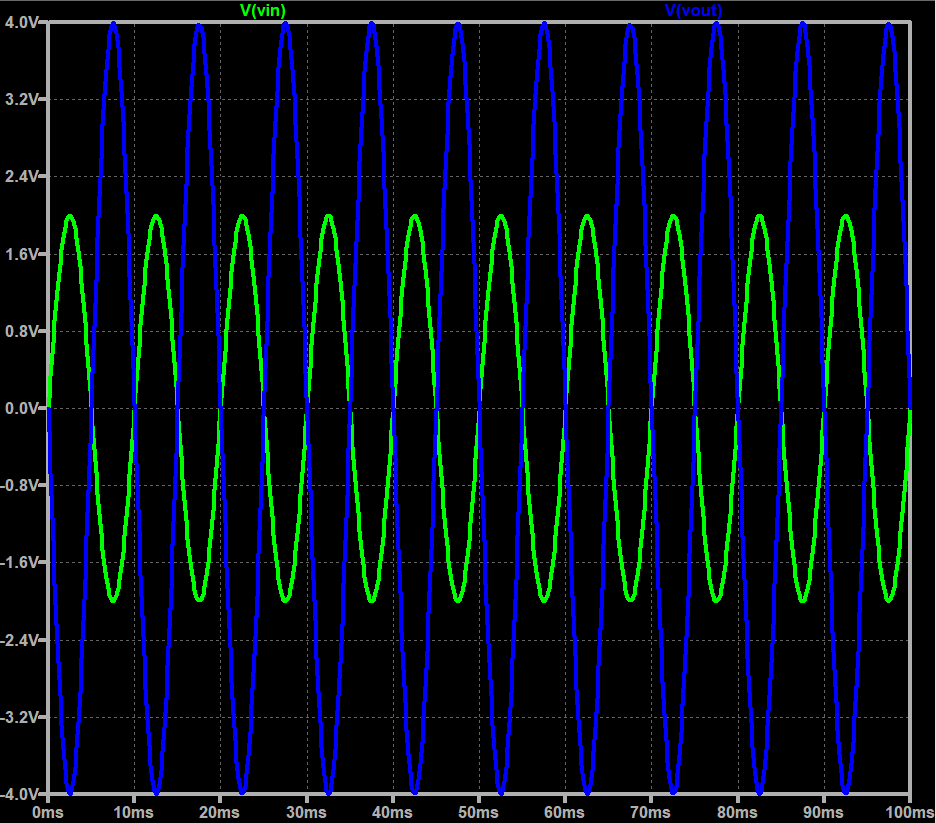

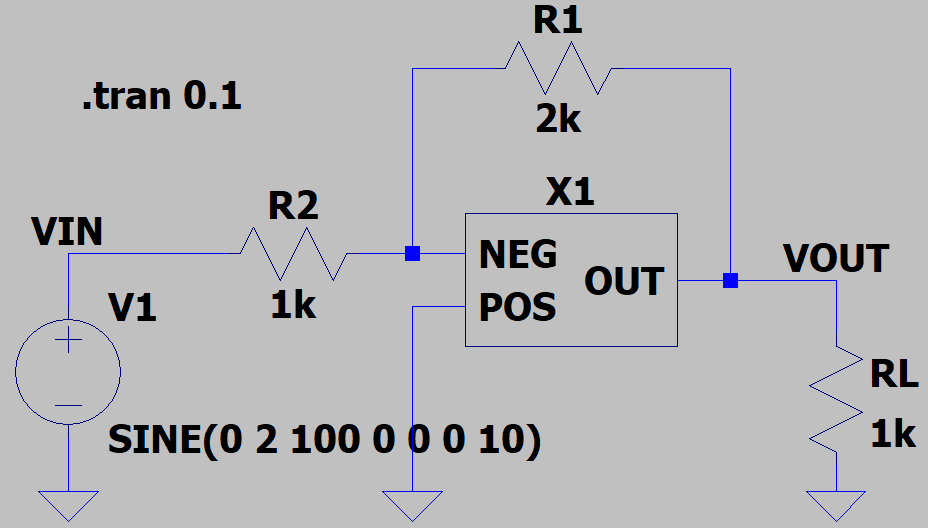

普通に新規の回路図画面を開き、「所望の場所」にセーブしたマクロモデルのシンボルを選択すれば、今まで通りに回路の作成が可能です。今回はこんな感じにしてみました。2倍の反転増幅器であります。ありがち。

おお、それらしく動いているじゃあ~りませんか。

次回から調子こいてマクロモデルの作成か?