前回は複数の外部入力端子を組み合わせて割り込みをかけることもできるIOC機能でした。今回は複数の外部入力端子を含む各種信号を使ってロジックを作り、結果を外部出力したり内部回路で使ったりできるCIC機能を使ってみます。FPGAとはいかないですが、ごく小さなPLDみたいな感じ。外付けロジックIC数個分くらいの規模感。

※今回もターゲット・マイコンは、PIC16F18855 です。例によってMPLAB X IDEを起動しマイコン機種を選択した後、MCC Classicを使ってプロジェクトをコンフィギュレーションしております。

Configurable Logic Cell(CLC)

マイコンチップ上に小規模ながらも「コンフィギャラブル」な論理回路を集積するというのはツボにハマるととても有効なのではないかと思います。ちょっと信号のANDとりて~というくらいでロジックIC1個載せるのにもコストがかかります。それに小型化している基板へのインパクトも馬鹿になりません。かといって「お高い」FPGAを載せるような用途でもなし、「お求めやすい」マイコンにそういう機能が入っていたら使いたくなるのでは?

こうしてMicroChip社がCLCと呼ぶ機能をPICマイコンに搭載してます。他社マイコンでも、PSoCマイコンは同様なロジック回路を搭載してた筈(アナログ・コンフィギャラブルが売りですがロジックも搭載。)

さて今回のターゲットのPIC16F18855には、CLC1からCLC4とよぶ4個の回路が搭載されています。各CLCは基本4入力1出力の「ロジックセル」です。単純な組み合わせ回路としても使えるし、フリップ・フロップ含む順序回路を構成することも可能です。

入力としては、外部GPIO端子以外に内蔵周辺回路類の各種出力信号/一部レジスタビットと組み合わせることが可能です。選択の範囲が広いです。また、出力信号は、外部GPIO端子に出力することが可能な他に、割り込みに接続したり、一部内蔵ペリフェラルの入力に使うことも可能。至れり尽くせりだな、おい。

MCC Classic 使用のコンフィギュレーション

さて、いつものようにMPLAB X IDE上でPIC16F18855用に新規プロジェクトを作成した後、MCC Classicを使って、ソースコードを自動生成していきます。

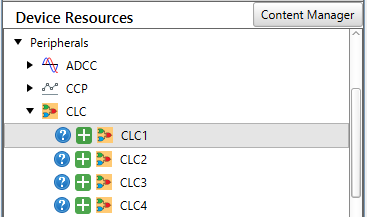

今回使用するCLC機能は、前回のIOC機能のようにデフォで使えるようになっている、という機能ではないです。以下のDevice Resourcesウインドウから「+」ボタンを押してプロジェクトのリソースとして取り込まねば使えません。

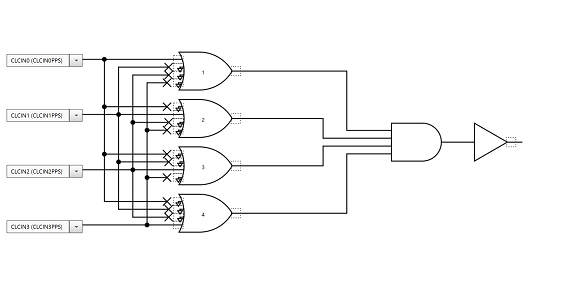

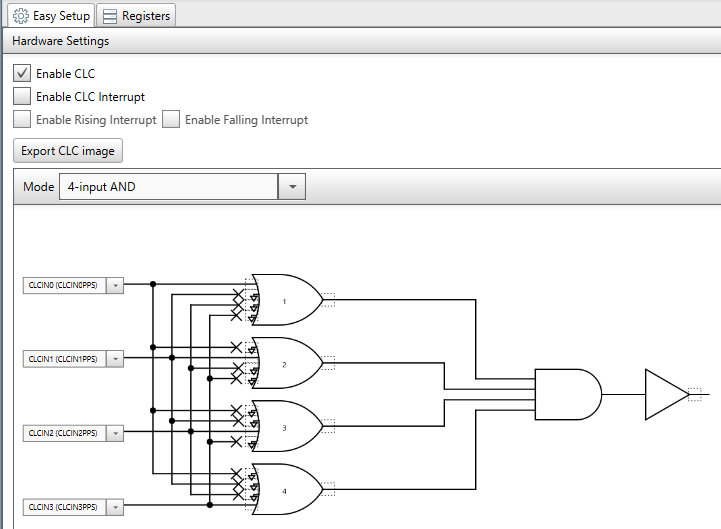

上記からCLC1を取り込んでみると、さっそくコンフィギュレーション用の設定画面にロジック回路図が現れます。以下のような感じ。

上記のSettingsでは、デフォルトでCLCはイネーブルにチェック入ってます(使うと宣言しているのであたりまえか。)CLC割り込みにはチェック入ってません。

-

- Modeという欄で今回は「4-input AND」を選択しています。ここのモードを変更すると表示されるロジック回路図も変化します。

- ロジック回路図の入力信号に接続されているプルダウンメニューで、入力をどこに接続するのか選択できます。上記ではすべて外部入力端子接続を選択してますが、内蔵ペリフェラルの出力信号なども多数接続可能です。

- ちょっと見ずらいですが、点線で描かれている小さな四角をクリックすることで配線を接続したり、反転(〇が表示される)させることができます。上記では初段の4入力ORのところにそれぞれ1本の外部信号のみ接続し、論理反転は使用しないように設定してます。

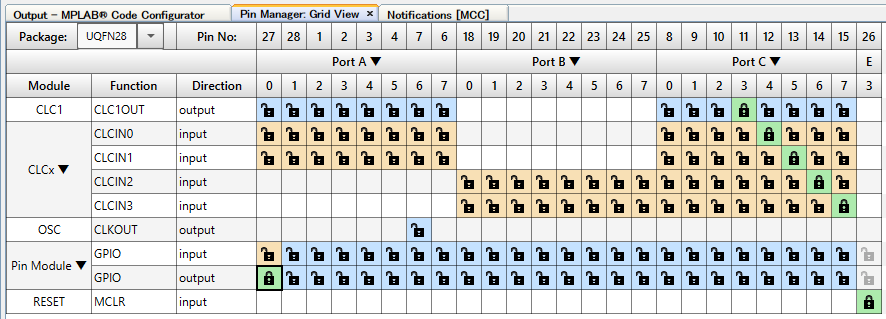

上記でロジックを構成した後、外部GPIO端子に信号を接続する場合は、Pin Managerから接続を指示します。

今回は、PC3端子にCLC1の出力を接続、PC4からPC7までの端子をCLC1の入力信号として使っています。

なお、PA0端子をGPIO出力端子に設定しているのは、「いつものLチカ」をCLC1の動作とパラで行わせるためです。

動作の様子

上記の設定後、MCCの「Generate」ボタンを押してソースコードセットを生成しました。自動生成のソースに手を加えたのは、main()関数のループに「いつものLチカ」コードを追加したところだけです。これでCIC1の動作にかかわらず、オンボードのLEDが点滅するというもの。

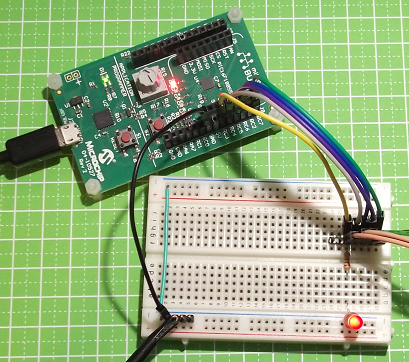

ビルドしてFlashに書き込み後の様子が以下に。CIC1の出力端子PC3には外付けLEDを1kΩの電流制限抵抗介して接続してあります。ちょっと頼りなげな光り方なのは駆動パターンによりデューティ16分の1動作しているため。

CIC1のロジックを駆動し、その動作を観察するためにAnalog Discovery2のロジック・パターン・ジェネレータ機能とロジアナ機能を使用しました。接続はこんな感じ。

-

- RC7、AD2のDIO3端子に接続、パターンジェネレータ生成の論理値入力

- RC6、AD2のDIO2端子に接続、パターンジェネレータ生成の論理値入力

- RC5、AD2のDIO1端子に接続、パターンジェネレータ生成の論理値入力

- RC4、AD2のDIO0端子に接続、パターンジェネレータ生成の論理値入力

- RC3、AD2のDIO4端子に接続、ロジアナ機能で観察

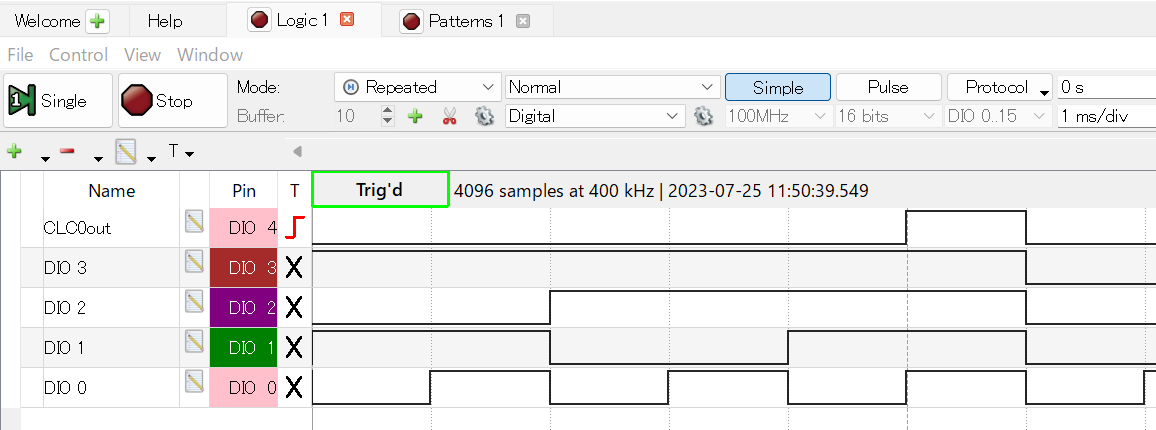

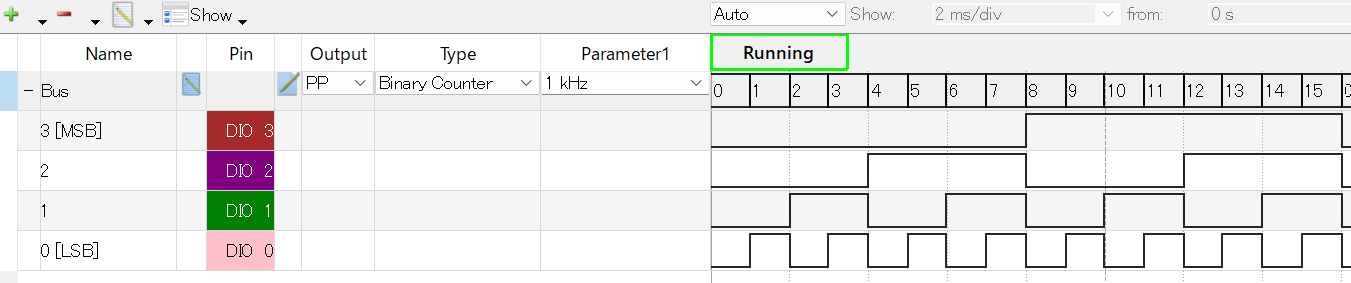

ロジックパターンジェネレータで生成したパターンの様子が以下に。

4本の入力端子が、オールハイになっているところで出力端子がハイとなっていることが分かります。あたりまえか。